从头学起Verilog(三):Verilog逻辑设计

引言

经过了组合逻辑和时序逻辑的复习,终于到了Verilog部分。这里主要介绍Verilog一些基础内容,包括结构化模型、TestBench编写和仿真、真值表模型。

这部分内容不多,也都十分基础,大家可以看个乐呵,看个意思,但是有一些细节还是需要注意的。

Verilog结构化模型

结构化和语言规则

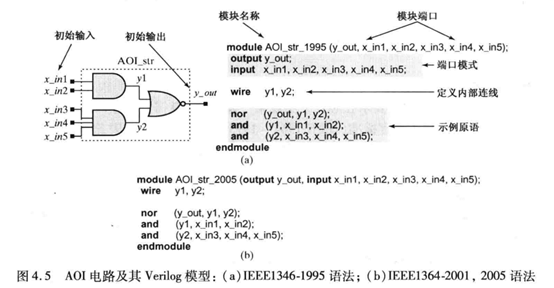

下图以示例的形式分别说明了1995版和2001/2005版Verilog语法下的结构化模型,两者的不同主要体现在模块输入输出端口的声明中。端口可以是input、output,也可以是inout双向端口(可用用于存储器与总线直接的数据传输)。

Verilog大小写敏感,名称可以包含字母、数字、下划线和$,变量名第一个字符不可以是数字或$。

四值逻辑:0,1,x,z,x表示未知(wire被相反逻辑所驱动),z表示高阻(连接线不与驱动相连接)。

除endmodule外,Verilog的每个表述文本都要以";"结束(与各种软件编程语言类似)。

注释可以用"//"单行注释,也可以用"/* */"范围注释。

矢量Sum[3:0]指四位位宽,左侧高位,右侧低位。若一个八位变量t[7:0],存储4,则t[2]对应1,t[3:0]是4,t[3:1]是2。

线网用于结构间的连接,wire类型,默认,输入即变化,不需要触发。

reg需要有触发,否则保持值,需要过程赋值语句(always,initial)触发,即只能这过程赋值语句中触发。

= 阻塞赋值 <=非阻塞赋值

定长数:默认十进制 8'b0001_0001 表示8位二进制数,存储值为00010001,_便于增加可读性。

自顶向下的设计(电路较大的时候十分有必要)

架构:一个设计的高层次的划分和组织结构。

将一个复杂系统划分为多个易于处理和实现的功能单元来设计,划分后的各单元模块设计更容易、测试更简单。

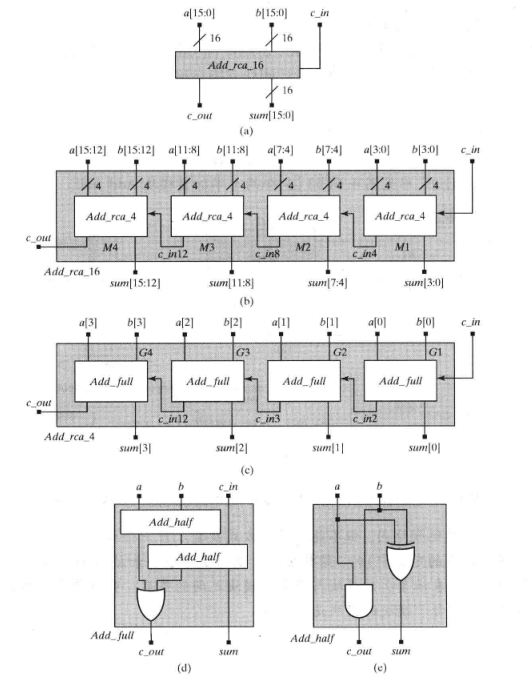

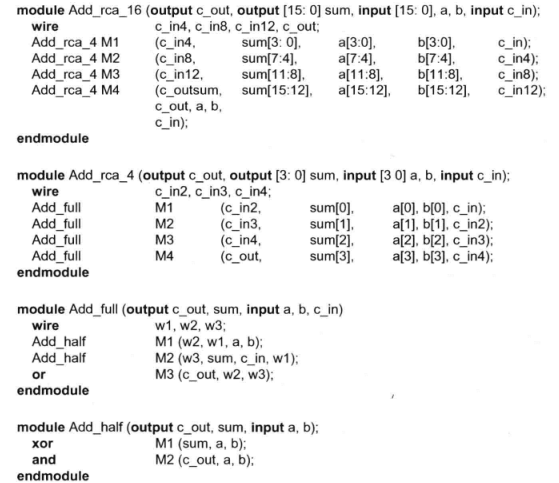

如图,一个16位全加器可以被分解为4个4位全加器,4位全加器可以被分解为4个全加器,全加器可以被分解为两个半加器。通过模块嵌套可以清楚地实现。

实现代码如下:

TestBench编写和仿真

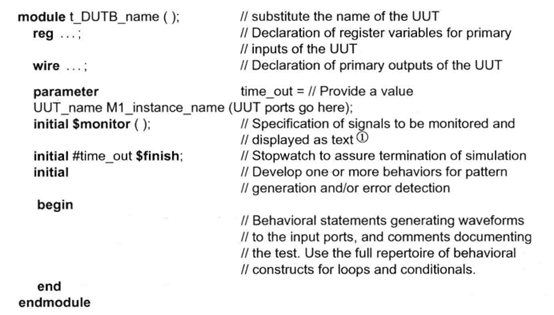

这里首先给出一个testbench的模版。一个模块完成后,需要编写对应的TestBench文件以测试该模块的功能。TestBench是一个额外的文件。

在文件开始,一般需要使用 `include "XX.v" 包含要测试的模块;一般使用 `timescale 1ns/1ps 来定义时延单位和时延精度(注意,这里的"`"不是单引号,是ESC下面的那个符号),时间单位和时间精度只能是1、10和100这三种整数,单位有s、ms、us、ns、ps和fs,时延单位必须要大于时延精度。

reg型变量一般作为模块的输入变量,信号发生,通过在过程赋值语句中改变输入变量值的不同组合,观察输出信号是否符合预期。初始值为x。

wire型变量一般作为模块的输出变量,可以随输出即刻变化。初始值为z。

# 延迟值 表示延时多少延迟单位。

延时

传播延时

Verilog中所有基本门和线网都有一个默认的零传播延时。

延时可以通过“# 延迟时间”的形式实现仿真。将“#1”插入到每个门例化名的前面。

惯性延时

每个传导线路都有电容性和电阻性,电荷无法一瞬间积累或消散。

Verilog把一个门的传播延时作为可以影响输出对应输入脉冲最小宽度(即输入脉冲宽度要大于等于门的传播延时才会影响输出)

传输延时

即传输线上延时可通过:

wire #2 A_long_wire 进行模拟

真值表模型(UDP)

用真值表直接表示逻辑功能。一位标量输出。

不匹配自动赋值x,z输入处理为x,?可以表示任意。

组合逻辑

格式

primitive 模块名(output a,input b,c);

table

//b&c=a

0 0 : 0;

0 1 : 0;

1 0 : 0;

1 1 : 1;

endtable

endprimitive

时序逻辑

格式1:

// enable data : state : next_state/out

1 1 : ? 1

即在enable=1、data=1、state任意条件下,输出next_state为1(必须为reg类型)。

格式2:

// clk data : state : next_state/out

(10) 0 : ? : 0

即在下降沿,输入data=0,state为任意状态条件下,输出为1。

总结

本文针对Verilog中的基础内容进行了总结,主要是复习和回顾。需要额外关心的地方已经加粗标出。如果有什么不足希望大家能够指出,共同学习。

从头学起Verilog(三):Verilog逻辑设计的更多相关文章

- 从头学起Verilog(一):组合逻辑基础与回顾

引言 该部分主要回顾了本科时数字电路中组合逻辑电路部分,内容相对简单和基础. 内容主要包括:布尔代数相关知识,卡诺图,最大项与最小项,竞争和冒险以及一些常见模块 数字电路中的逻辑 组合逻辑:输出可以表 ...

- 基于Verilog HDL整数乘法器设计与仿真验证

基于Verilog HDL整数乘法器设计与仿真验证 1.预备知识 整数分为短整数,中整数,长整数,本文只涉及到短整数.短整数:占用一个字节空间,8位,其中最高位为符号位(最高位为1表示为负数,最高位为 ...

- Actor:人生如戏全靠演技--“三维度”逻辑编程语言的设计(3)

在上一篇介绍了逻辑编程的作用,介绍了逻辑编程中的一些概念,包括逻辑程序的结构:事实.规则和问题:知识的表达方式:谓词演算.产生式规则,以及这些概念与三维度(角色+场景+时间)理论的契合关系,正式提出了 ...

- Linux 从头学 01:CPU 是如何执行一条指令的?

作 者:道哥,10+年的嵌入式开发老兵. 公众号:[IOT物联网小镇],专注于:C/C++.Linux操作系统.应用程序设计.物联网.单片机和嵌入式开发等领域. 公众号回复[书籍],获取 Linux. ...

- 数据库设计理论与实践·<二>概念设计与逻辑设计

2一.概念设计 1.1 概念设计关键知识 1.2 辨析 实体与属性的区别: ①实体能进一步用多个属性来描述,属性却不能,属性是不可再细分/分割的原子项. ②实体内部或者多个实体之间存在联系,而属性无. ...

- Linux从头学06:16张结构图,彻底理解【代码重定位】的底层原理

作 者:道哥,10+年的嵌入式开发老兵. 公众号:[IOT物联网小镇],专注于:C/C++.Linux操作系统.应用程序设计.物联网.单片机和嵌入式开发等领域. 公众号回复[书籍],获取 Linux. ...

- Linux从头学07:中断那么重要,它的本质到底是什么?

作 者:道哥,10+年的嵌入式开发老兵. 公众号:[IOT物联网小镇],专注于:C/C++.Linux操作系统.应用程序设计.物联网.单片机和嵌入式开发等领域. 公众号回复[书籍],获取 Linux. ...

- 跟vczh看实例学编译原理——三:Tinymoe与无歧义语法分析

文章中引用的代码均来自https://github.com/vczh/tinymoe. 看了前面的三篇文章,大家应该基本对Tinymoe的代码有一个初步的感觉了.在正确分析"print ...

- 深入理解计算机系统(4.2)------逻辑设计和硬件控制语言HCL

上一篇博客我们简单介绍了Y86指令集体系,而这篇博客我们将介绍指令集体系的逻辑设计和硬件控制语言HCL,为后面去实现Y86打下基础. 在硬件设计中,用电子电路来计算对位进行运算的函数,以及在各种存储器 ...

- [译文]Domain Driven Design Reference(三)—— 模型驱动设计的构建模块

本书是Eric Evans对他自己写的<领域驱动设计-软件核心复杂性应对之道>的一本字典式的参考书,可用于快速查找<领域驱动设计>中的诸多概念及其简明解释. 其它本系列其它文章 ...

随机推荐

- MacBook连接蓝牙鼠标、蓝牙键盘失败的解决方案

问题: keychron k4连接不上MacBook,但是win10和iPhone都可以成功连接. 解决方法: 1.关闭wifi: 2.连接蓝牙键盘: 3.稍等一会,再连接wifi就可以了. 另外,苹 ...

- scp远程上传

scp -P 22 /Users/mac/Downloads/VBoxGuestAdditions_5.2.12.iso root@192.168.1.210:/usr/local/src s ...

- Business Partner - 供应商与客户的集成 - S/4HANA(1)

本文基于S/4HANA 1511版本,同时大部分内容适用于S/4HANA i.e1610/1709/1809. 本文旨在为全新实施的BP配置,或从ECC到S/4HANA的供应商客户主数据迁移提供信息支 ...

- HTML 5标签中<button>的新属性

<button> 标签HTML5 中的新属性 属性 值 描述 autofocus autofocus 规定当页面加载时按钮应当自动地获得焦点. disabled disabled 规定应该 ...

- C++switch结构

- Paillier同态加密的介绍以及c++实现

我们先来简短认识一下Paillier同态加密算法: 如果就这么按照定义来用最简朴的c++程序写 就像这样: #include <iostream> #include <math.h& ...

- Graph-to-ID task

首先图像是一个二维的结构,CNN提取图片的特征,但是是local的,通过kenel的形式,不断的图上移动,通过卷积的形式, 无论移动到哪个位置,内部的结构都是不变的,这就是参数共享. 这个所说的图像显 ...

- Kitty基于Spring Boot、Spring Cloud、Vue.js、Element实现前后端分离的权限管理系统

源码地址:https://gitee.com/liuge1988/kitty 软件架构 后端架构 开发环境 IDE : eclipse 4.x JDK : JDK1.8.x Maven : Maven ...

- kubectl命令小妙招

kubectl命令使用大全 中文: http://docs.kubernetes.org.cn/683.html [root@master-test ~]# kubectl --help kube ...

- 安装Mysql,开发权限,以及复制数据库

官网下载 https://downloads.mysql.com/archives/community/ 解压后安装,管理员身份打开cmd,转到mysql的bin目录,mysqld --ins ...