Xilinx FFT IP v9.0 使用(一)

reference:https://blog.csdn.net/shichaog/article/details/51189711

https://blog.csdn.net/qq_36375505/article/details/81742680 (推荐)

https://blog.csdn.net/lovewdmcwieg/article/details/79235229

https://blog.csdn.net/FPGADesigner/article/details/80694673

该ip用于实现N=2**m(m=3~16)点FFT的变换,

*实现的数学类型包括:

A) 定点全精度

B) 定点缩减位宽

C) 块浮点

每一级蝶型运算后舍入或者取整。对于N点运算,FFT还是逆FFT,scaling策略以及循环前缀的长度是运行时可配置的,可随帧改变,改变变换点数会复位FFT ip核。

*有四种可选择的FFT的实现架构:

1) PipelinedStreaming I/O

2) Radix-4Burst I/O

3) Radix-2Burst I/O

4) Radix-2 Lite Burst I/O

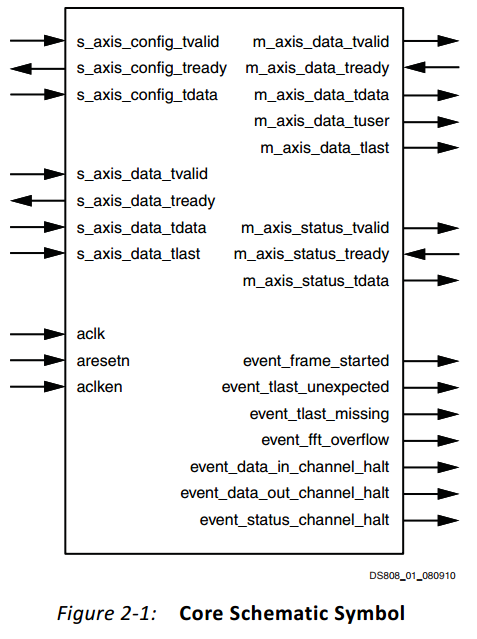

FFT ip核使用基二和基四分解法计算离散傅里叶变换 ; 对于Burst I/O architectures采用时域抽取法实现,对于Pipelined Streaming I/Oarchitecture.使用频域抽取法。当使用基四计算时,其蝶型算法的级数是log 4 (N),每一级包括N/4的基四蝶型运算。对于点数不是4的指数情况,则需要一个额外的基二来组合数据。类似的基二实现法需要log 2 (N)级蝶型运算。对于scaling方法,其每一级的scaling因子由s_axis_config_tdata来配置。Ip核的端口如下:

输入输出方向在上图中已经很明显了,下面描述端口作用

| 名称 | 方向 | 可选择性 | 描述 |

|

aclk |

I | NO | 上升时钟沿采样 |

|

aclken |

I | yes |

高有效,时钟使能 |

|

aresetn |

I | yes |

同步低有效复位,至少需要保持两个低有效周期; |

|

s_axis_config_tvalid |

I | NO |

参数配置通道,config数据有效标志 |

|

s_axis_config_tready |

O | NO |

参数配置通道,高状态下,config才可以再次配置 |

|

s_axis_config_tdata |

I | NO |

参数配置通道,包括了配置信息:CP_LEN,FWD/INV,NFFT 和SCALE_SCH |

|

s_axis_data_tvalid |

I | NO |

数据输入通道,数据有效标志 |

|

s_axis_data_tready |

O | NO |

数据输入通道,状态准备标志 |

|

s_axis_data_tdata |

I | NO |

数据输入通道,数据输入;包括未处理数据:XN_RE/XN_IM |

|

s_axis_data_tlast |

I | NO |

数据输入通道,外部主设备在帧的最后一个样本上断言。 除了生成事件event_tlast_unexpected和event_tlast_missing事件之外,核心不使用它 |

|

m_axis_data_tvalid |

O | NO |

数据输出通道,标志输出数据的有效性 |

|

m_axis_data_tready |

I | NO |

数据输出通道,接受外部从设备断言,表示已准备好接受数据。 仅存在于非实时模式中。 |

|

m_axis_data_tdata |

O | NO |

数据输出通道,包含处理后的数据:XK_RE/XK_IM |

|

m_axis_data_tuser |

O | NO |

数据输出通道,携带额外的每个采样信息,例如XK_INDEX,OVFLO和BLK_EXP |

|

m_axis_data_tlast |

O | NO |

数据输出通道,内核在帧的最后一个采样上断言。 |

|

m_axis_status_tvalid |

O | NO |

状态输出通道,提供状态有效的断言 |

|

m_axis_status_tready |

I | NO |

状态输出通道,外部slave断言是否准备好接收状态数据。仅存在与非实时模式中。 |

|

m_axis_status_tdata |

O | NO |

状态输出通道,包含了状态数据BLK_EXP/OVFLO |

|

event_frame_started |

O | NO |

事件状态通道,当内核开始处理一个新帧时,内核产生断言 |

|

event_tlast_unexpected |

O | NO |

事件状态通道,当内核发现在非帧的最后一个采样时,出现了s_axis_data_tlast拉高,内核将产生断言 |

|

event_tlast_missing |

O | NO |

事件状态通道,当在帧最后一个采样时,s_axis_data_tlast没有被拉高,内核将产生断言 |

|

event_fft_overflow |

O | NO |

事件状态通道,在数据输出通道卸载的数据样本中看到溢出时置位。 仅在溢出是有效选项时出现。 |

|

event_data_in_channel_halt |

O | NO |

事件状态通道,在内核需要数据时,数据输入数据无效,内核产生断言 |

|

event_data_out_channel_halt |

O | NO |

事件状态通道,在内核向外写数据时,出现不能写出时,内核出现断言。仅出现在非实时模式下。 |

|

event_status_channel_halt |

O | NO |

事件状态通道,在内核向外写状态时,出现不能写出时,内核出现断言。仅出现在非实时模式下。 |

上面信号所有s开始的表示的是axi信号的slave端,m是master端。各信号更详细作用参考: pg109 -Fast Fourier Transform v9.0 LogiCORE IP Product Guide.pdf

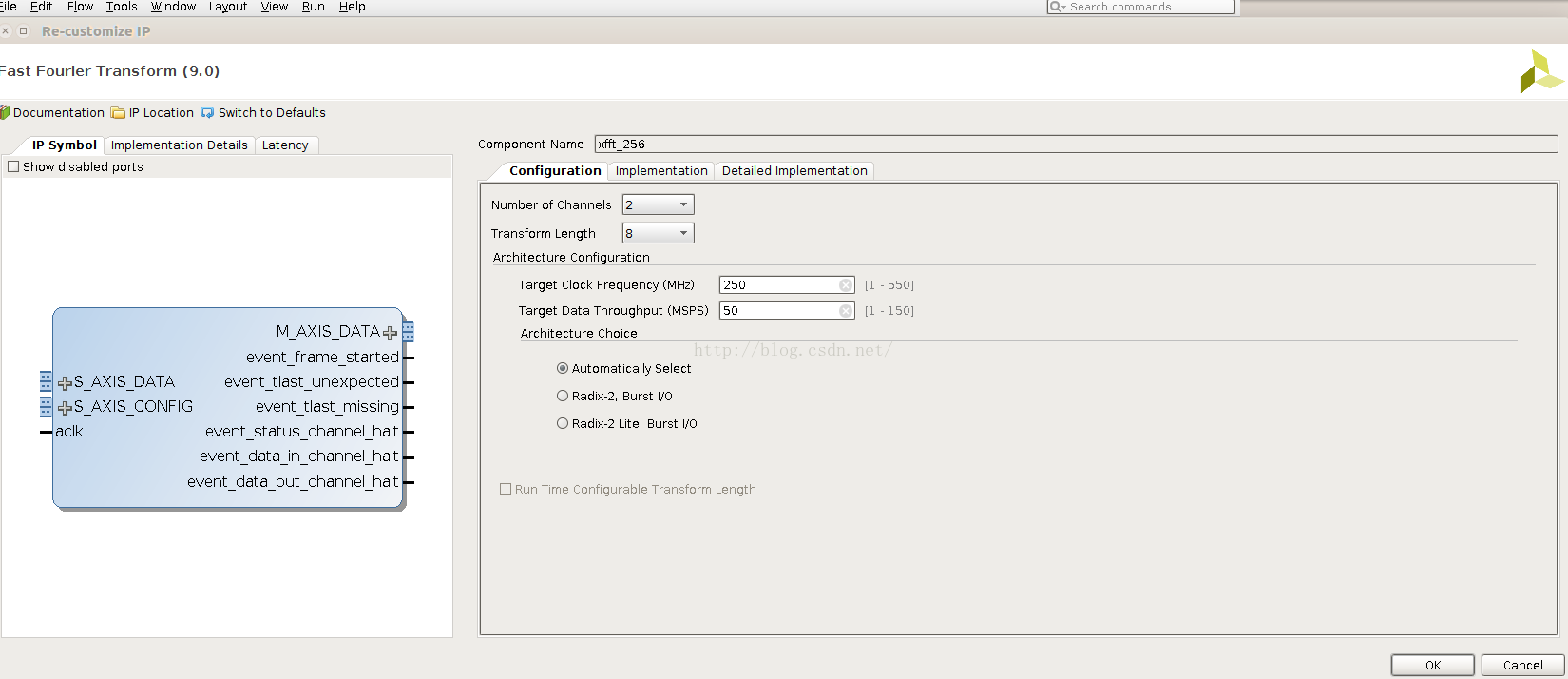

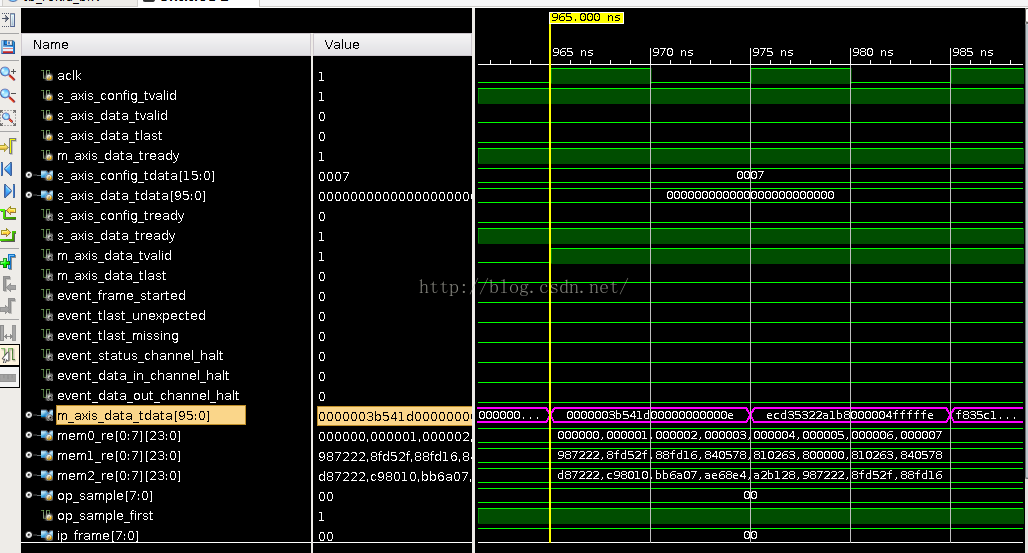

以8点FFT示意,configure

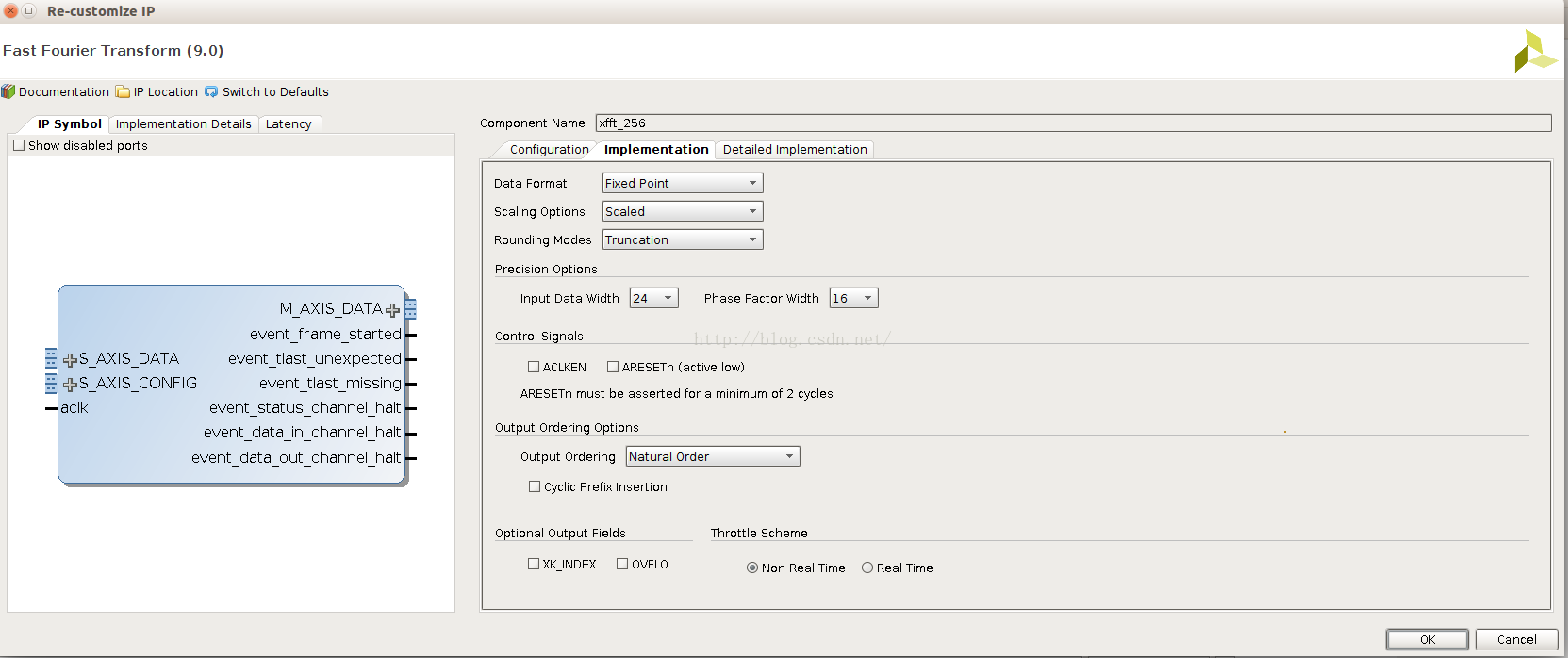

implementtation

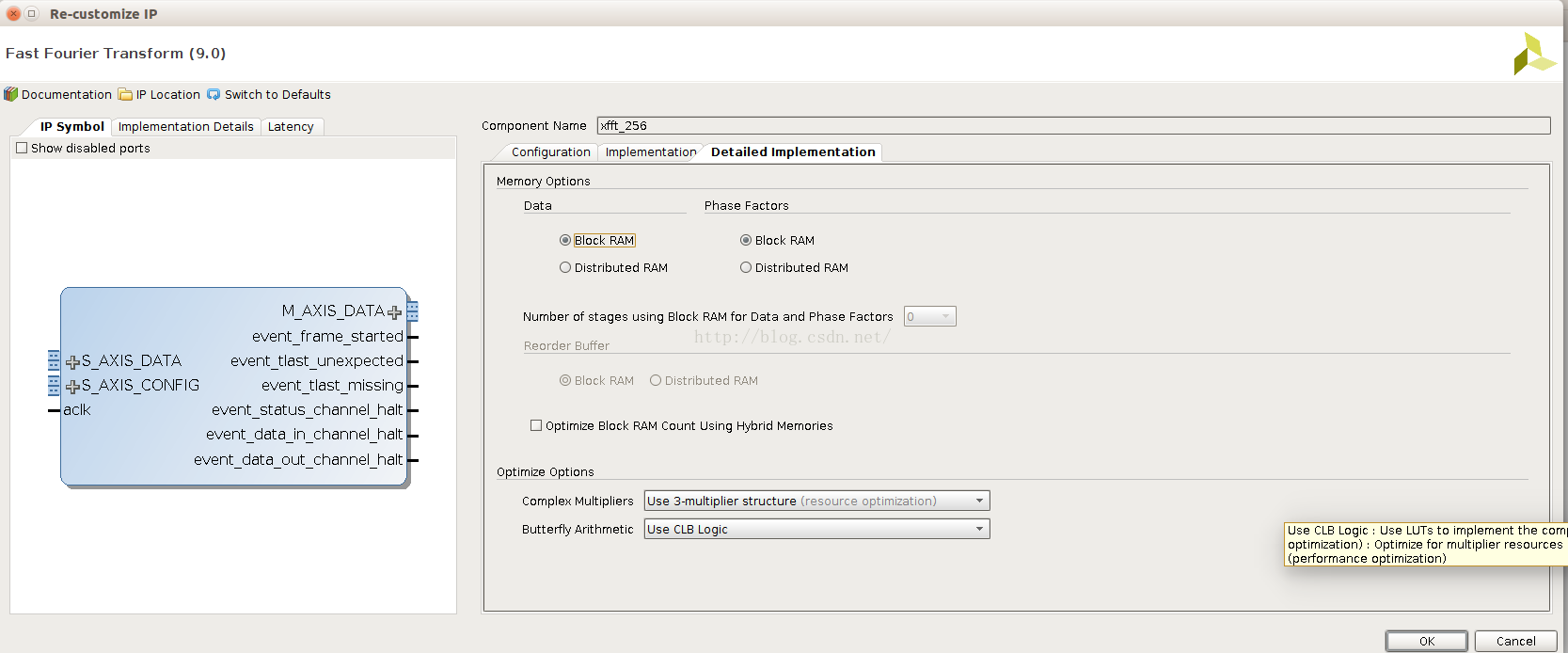

summary

由于xilinx自带的testbench是VHDL的,这里给出自己写的verilog版本的testbench。

`timescale 1ns / 1ps module TB_fft256; // Inputs

reg aclk;

reg s_axis_config_tvalid;

reg s_axis_data_tvalid;

reg s_axis_data_tlast;

reg m_axis_data_tready;

reg [:] s_axis_config_tdata;

reg [: ] s_axis_data_tdata; // Outputs

wire s_axis_config_tready;

wire s_axis_data_tready;

wire m_axis_data_tvalid;

wire m_axis_data_tlast;

wire event_frame_started;

wire event_tlast_unexpected;

wire event_tlast_missing;

wire event_status_channel_halt;

wire event_data_in_channel_halt;

wire event_data_out_channel_halt;

wire [ : ] m_axis_data_tdata; reg[:] mem0_re[:];

reg[:] mem1_re[:];

reg[:] mem2_re[:];

initial $readmemh("/home/gsc/FPGA_exercise/bf_verilog/stimulus0_24bit.dat",mem0_re);

initial $readmemh("/home/gsc/FPGA_exercise/bf_verilog/stimulus1_24bit.dat",mem1_re);

initial $readmemh("/home/gsc/FPGA_exercise/bf_verilog/stimulus2_24bit.dat",mem2_re); reg[:] op_sample= ;

reg op_sample_first = ;

reg[:] ip_frame=;

reg[:] op_frame=; integer i;

// generate clk

always # aclk =! aclk; // Instantiate the Unit Under Test (UUT) xfft_256 uut (

.aclk(aclk), // input wire aclk

.s_axis_config_tdata(s_axis_config_tdata), // input wire [15 : 0] s_axis_config_tdata

.s_axis_config_tvalid(s_axis_config_tvalid), // input wire s_axis_config_tvalid

.s_axis_config_tready(s_axis_config_tready), // output wire s_axis_config_tready

.s_axis_data_tdata(s_axis_data_tdata), // input wire [95 : 0] s_axis_data_tdata

.s_axis_data_tvalid(s_axis_data_tvalid), // input wire s_axis_data_tvalid

.s_axis_data_tready(s_axis_data_tready), // output wire s_axis_data_tready

.s_axis_data_tlast(s_axis_data_tlast), // input wire s_axis_data_tlast

.m_axis_data_tdata(m_axis_data_tdata), // output wire [95 : 0] m_axis_data_tdata

.m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid

.m_axis_data_tready(m_axis_data_tready), // input wire m_axis_data_tready

.m_axis_data_tlast(m_axis_data_tlast), // output wire m_axis_data_tlast

.event_frame_started(event_frame_started), // output wire event_frame_started

.event_tlast_unexpected(event_tlast_unexpected), // output wire event_tlast_unexpected

.event_tlast_missing(event_tlast_missing), // output wire event_tlast_missing

.event_status_channel_halt(event_status_channel_halt), // output wire event_status_channel_halt

.event_data_in_channel_halt(event_data_in_channel_halt), // output wire event_data_in_channel_halt

.event_data_out_channel_halt(event_data_out_channel_halt) // output wire event_data_out_channel_halt

); initial begin // Initialize Inputs aclk = ;

s_axis_config_tvalid = ;

s_axis_config_tdata = ;

s_axis_data_tvalid = ;

s_axis_data_tdata = ;

s_axis_data_tlast = ;

m_axis_data_tready = ; // Wait 100 ns for global reset to finish #;

m_axis_data_tready = ;

s_axis_config_tvalid = ;

//s_axis_config_tdata = 16'b0101100101011011; // FFT desired (and not IFFT

s_axis_config_tdata = 'b0000000000000111; // FFT desired (and not IFFT //s_axis_data_tlast = 1;

s_axis_data_tdata = 'h000000;

s_axis_data_tvalid = ; begin

for(i=;i<;i=i+)

begin

#

s_axis_data_tvalid <= ;

s_axis_data_tdata <= {{'h000000},mem1_re[i],{24'h000000},mem0_re[i]};

$display("mem_a[%d] = %h", i, mem0_re[i]);

// if(i== 256)

// s_axis_data_tlast <= 1;

// else

// s_axis_data_tlast <= 0;

end end

#;

s_axis_data_tdata = 'h000000;

s_axis_data_tvalid = ;

# $finish;

//$stop

end

endmodule

stimulus0_24bit.dat文件内容如下:

000000

000001

000002

000003

000004

000005

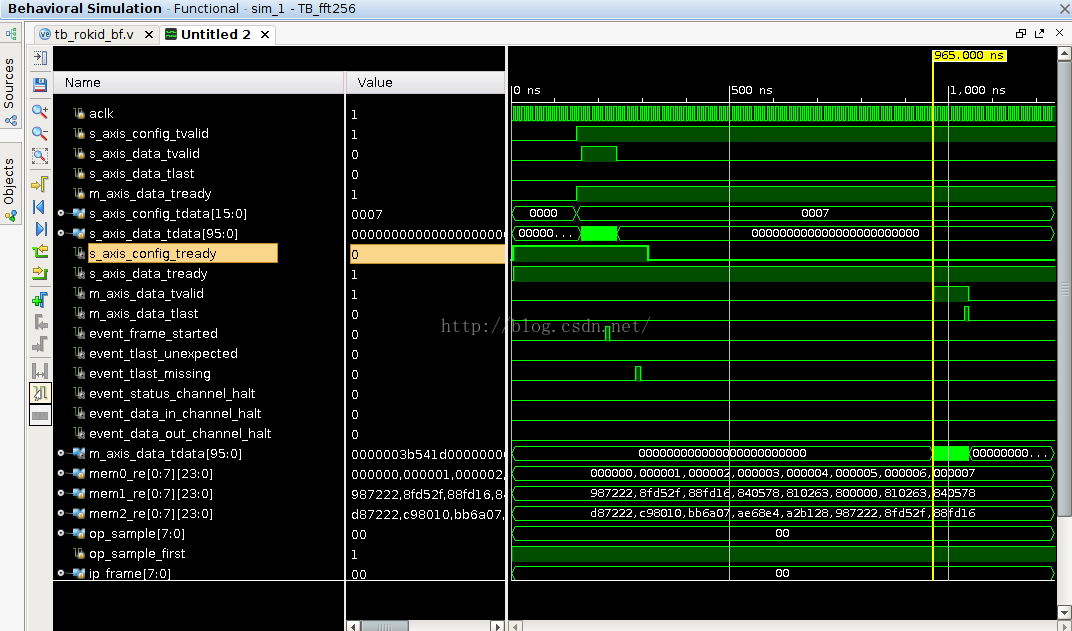

000006

000007stimulus1_24bit.dat文件内容随便,这里是两个通道的FFT计算。仿真波形图如下:

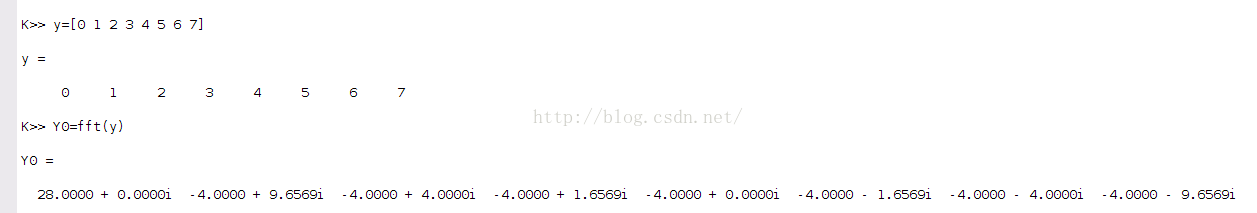

MATLAB计算所得的FFT结果如下:

将FFT结果的放大后得到如下图:

MATLAB计算的结果是28,而fpga仿真结果是0x00000e为14,0xfffffe为-2;这是因为设置了scaling因子,且scaling因子是2,即28/2=14。

关于hls的实现见:

http://blog.csdn.net/shichaog/article/details/50811449

Xilinx FFT IP v9.0 使用(一)的更多相关文章

- Xilinx FFT IP v9.0 使用

该ip用于实现N=2**m(m=3~16)点FFT的变换, 实现的数学类型包含: A) 定点全精度 B) 定点缩减位宽 C) 块浮点 每一级蝶型运算后舍入或者取整.对于N ...

- 从Xilinx FFT IP核到OFDM

笔者在校的科研任务,需要用FPGA搭建OFDM通信系统,而OFDM的核心即是IFFT和FFT运算,因此本文通过Xilinx FFT IP核的使用总结给大家开个头,详细内容可查看官方文档PG109.关于 ...

- Xilinx FFT IP核缩放因子说明

以1024点FFT为例, reg [9:0] scale_sch = 10'b11_10_01_01_01; 流水线结构中,将每个基 2 的蝶形处理单元视为一个阶段. 每个阶段进行一次数据的缩减,缩减 ...

- FFT HDL Optimized模块HDL综合代码生成及与Xilinx xfft IP MEX接口精度详细比较

前面一篇随笔叙述了关于MATLAB中FFT_HDL_Optimzed模块定点(IEEE754单精度float格式)二进制与十进制转换实现,有需要的往前翻一下即可.这一篇随笔将叙述 FFT HDL Op ...

- 实测—fft IP核使用(包括ifft的配置使用)

Vivado xilinx fft9.0 使用笔记: ****注 仿真实测1024点的转换需要经过1148个时钟周期才能得到转换结果: 模块配置信号含义请参考pg109文档手册(写的贼烂会看晕),不详 ...

- FFT ip core

The FFT core provides four architecture options to offer a trade-off权衡取舍 between core size andtransf ...

- PCIE xilinx v5 IP核使用前的研究

外带一个月前啃的一个星期,加本星期心无旁骛,啃出些心得,广惠后人.但愿有用. trn信号是数据链路层的信号 TLP包是数据链路层传给transaction层的包 解包需要一个transaction的协 ...

- xilinx DMA IP核(一) —— loop测试 代码注释

本篇笔记中的代码来自:米联科技的教程“第三季第一篇的DMA_LOOP环路测试” 硬件的连接如下图所示: 图:DMA Loop Block Design 橘色的线就是DMA加FIFO组成的一个LOOP循 ...

- FFT IP核调用与仿真之SCALE压缩因子设置

关于FFT IP核的配置,网上有很多相关的资料可以参考,但是唯独涉及到scaled压缩因子设置这个参数,资料却非常匮乏,这是个什么参数,应该整么设置,设置后对结果输出会有什么影响,整样才能知道它设置的 ...

随机推荐

- Bulk RNA-Seq转录组学习

与之对应的是single cell RNA-Seq,后面也会有类似文章. 参考:https://github.com/xuzhougeng/Learn-Bioinformatics/ 作业:RNA-s ...

- springboot ----> sts如何启动两个实例

idea 实现启动两个spring boot工程实例的方法 可以参考这篇博客. 因为使用spring tool suite 学习spring cloud 需要实例化两个spring boot 工程来构 ...

- Python全栈开发,Day2(in,while else,格式化输出,逻辑运算符,int与bool转换,编码)

一.in的使用 in 操作符用于判断关键字是否存在于变量中 ? 1 2 a = '男孩wusir' print('男孩' in a) 执行输出: True in是整体匹配,不会拆分匹配. ? 1 2 ...

- Error:Unable to tunnel through proxy. Proxy returns "HTTP/1.1 400 Bad Request"解决方法

出现这个错误的原因主要是因为你的本地Gradle和项目的Gradle地址不一样,要么就是没找到 所以需要更改下你的Gradle地址 如图需要将你的Gradle版本的地址改为,你本地的Gradle地址即 ...

- ubuntu+anaconda

1.下载anaconda 查看ubuntu是32位还是64位 命令: uname -m 如果显示i686,你安装了32位操作系统 如果显示 x86_64,你安装了64位操作系统 uname -a 查看 ...

- 将本地 项目文件托管到 github

1.新建一个本地 repository文件夹 2.将想要 托管的项目或文件 复制到repository 文件夹下 2. 右键 git bash here 输入命令 git init 生成本地仓库 4. ...

- ACM-选人问题(救济金发放)

n(n<20)个人站成一圈,逆时针编号为1-n.有两个官员,A从1开始逆时针数,B从n开 始顺时针数.在每一轮中,官员A数k个就停下来,官员B数m个就停下来(注意有可能两个 官员停在同一个人上) ...

- 字符串加密解密(Base64)

var Base64 = { // private property _keyStr: "ABCDEFGHIJKLMNOPQRSTUVWXYZabcdefghijklmnopqrstuvwx ...

- python-day75--django项目问题详细

1.项目名要小写 2.表中字段 AutoField() 表示整形字段,建表时不用写,当整形的数字范围不够你用的时候, 你可以用 BigAutoField()字段, 表示长整形 当表内新增有关 ...

- json 常用的序列化 反序列化对象 代码

序列化对象: ---------------------------------------------------------- Person p = new Person() { Name = & ...