STA——multicycle path

之前去地平线面试的时候被问到了multicycle path的一点问题,其实这个问题我应该知道,看过《Constraining Designs for Synthesis and Timing Analysis A Practical Guide to Synopsys Design Constraints (SDC)》,但当时回答的不好。

看这篇文章需要现对建立时间、保持时间的概念有一些了解。

0. 多周期路径

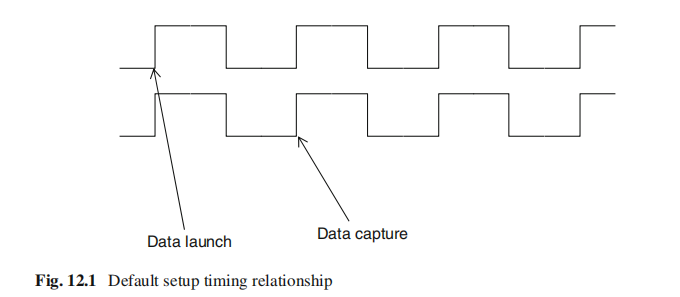

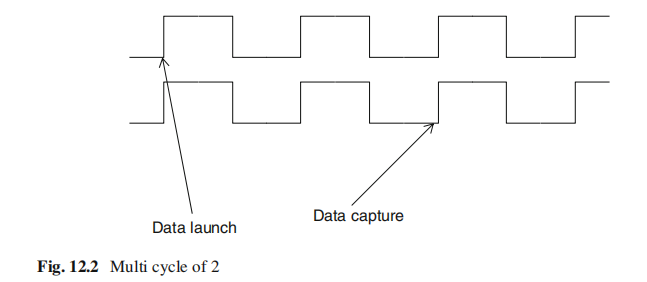

一般情况下数据在任意时钟沿发射,在下一个时钟沿被捕获,但是有时设计者需要延迟几个时钟周期data才被捕获,这就是多周期路径。

默认的建立时间时序:

多周期的建立时间时序:

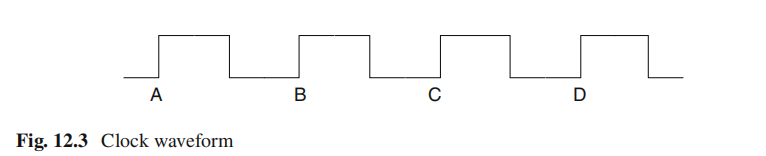

1. 发射时钟和捕获时钟相同

对于上面的时钟,默认是在A沿发射,B沿捕获。在进行建立时间分析时,我们希望在A沿发射数据,在D沿捕获数据,我们可以通过-setup选项,指定多周期路径为3个周期。

set_multicycle_path -setup 3 -from xxx -to xxx

setup time analysis变成了:Tc-q +Tlogic +Tsetup < 3*T+skew。约束变宽松了。

但是这样的话,在进行hold time分析的时候,工具会对捕获寄存器捕获沿之前的那一个时钟沿,也就是C沿进行hold analysis。这样的话hold time analysis变成了

Tc-q + Tlogic > Thold + 2*T,但这增加了电路的复杂性(需要插入一些buffer来增加延迟),没有必要,通过-hold选项,将hold edge向左移动2个周期

set_multicycle_path -hold 2 -from *** -to ***

注意:-setup制定多周期路径为N个周期,-hold使hold edge向左移动N-1个周期

2. 发射时钟和捕获时钟不同

2.1 捕获时钟周期倍长于发射时钟周期

上面例子中发射时钟周期为10ns,捕获时钟周期为20ns。

默认情况下,setup analysis在B沿发射,N沿捕获,组合逻辑路径最大为10ns。对于hold analysis与保持时钟沿没关系,在hold analysis中,可以在A时钟沿发射,M时钟沿捕获,或者在C时钟沿发射,N时钟沿捕获。

因为捕获时钟周期大于采样时钟周期,所以在一个捕获周期中,只能发射一个data。对于在N时钟沿捕获的情况,可以在A或者B时钟沿发射数据。在A发射可以增加额外的10ns的延迟余量。通过-start选项可以声明两个源时钟周期的路径,这使得发射沿从B移动到A。当然要指明是-setup。

set_multicycle_path -setup -start 2 -from xxx -to xxx

对于hold check有两种情况:

1. A发射M捕获。

2.B发射N捕获。

对于上面两种hold check情况,第二种约束更强,组合逻辑需要增加额外的10ns。我们希望hold check恢复到默认的位置,A发射M捕获(或者B发射N捕获),希望lauch edge从B移动到C,通过-start 和- hold选项。

set_multicycle_path -hold -start 1 -from xxx -to xxx

-hold指定移动的周期数。

2.2 发射时钟周期倍长于捕获时钟周期

发射时钟周期为20ns,捕获时钟周期为10ns。

默认的setup check是M发射B捕获;hold check是 M发射A捕获。

M发射,希望在C捕获,这样可以增加额外的10ns的延迟裕量。这可以通过-end选项来指定2个目的时钟周期的路径。

set_multicycle_path -setup -end 2 -from xxx -to xxx

-setup指定路径的周期数,为N

但这会使得hold check变成M发射B捕获,希望它恢复到默认情况,用-end选项指明捕获沿向左移动一个目的时钟周期。

set_multicycle_path -hold -end 1 -from xxx -to xxx

-hold指定移动的周期数,为N-1

2.3 总结

-start:移动源时钟(发射时钟)沿;

-end :移动目的时钟(捕获时钟)沿;

-setup -start N:向左移动发射时钟沿;

-hold -start N-1:向右移动发射时钟沿;

-setup -end N:向右移动捕获时钟沿;

-hold -end N-1:向左移动捕获时钟沿;

3. examples

3.1 FSM

如上图所示,enable逻辑通过一个N个周期的状态机。那么对于从F1发出的actual data,可以在N个周期内到达F3的输入,所以约束如下:

set_multicycle_path -setup N -end -from Cs -through F1/Q -to Cd

set_multicycle_path -hold N-1 -end -from Cs -through F1/Q -to Cd

3.2 reset

set_multicycle_path -fall -from reset_n -setup 3

set_multicycle_path -fall -from reset_n -hold 2

3.3 Large data path macros

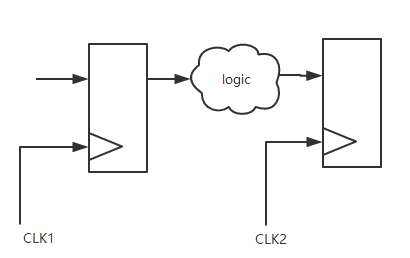

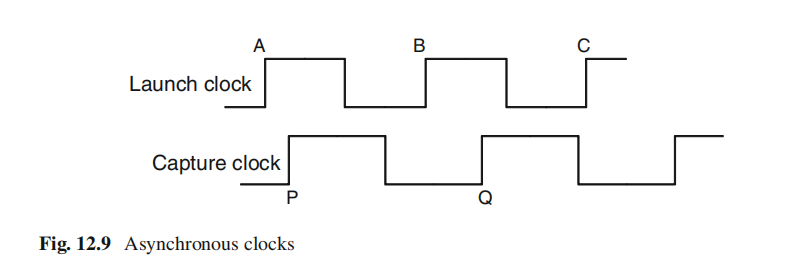

3.4 异步时钟

在跨时钟路径中,一般会生命为fault path,这样STA工具不会对这条路径进行时序分析,那么路径可以有任意大小的delay,但是设计者可能想要约束这一段路径的延迟,如下

set_multicycle_path -from [get_clocks C1] -to [get_clocks C2] -setup 2

set_multicycle_path -from [get_clocks C1] -to [get_clocks C2] -hold 1

原来是在A发射P捕获,但将路径设置为两个捕获周期之后,在A发射Q捕获,组合逻辑延迟扩展了一个捕获周期。这样就将组异步路径合逻辑延迟约束在一个捕获周期多一点。

参考:

STA——multicycle path的更多相关文章

- 【Simplify Path】cpp

题目: Given an absolute path for a file (Unix-style), simplify it. For example,path = "/home/&quo ...

- STA分析(二) multi_cycle and false

multicycle path:当FF之间的组合逻辑path propagate delay大于一个时钟cycle时,这条combinational path能被称为multicycle path. ...

- Timequest GUI

Tasks界面 使用Tasks界面可以访问常用命令,例如生成网表建立报告等. 两个常用命令位于Tasks界面中:打开工程和编写SDC文件.其他命令在下面的文件夹中: Netlist Setup Rep ...

- UVA-12569 Planning mobile robot on Tree (EASY Version) (BFS+状态压缩)

题目大意:一张无向连通图,有一个机器人,若干个石头,每次移动只能移向相连的节点,并且一个节点上只能有一样且一个东西(机器人或石头),找出一种使机器人从指定位置到另一个指定位置的最小步数方案,输出移动步 ...

- 【黑金原创教程】【TimeQuest】【第四章】内部延迟与其他

声明:本文为黑金动力社区(http://www.heijin.org)原创教程,如需转载请注明出处,谢谢! 黑金动力社区2013年原创教程连载计划: http://www.cnblogs.com/al ...

- TIMEQUEST学习之黑金动力(三)

不知不觉,学到的第四章.但是对于TQ的内部模型和外部模型的完整分析还是没有很好的理解.接着学习......... 我们也了解静态时序分析的第一步骤,亦即时钟方面的约束.此外,也稍微对 Report T ...

- 八数码问题(一) 暴力BFS + STL

八数码问题是一个经典的人工智能问题.具体问题不累述了. 思路:由于存在多组测试数据,可以考虑“打表法“.所谓打表法,即枚举所有的初始情况,记录其到达终点的路径.而在这个题目中,顺序打表会调用很多次BF ...

- Xilinx FPGA编程技巧之常用时序约束详解

1. 基本的约束方法 为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取.最普遍的三种路径为: 输入路径(Input Path),使用输入约束 寄存器到寄存器路径(Register-to ...

- set_multicycle_path语法说明【转载】

(转载) (其实多看手册就知道原因了) Q:多周期路径中的检查保持时间时刻,为什么默认是在建立时间检查的前一个cycle?请大家谈谈自己的理解. 如:Set_multicycle_path -setu ...

随机推荐

- 洛谷 P1631 序列合并

题意简述 有两个长度都是N的序列A和B,在A和B中各取一个数相加可以得到N^2个和,求这N^2个和中最小的N个. 题解思路 大根堆,先存入n个和,再比较大小,改变堆中元素. 代码 #include & ...

- 使用flash2print 代替 printflash 将office文档 转为flash 在页面中播放

前一些日子公司需求把用户上传的一些word等 文档 能像百度文库那样 显示给用户, 但是如果是直接显示office文档的话就需要 些控件的支持 .非常的不友好,所以 一开始我就想能不能转成pdf 来 ...

- 重新学习MySQL数据库开篇:数据库的前世今生

本文内容出自刘欣的"码农翻身"公众号,强烈推荐刘欣大大的文章. 数据库的前世今生 小李的数据库之旅 无纸化办公 小李是这个大学计算机科学与技术系的知名学生,他的编程能力了得,使 ...

- Spring-Boot:多种配置注入方式

package com.example.el; import org.springframework.beans.factory.annotation.Value; import org.spring ...

- vue-cli3 按需引入element-ui

按照官网的教程:按需引入需要借助:babel-plugin-component 安装:babel-plugin-component 注意:官网是修改 .babelrc 文件,我这里为了方便就直接修改 ...

- shell习题1

1------->>>批量创建用户. $# --- 统计传入参数的数量 $* --- 传入若干个参数 使用id来确认用户是否存在并创建 向$*进行传参,在运行时加上需要添加的 ...

- java 获取真实ip和根据ip获取ip所在地区

import com.alibaba.fastjson.JSON; import javax.servlet.http.HttpServletRequest; import java.io.ByteA ...

- 随笔编号-04 AngularJS 相关小问题解决方案合集

1 解决 Select选择框遍历时,出现一个空白选项: <select style="width: 20%;margin-left: 5px;height: 31px;" ...

- unity shader之预备知识

1.渲染流水线 任务:从一个三维场景出发,生成(或者渲染)一张二维图像.即:计算机需要从一系列的定点出数据,纹理等信息出发,把这些信息最终转换程一张人眼可以看到的图像.而这个工作通常是由CPU和GPU ...

- 关于简单递归在python3中的实现

话不多说,奉上代码: #倒计时 def count_down(i): if i <= 0: return else: print(str(i)) count_down(i - 1) #求阶乘 d ...