《FPGA全程进阶---实战演练》第二章之硬件平台的搭建

学习FPGA,多多少少应该要懂得硬件电路的设计,这样不单单增加了自己的技能,而且还能够对FPGA的硬件实现有更好的了解。

1 模块划分

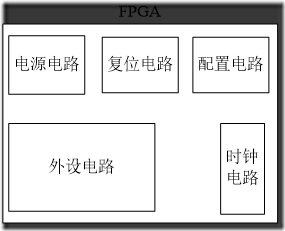

对于一个基本的FPGA硬件平台,常用的几个电路部分:(1)电源电路;(2)复位电路;(3)时钟电路;(4)外设电路;(5)配置电路。如图2.1所示。

图2.1 常用电路模块

1.1电源电路

电源电路是FPGA的核心,是“心脏”,若是电源电路设计的不合理,很可能导致整个系统的溃败,不能正常运行或者失败。对于FPGA来说,基本上包括三类电压:(1)核心电压;(2)I/O电压;(3)辅助电压;

(1) 核心电压是保证FPGA正常工作的基本电压,属于FPGA内部系统电压。

(2) I/O电压是FPGA的I/O引脚工作所需的参考电压。不同bank的I/O所需要的电压不尽相同,对于一些LVDS的I/O电压,可能会需要1.5V,这就不同于LVTTL电平的I/O口。

(3) 除了上述之外的部分的电压,称为辅助电压,例如一些PLL电路的设计等。

需注意以下情况:

(1)器件需要几档电压,电压值分别为多少;

(2)不同档最大电流是多少;

(3)不同档是否有上电要求;

(4)电源的去耦电容如何分配和排布;

(5)电源电压是否需要设计特殊的去耦电路;

(6)个别芯片需要注意接地问题,FPGA的地信号通常是和电压配对的,一般应用中,统一共地是没有问题的。但个别芯片底部中央有个接地焊盘,这个地信号是连接FPGA内部的很多中间信号的地端,它并不和FPGA的其他地信号直接导通,要注意中间接地焊盘。

1.2 时钟电路

FPGA的时钟信号源一般来自外部,在大规模的FPGA内部会带有PLL或DLL等可以对时钟信号进行倍频或分频。由于FPGA内部有大量的寄存器资源,而往往在做逻辑使用时,大量的寄存器会有同一个时钟源,由于时钟到达每一个寄存器所需要的时间不一样,这就导致延迟,若到达寄存器的延迟过大的话,会导致系统混乱,不能正常工作,所以FPGA内部设计了“全局时钟网络”的走线池,通过这种专用走线,可以将同一时钟到达寄存器的时间差控制到最小的范围之内。只需将外部晶振的引脚接到FPGA专用引脚上面即可,EDA软件会自动识别此类信号,并将此信号分配到全局时钟网络上。

需注意以下情况:

(1)系统运行的最高时钟频率是多大;

(2)时钟走线尽可能短,有条件可以做包地处理;

(3)尽可能选择专用的时钟输入引脚;

(4)是否有可用的内部时钟管理模块,(PLL或者DLL,通常是有的)其输入频率是多少(查器件手册,有一个范围);

1.3 配置电路

FPGA芯片的配置是通过JTAG实现在线可编程,当断电时SRAM数据丢失,不能恢复,因此FPGA通常需要外挂一个用于保存当前配置数据流的PROM或Flash芯片,通常称为“配置芯片”。CPLD大多都是基于PROM或Flash来实现可编程特性,对它们进行编程时就已经配置好数据流固化好了,重新上电还能够运行固有的配置数据,CPLD不需要配置芯片。

需注意以下情况:

(1)配置芯片尽量离FPGA近些;

(2)尽量使用官方指定的电路和引脚;

(3)必要时增加阻抗匹配电阻;

1.4复位电路

复位电路的设计,尽量采用专用引脚。FPGA内部大量的寄存器在上电工作之前需要有一个确定的初始状态以确保正常运行。而上电时间对于FPGA的复位来说也至关重要,FPGA是基于SRAM结构,若上电复位时间较短,那么FPGA器件内部很可能没有复位完成,若上电复位时间较长,对于用户交互使用会有一定的影响,所以上电复位时间要确定好。

需注意以下情况:

(1)使用FPGA专用引脚;

(2)上电复位时间要确定;

(3)尽可能选择专用的时钟输入引脚;

《FPGA全程进阶---实战演练》第二章之硬件平台的搭建的更多相关文章

- 《FPGA全程进阶---实战演练》第三十二章 Signal Tap II 应用实例

还有几天就要交文章终稿了,三年的研究生生活也快要结束了,时间飞快,岁月如梭,但学习技术的热情仍然不能松懈,不懂的东西太多,需要实时保持奋斗!!过些天会继续更新<FPGA全程进阶---实战演练&g ...

- 《FPGA全程进阶----实战演练》第二章之系统搭建

1 系统方案 对于设计一款硬件平台,首先要确定整体框架,确定各个模块所需要的芯片以及电压分配情况.图2.6是笔者曾经设计的硬件平台系统. 图2.6系统框图 对于选定一个系统方案之后,接下来做的要先去查 ...

- 《FPGA全程进阶---实战演练》第二十一章 电源常用类型:LDO和 DCDC

高速电路中的电源设计 高速电路中的电源设计大概分为两种,一种是集总式架构,一种是分布式架构.集总式架构就是由一个电源输入,然后生成多种所需要的电压.如图1所示.这种架构会增加多个DC/DC模块,这样成 ...

- 《FPGA全程进阶---实战演练》第二十一章之 几种常用电平分析及特性

TTL,CMOS以及LVTTL,LVCMOS TTL和CMOS是数字电路中两种常见的逻辑电平,LVTTL和LVCMOS是两者低电平版本.TTL是流控器件,输入电阻小,TTL电平器件速度快,驱动能力大, ...

- 《FPGA全程进阶---实战演练》第二十一章 细说低速与高速电路设计之电阻 电容 电感 磁珠

1.1 什么是高速电路 信号的最高频率成分是取决于有效频率,而不是周期频率. 高速电路的定义是根据信号的有效频率来计算的,在现实世界中,任何信号都是由多个频率分量的正弦波叠加而成的.定义各正弦波分 ...

- 《FPGA全程进阶---实战演练》第二章之焊接板子及调试注意事项

1.若是读者第一次做板子,强烈建议画完PCB板后将PCB图打印出来,然后对照你买的芯片将芯片放置对 应的位置,然后查看所有的封装格式适不适合,否则等你做出板子来后再试,为时晚矣.笔者虽然知道要这么 做 ...

- 《FPGA全程进阶---实战演练》第二章之PCB layout注意事项以及投板几点说明

上一篇博客讲述了各个部分的原理图,那么根据原理图画出PCB,其实PCB是一门很大的学问,想要掌握谈何容易.就笔者在画PCB时的一些注意事项做一些说明. 1.电源部分的电源线 ...

- 《FPGA全程进阶---实战演练》第四章之实验平台软硬件使用简介

本章主要是讲解读者在进行FPGA逻辑设计之前的准备工作,需要下载Quartus II软件和 Modelsim 软件,一个是用来进行FPGA逻辑设计,一个是用来对逻辑进行理论分析与验证. 1.1 qua ...

- 《FPGA全程进阶---实战演练》第一章之FPGA介绍

1 什么是FPGA FPGA也即是Field Programmable Gate Array的缩写,翻译成中文就是现场可编程门阵列.FPGA是在PAL.GAL.CPLD等可编程器件的基础上发展起来的新 ...

随机推荐

- PLSQL_Oracle基本概念总结(汇总)

2014-08-16 Created By BaoXinjian

- 使用fork并发处理多个client的请求和对等通信p2p

一.在前面讲过的回射客户/服务器程序中,服务器只能处理一个客户端的请求,如何同时服务多个客户端呢?在未讲到select/poll/epoll等高级IO之前,比较老土的办法是使用fork来实现.网络服务 ...

- kubernetes 二

部署harbor Habor是由VMWare中国团队开源的容器镜像仓库.事实上,Habor是在Docker Registry上进行了相应的企业级扩展,从而获 得了更加广泛的应用,这些新的企业级特性包括 ...

- php json的相关操作

类与json <?php class userinfo { var $user_name; var $user_ip; var $user_logintime; } $u = new useri ...

- 在python中配置MySQL数据库

MySQL数据库(1) 尽管用文件形式将数据保存到磁盘,已经是一种不错的方式.但是,人们还是发明了更具有格式化特点,并且写入和读取更快速便捷的东西——数据库(如果阅读港台的资料,它们称之为“资料库”) ...

- 实战:MySQL Sending data导致查询很慢的问题详细分析(转)

这两天帮忙定位一个MySQL查询很慢的问题,定位过程综合各种方法.理论.工具,很有代表性,分享给大家作为新年礼物:) [问题现象] 使用sphinx支持倒排索引,但sphinx从mysql查询源数据的 ...

- appium操作微信公众号H5 web页面

安卓微信公众号的H5页面是webview,一般操作需要切换context. 在执行如下步骤,就能直接像识别native样识别webview 1.代码追加: ChromeOptions options ...

- 页面返回刷新或H5监听(手机的)返回键

1. pushHistory(); window.addEventListener("popstate", function(e) { alert("我监听到了浏览器的返 ...

- 【转】获取scrollTop兼容各浏览器的方法,以及body和documentElement是啥?

1.各浏览器下 scrollTop的差异 IE6/7/8: 对于没有doctype声明的页面里可以使用 document.body.scrollTop 来获取 scrollTop高度 : 对于有do ...

- Lua脚本语言快速入门手册

学了两天Lua语言,感叹其短小精悍,上手极快,语法还很舒服,不错!整理下学习过程中经常用到的基础知识,共勉! Lua用法简述 Lua语言是在1993年由巴西一个大学研究小组发明,其设计目标是作为嵌入式 ...