数字IC设计入门必备——VIM自定义模板调用与VCS基本仿真操作示例

一、前言

毕业论文答辩结束,闲下来写篇文章。芯片研发人员都在Linux系统下借助各种EDA工具和代码语言完成工作,因此提高代码开发效率,熟练运用开发工具是十分必要的。本文讲述VIM编辑神器的verilogHDL自定义模板调用以及VCS仿真软件的基本使用方式。

二、VIM编辑器自定义模板调用

在之前的博文中谈到过GVIM编辑器中可以通过调用模板来生成重复性代码,但没有介绍自定义模板的方式。关于VIM的安装与配置详细内容,见参考文献1。这里主要用到VIM的用户配置文件:.vimrc(若没有新建该文件并编辑),我们在用户目录下使用ls -al命令可以看到该文件:

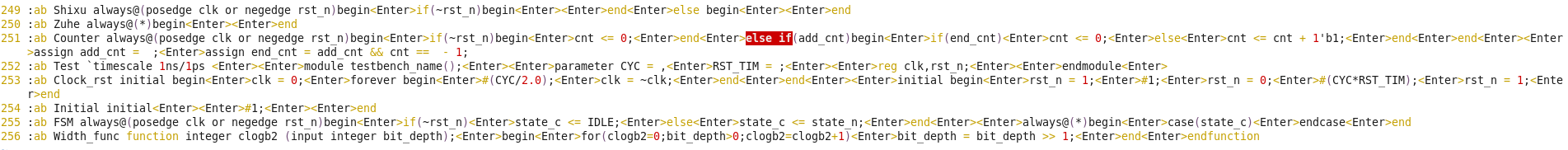

使用VIM编辑器打开VIM配置文件,以下部分是在文件底部自行添加的命令:

自定义模板的格式为 :ab <com> <code>

其中com是调用指令,code是当前指令生成的代码。我们新建一个.v文件测试下就能看出模板调用的妙处了。

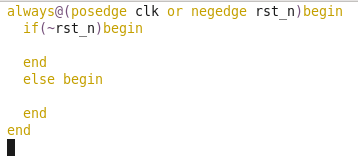

编辑(插入)模式下,输入Shixu后按下回车生成:

输入Zuhe后按下回车生成:

输入Counter后按下回车生成:

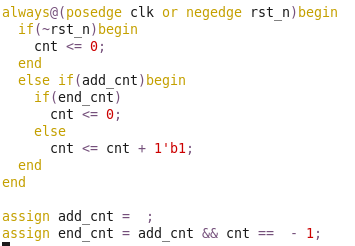

这三个是最常用到的代码,三者相互组合可以完成很多功能了。但若状态或工作模式较多,一般采用状态机完成。输入FSM后按下回车生成:

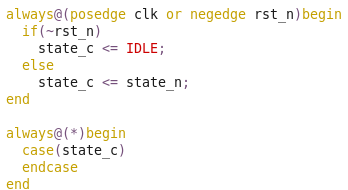

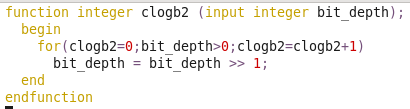

在设计时,经常要根据数值范围设定变量的位宽。此时经常用到一个位宽计算到函数。输入Width_func后按下回车生成:

在设计文件里常用的重复性代码基本就这些了,可以根据自己的coding style灵活调整。接下来说说testbench部分。输入Test后按下回车生成:

里边包括了testbench中的时钟和复位相关的参数与信号定义。实际上时钟和复位信号的产生也是可以复用的。输入Clock_rst后按下回车生成:

自定义模板还没有灵活到可以生成模块例化代码,这一部分功能得借助其他脚本语言完成了,笔者还没有尝试过。

三、VCS软件仿真

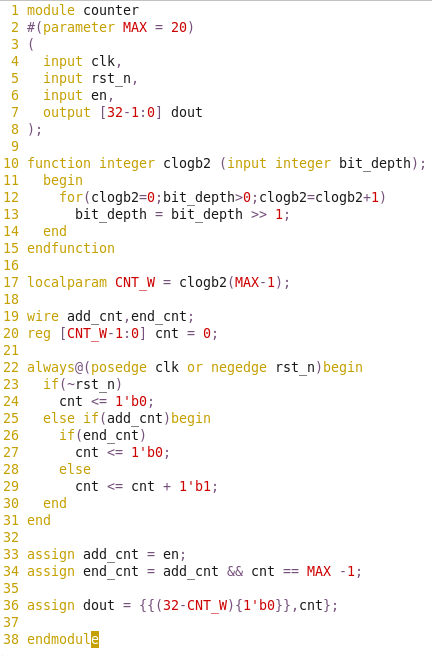

光说这个软件没什么意思,我们来举个栗子~设计一个计数器,输出位宽固定32位。当使能信号拉高则开始从0计数直到最大值后再次从0开始递增。设计代码counter.v:

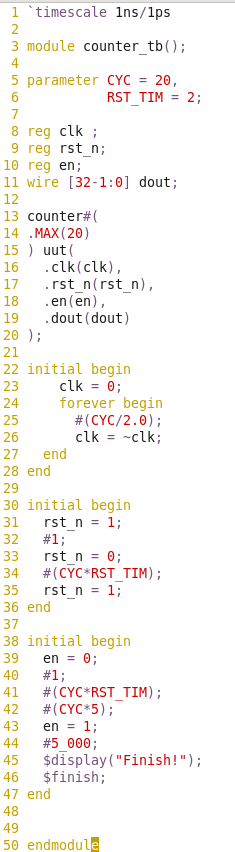

测试代码 counter_tb.v:

VCS仿真大体分为三步:编译、仿真以及调试。编译命令:vcs *.v -debug_all 命令行界面会显示些信息:

之后文件夹内会生成simv文件,执行该文件进行仿真。./simv -gui 这里使用-gui选项打开DVE图形界面。

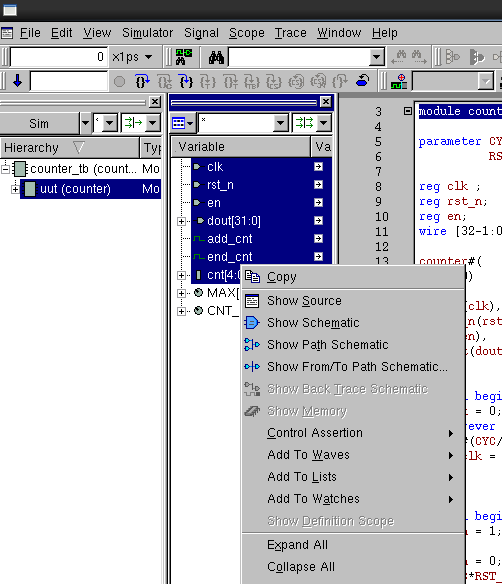

接下来的操作和常用的Modelsim差不多了。把要观测的信号添加到波形窗口:

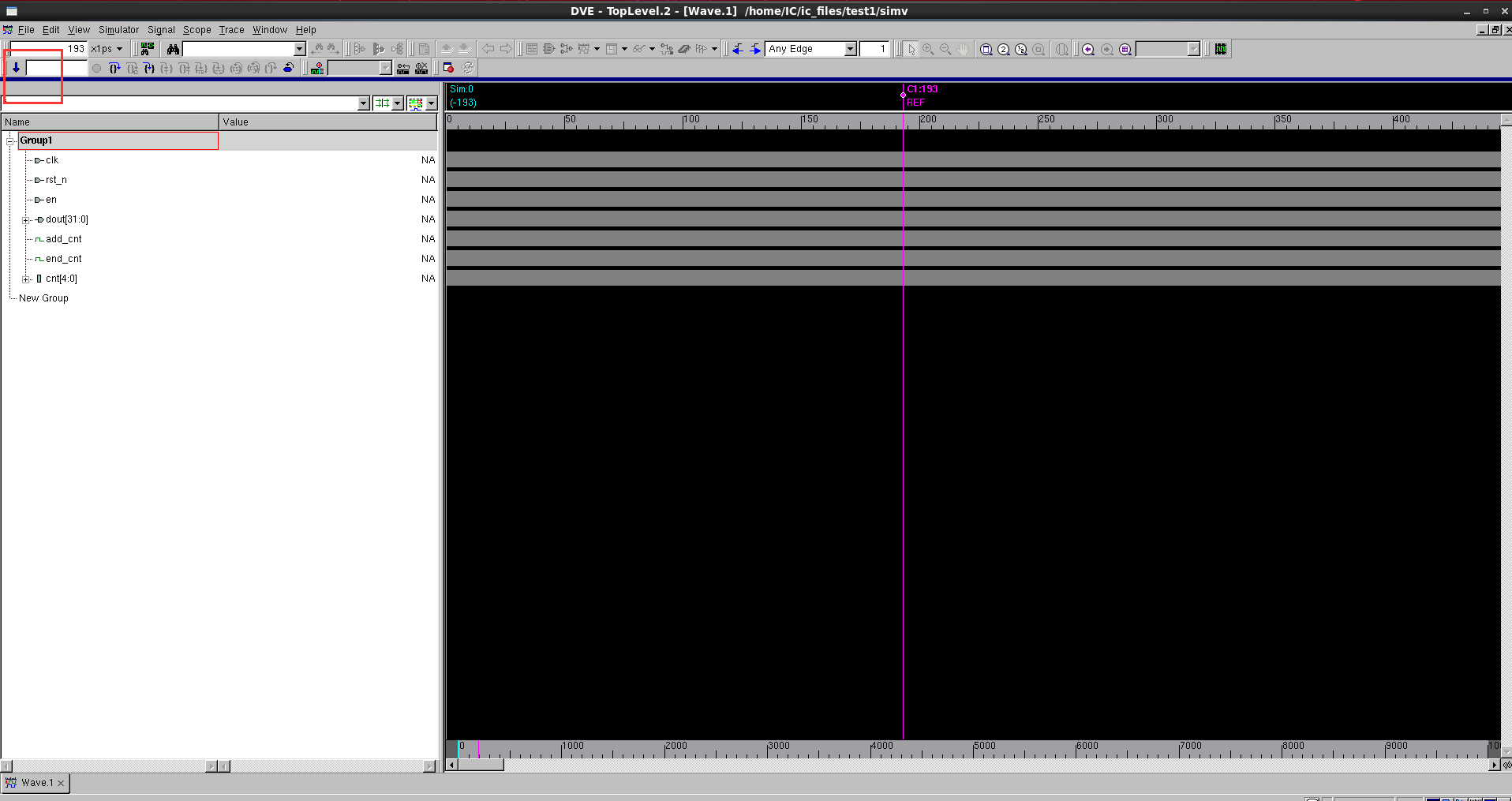

点击左上角按钮运行仿真:

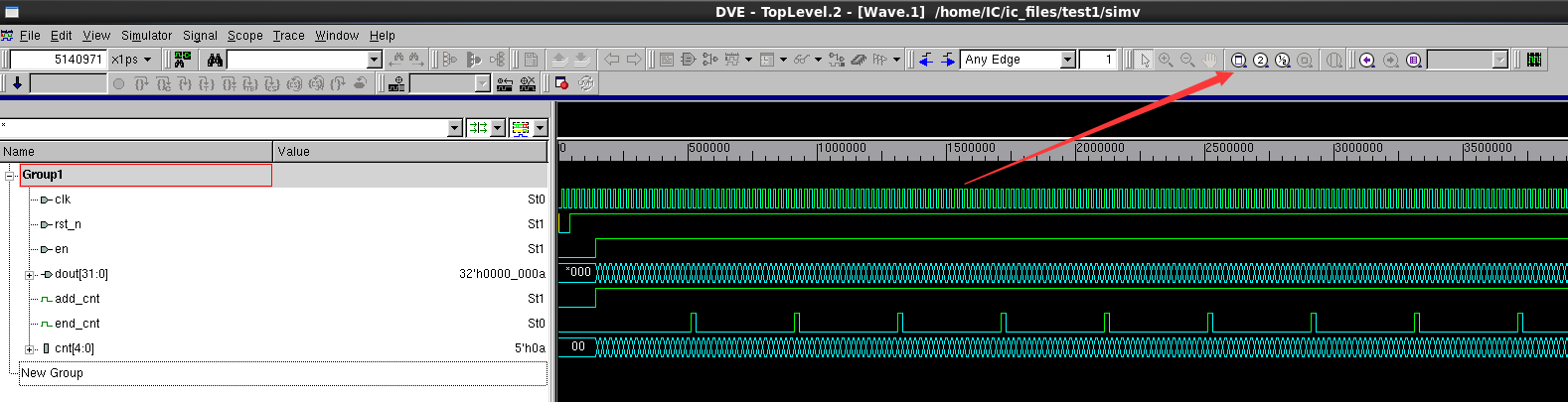

按下红色箭头所指位置观察全局波形:

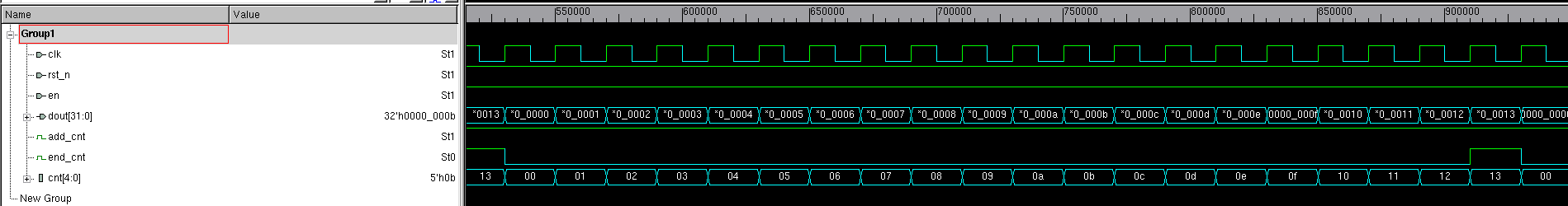

按住鼠标左键拖动来局部放大数据波形,计数器与输出从0到19周期性递增,功能正确。

复杂的操作后续用到再学。

参考文献

1 vim 的安装及配置 - QIYUEXIN - 博客园 https://www.cnblogs.com/qiyuexin/p/6398606.html

2 VCS使用学习 - IC_SOC_ARM - CSDN博客 https://blog.csdn.net/ic_soc_arm_robin/article/details/44262063

3 VCS-DVE - 百度文库 https://wenku.baidu.com/view/f5f7ce8f69eae009591becc1.html

4 数字芯片实验室的个人空间 - 哔哩哔哩 ( ゜- ゜)つロ 乾杯~ Bilibili https://space.bilibili.com/87907395/channel/detail?cid=64692

数字IC设计入门必备——VIM自定义模板调用与VCS基本仿真操作示例的更多相关文章

- 数字IC设计入门书单

首发于观芯志 写文章 数字IC设计入门书单 Forever snow 1 年前 作者:Forever snow链接:你所在领域的入门书单? - 知乎用户的回答来源:知乎著作权归作者所有,转 ...

- 数字IC设计工程师的知识结构

刚毕业的时候,我年少轻狂,以为自己已经可以独当一面,庙堂之上所学已经足以应付业界需要.然而在后来的工作过程中,我认识了很多牛人,也从他们身上学到了很多,从中总结了一个IC设计工程师需要具备的知识架构, ...

- VerilogHDL概述与数字IC设计流程学习笔记

一.HDL的概念和特征 HDL,Hard Discrimination Language的缩写,翻译过来就是硬件描述语言.那么什么是硬件描述语言呢?为什么不叫硬件设计语言呢?硬件描述语言,顾名思义就是 ...

- 【转载】数字IC设计流程及开发工具

原文链接:https://www.zhihu.com/question/28322269/answer/42048070 Design Flow &lt;img src="h ...

- 数字IC设计-15-DPI(延续)

简介 供SV,无论是构建测试激励,或模拟硬件的并行行为,DPI这是非常方便.上次我们介绍SV内通"import"导入和电话C性能. 在本节,通过一个简单的例子来说明C什么语言的函数 ...

- 数字IC设计工程师成长之路

学习的课程 仿真工具VCS实践学习 2019年12月9日-2019年12月23日

- 数字IC前后端设计中的时序收敛(五)--Max Transition违反的修复方法

本文转自:自己的微信公众号<数字集成电路设计及EDA教程> 里面主要讲解数字IC前端.后端.DFT.低功耗设计以及验证等相关知识,并且讲解了其中用到的各种EDA工具的教程. 考虑到微信公众 ...

- 数字IC前后端设计中的时序收敛(四)--Max Capacitance违反的修复方法

本文转自:自己的微信公众号<数字集成电路设计及EDA教程> 里面主要讲解数字IC前端.后端.DFT.低功耗设计以及验证等相关知识,并且讲解了其中用到的各种EDA工具的教程. 考虑到微信公众 ...

- 数字IC前后端设计中的时序收敛(三)--Hold违反的修复方法

本文转自:自己的微信公众号<数字集成电路设计及EDA教程>(二维码见博文底部) 里面主要讲解数字IC前端.后端.DFT.低功耗设计以及验证等相关知识,并且讲解了其中用到的各种EDA工具的教 ...

随机推荐

- postman使用--构建工作流和newman

构建工作流 在使用“Collection Runner”的时候,集合中的请求执行顺序就是请求在Collection中的显示排列顺序.但是,有的时候我们不希望请求按照这样的方式去执行,可能是执行完第一个 ...

- Python基础篇 -- 字符串

字符串 字符串是不可变的对象,任何操作对原字符串是不会有任何影响的. 索引和切片 索引 . 索引就是下标, 下标从 0 开始, 使用[] 来获取数据 s1 = "0123456" ...

- LeetCode 字符串的排列

给定两个字符串 s1 和 s2,写一个函数来判断 s2 是否包含 s1 的排列. 换句话说,第一个字符串的排列之一是第二个字符串的子串. 示例1: 输入: s1 = "ab" s2 ...

- python中with用法及原理

资源的管理在程序的设计上是一个很常见的问题,例如管理档案,开启的网络socket与各种锁定(locks)等.最主要的问题在于我们必须确保这些开启的资源在使用之后能够关闭(或释放),若忘记关闭这些资源, ...

- 2018-10-09中国裁判文书网爬虫vl5x和DocID分析

本来是想要抓取食药监的药品数据,看到js加密很繁琐,调了一个星期没有结果,想看看其他类似网站的js加密情况,发现裁判文书网的加密好像不是太复杂,经过两天的分析和编写,基本把vl5x加密和DocID解密 ...

- CVS update常用技巧

常用的命令有 cvs update 全部更新 cvs update path/to/file 来更新某一个文件 cvs update -dP 意为删除空目录创建新目录 cvs -f -n update ...

- perl学习之子程序

一.定义子程序即执行一个特殊任务的一段分离的代码,它可以使减少重复代码且使程序易读.PERL中,子程序可以出现在程序的任何地方.定义方法为:sub subroutine{statements;}二.调 ...

- mysql函数总结

MySQL函数 MySQL数据库提供了很多函数包括: 数学函数:字符串函数:日期和时间函数:条件判断函数:系统信息函数:加密函数:格式化函数: 一.数学函数 数学函数主要用于处理数字,包括整型.浮点数 ...

- python 实现计算器功能 输入字符串,输出相应结果

import re formul='1 - 2 *( (6 0- 30+(0-40/5) * (9-2* 5/3 +7 /3*99/4*2998 +10 *568/14)) - (-4*3) / (1 ...

- 关于security的简单理解和应用

2018年7月30日1.搜索引擎框架百度google Lucene 单机操作,就是一堆jar包中的api的使用,自己干预,如何创建索引库,删除索引库,更新索引库,高亮,自己调度APISolr 支持we ...