DMA与cache一致性的问题

Cache和DMA本身似乎是两个毫不相关的事物。Cache被用作CPU针对内存的缓存利用程序的空间局部性和时间局部性原理,达到较高的命中率,从而避免CPU每次都必须要与相对慢速的内存交互数据来提高数据的访问速率。DMA可以作为内存与外设之间传输数据的方式,在这种传输方式之下,数据并不需要经过CPU中转。

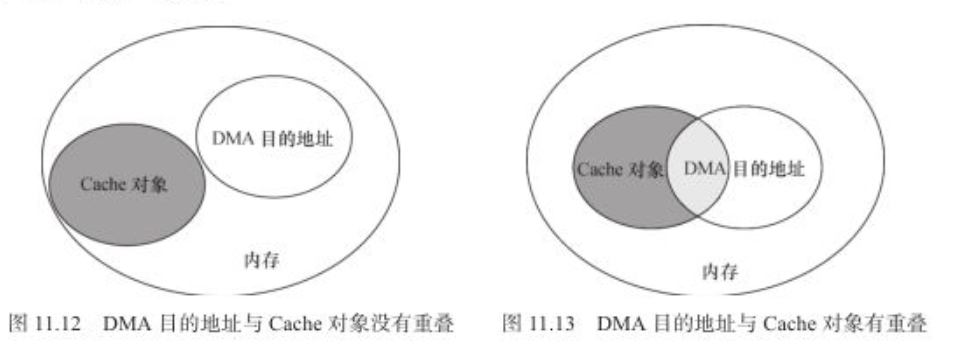

假设DMA针对内存的目的地址与 Cache缓存的对象没有重叠区域(如图11.12所示)DMA和 Cache之间将相安无事。但是,如果DMA的目的地址与 Cache所缓存的内存地址访问有重叠(如图11.13所示),经过DMA操作,与 Cache缓存对应的内存中的数据已经被修改,而CPU本身并不知道,它仍然认为 Cache中的数据就是内存中的数据,那在以后访问 Cache映射的内存时f,它仍然使用陈旧的 Cache数据。这样就会发生 Cache与内存之间数据“不一致性”的错误。

所谓 Cache数据与内存数据的不一致性,是指在采用 Cache的系统中,同样一个数据可能既存在于 Cache中,也存在于主存中, Cache与主存中的数据一样则具有一致性,数据若不一样则具有不一致性。需要特别注意的是, Cache与内存的一致性问题经常被初学者遗忘。在发生 Cache与内存不一致性错误后,驱动将无法正常运行。如果没有相关的背景知识,工程师几乎无法定位错误的原因,因为这时所有的程序看起来都是完全正确的。 Cache的不一致性问题并不是只发生在DMA的情况下,实际上,它还存在于 Cache使能和关闭的时刻。例如,对于带MMU功能的ARM处理器,在开启MMU之前,需要先置 Cache无效,对于TLB,也是如此,代码清单11.12给出的这段汇编可用来完成此任务。

/* 使cache无效 */

mov r0, #0

mcr p15, 0, r0, c7, c7, 0

mcr p15, 0, r0, c7, c10, 4

mcr p15, 0, r0, c8, c7, 0

因此申请DMA内存而避免Cache不一致的问题的话,就需要使用dma_alloc_coherent()等方法申请;

DMA与cache一致性的问题的更多相关文章

- 【转】DMA和cache一致性

DMA和cache一致性问题 Cache原理 CPU缓存(Cache Memory)是位于CPU与内存之间的临时存储器,它的容量比内存小的多但是交换速度却比内存要快得多.缓存的出现主要是为了解决CPU ...

- DMA及cache一致性的学习心得 --dma_alloc_writecombine【转】

转自:https://www.cnblogs.com/hoys/archive/2012/02/17/2355914.html 来源:http://xmxohy.blog.163.com/blog/s ...

- Cache一致性与DMA

cache一致性与DMA 第一个问题 对于进行DMA操作的设备, 并不是所有系统都保持它们的cache一致性.在这种情况下, 准备进行DMA的设备可能从RAM得到陈旧的数据, 因为脏的cache行可能 ...

- 3.3.1 Cache一致性的基本概念

PCI设备对可Cache的存储器空间进行DMA读写的操作的过程较为复杂,有关Cache一致性的话题可以独立成书.而不同的处理器系统使用的Cache Memory的层次结构和访问机制有较大的差异,这部分 ...

- ARM Linux 内核 panic 之cache 一致性 ——cci-400 cache一致互联

ARM Linux 内核 panic 之cache 一致性 ——cci-400 cache一致互联 CCI-400 集合了互联和一致性功能,有 2 个 ACE slave 接口和 3 个 ACE-Li ...

- Linux DMA访问的一致性

DMA访问的一致性 DMA对内存是直接访问的,而CPU对内存的访问有时会通过cache.不管是CPU还是DMA访问内存,都需要确保cache的一致性.本文只分析从DMA的角度,对内存的访问如何确保ca ...

- 《大话处理器》Cache一致性协议之MESI (转)

原文链接:http://blog.csdn.net/muxiqingyang/article/details/6615199 Cache一致性协议之MESI 处理器上有一套完整的协议,来保证Cache ...

- ARM Linux 内核 panic 之cache 一致性 ——Cortex-A9多核cache和TLB一致性广播

ARM Linux 内核 panic 之cache 一致性 ——Cortex-A9多核cache和TLB一致性广播 Cortex-A9的多喝CPU可以接收和执行一致性广播操作,当其使能并处于SMP模式 ...

- Cache一致性协议之MESI

http://blog.csdn.net/muxiqingyang/article/details/6615199 Cache一致性协议之MESI 处理器上有一套完整的协议,来保证Cache一致性.比 ...

随机推荐

- 7z 程序打包 Demo

最近准备做一个用户端 异常收集的程序 需要收集用户机器的程序日志和相关信息 准备打包发回来 所以研究了一下7Z 文件压缩 做一个笔记吧 遇到的问题: 1:VS2008 遇到 loadlibrary ...

- 【OSX】多个JDK共存时选择要使用的JDK版本

10.5以后的$JAVA_HOME没有被在.bash_profile中设置的话会被默认设置为 /usr/libexec/java_home. 如果一台mac里面安装了多个JDK, 可以通过/usr/l ...

- Set "$USE_DEPRECATED_NDK=true" in gradle.properties to continue using the current NDK integration. 解决办法

1.将 jni 文件夹名改为 cpp: 2.添加 CMakeLists.txt; 3.修改 build.gradle; externalNativeBuild { cmake { path " ...

- PHP-CPP开发扩展(二)

PHP-CPP是一个用于开发PHP扩展的C++库.本节讲解PHP输出和函数的实现. 输出和错误 上面的helloworld示例里,我们使用Php::out进行输出,并使用了std::endl换行刷新缓 ...

- 音频标签化3:igor-8m项目的训练、评估与测试

上一节介绍了youtube-8m项目,这个项目以youtube-8m dataset(简称8m-dataset)样本集为基础,进行训练.评估与测试.youtube-8m设计用于视频特征样本,但实际也适 ...

- Java并发编程笔记之读写锁 ReentrantReadWriteLock 源码分析

我们知道在解决线程安全问题上使用 ReentrantLock 就可以,但是 ReentrantLock 是独占锁,同时只有一个线程可以获取该锁,而实际情况下会有写少读多的场景,显然 Reentrant ...

- leetcode — reverse-integer

/** * Source : https://oj.leetcode.com/problems/reverse-integer/ * * Created by lverpeng on 2017/7/4 ...

- Java基础之基本数据类型

前言:Java内功心法之基本数据类型,看完这篇你向Java大神的路上又迈出了一步(有什么问题或者需要资料可以联系我的扣扣:734999078) 变量就是申请内存来存储值.也就是说,当创建变量的时候,需 ...

- 一张图读懂PBN飞越转弯衔接TF/CF航段计算

在PBN旁切转弯的基础上,再来看飞越转弯接TF(或CF)航段,保护区结构上有些相似,只是转弯拐角处的保护区边界有“简化”,其余部分是相近的. FlyOver接TF段的标称航迹有一个飞越之后转弯切入航迹 ...

- vb.net 使用NPOI控制Excel檔

'導入命名空間 Imports NPOI.HSSF.UserModelImports NPOI.HPSFImports NPOI.POIFS.FileSystem Private Sub A1()'方 ...