IIC双向电平转换电路设计

现代的集成电路工艺加工的间隙可达0.5μm 而且很少限制数字I/O 信号的最大电源电压和逻辑电平。

为了将这些低电压电路与已有的5V或其他I/O电压器件连接起来,接口需要一个电平转换器。对于双向的总线系统像I2C 总线电平转换器必须也是双向的,不需要方向选择信号。解决这个问题的最简单方法是连接一个分立的MOS-FET管到每条总线线路,尽管这个方法非常简单但它不仅能不用方向信号就能满足双向电平转换的要求还能将掉电的总线部分与剩下的总线系统隔离开来,保护低电压器件防止高电压器件的高电压毛刺波。

双向电平转换器可以用于标准模式高达100kbit/s 或快速模式高达400kbit/s I2C 总线系统。

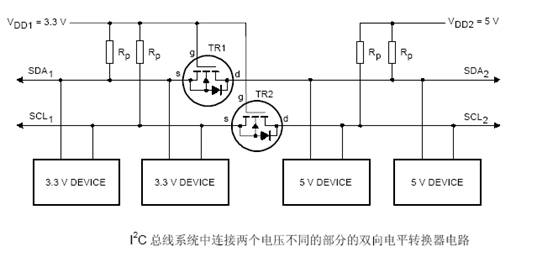

通过使用双向电平转换器可以将电源电压和逻辑电平不同的两部分I2C 总线连接起来配置入下图所示。左边的低电压部分有上拉电阻而且器件连接到3.3V 的电源电压,右边的高电平部分有上拉电阻器件连接到5V 电源电压。两部分的器件都有与逻辑输入电平相关的电源电压和开漏输出配置的I/O。

每条总线线路的电平转换器是相同的而且由一个分立的N通道增强型MOS-FET管串行数据线SDA的TR1和串行时钟线SCL 的TR2 组成。门极g 要连接到电源电压VDD1, 源极s 连接到低电压部分的总线线路而漏极d 则连接到高电压部分的总线线路。很多MOS-FET 管的基底与它的源极内部连接,如果内部没有,就必须建立一个外部连接。因此,每个MOS-FET 管在漏极和基底之间都有一个集成的二极管n-p 结。

如下图所示。

电平转换器的操作

在电平转换器的操作中要考虑下面的三种状态:

1、 没有器件下拉总线线路。

低电压部分的总线线路通过上拉电阻Rp 上拉至VDD1(3.3V) MOS-FET 管的门极和源极都是VDD1(3.3V), 所以它的VGS 低于阀值电压MOS-FET 管不导通这就允许高电压部分的总线线路通过它的上拉电阻Rp 拉到5V。 此时两部分的总线线路都是高电平只是电压电平不同。

2、一个3.3V 器件下拉总线线路到低电平。

MOS-FET 管的源极也变成低电平而门极是VDD1(3.3V)。VGS高于阀值,MOS-FET 管开始导通然后高电压部分的总线线路通过导通的MOS-FET管被VDD1(3.3V)器件下拉到低电平,此时两部分的总线线路都是低电平而且电压电平相同。

3、一个5V 的器件下拉总线线路到低电平。

MOS-FET 管的漏极基底、二极管低电压部分被下拉,直到VGS 超过阀值,MOS-FET 管开始导通,低电压部分的总线线路通过导通的MOS-FET管被5V 的器件进一步下拉到低电平,此时两部分的总线线路都是低电平而且电压电平相同。

这三种状态显示了逻辑电平在总线系统的两个方向上传输,与驱动的部分无关。状态1 执行了电平转

换功能,状态2和3按照I2C总线规范的要求在两部分的总线线路之间实现“线与”的功能。除了VDD1 (3.3V)

和VDD2 (5.0V)的电源电压外,还可以是例如2V VDD1 和10V VDD2 等的正常操作。其中VDD2必须等于或高于VDD1 。

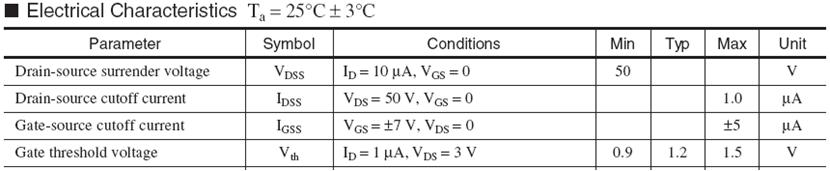

但是值得注意的是,VDD1作为较低部分的电压,必须能够大于所选择的MOS-FET的阀值电压,也就是必须能够打开MOS-FET。此管参数必须谨慎选择。如下两种参数MOS-FET,在VDD1 (1.8V)到VDD2 (3.0V) 的电路中就可能存在截然不同的效果。

管1

管2

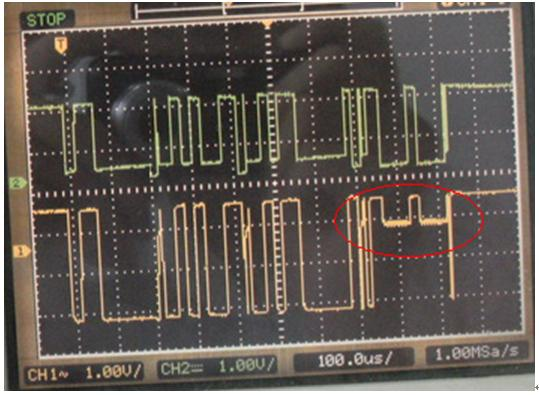

选择管1,由于VGS的范围是1.0~2.5V,很有可能出现大于1.8V的状况,因此VDD1方面传输低电平信号时,MOS-FET不能很完全的被打开,导致到VDD2 (3.0V)方面的信号不能彻底为低,出现半高状态。如下图:

择管2,由于VGS的范围是0.9~1.5V小于1.8V,因此,通路才会正常工作。

其他不同电压间的转换原理如上,请悉心选择器件。

在3.3V IIC总线中用到5V IIC器件,该电路已实验通过。

IIC双向电平转换电路设计的更多相关文章

- 一种简单实用的双向电平转换电路3.3V-5V

当你使用3.3V的单片机的时候,电平转换就在所难免了,经常会遇到3.3转5V或者5V转3.3V的情况,这里介绍一个简单的电路,他可以实现两个电平的相互转换(注意是相互哦,双向的,不是单向的!).电路十 ...

- 简单实用的双向电平转换电路(3.3v-5v)

当你使用3.3V的单片机的时候,电平转换就在所难免了,经常会遇到3.3转5V或者5V转3.3V的情况,这里介绍一个简单的电路,他可以实现两个电平的相互转换(注意是相互哦,双向的,不是单向的!).电路十 ...

- TTL和COMS电平匹配以及电平转换的方法

一.TTL TTL集成电路的主要型式为晶体管-晶体管逻辑门(transistor-transistor logic gate),TTL大部分都采用5V电源.1.输出高电平Uoh和输出低电平UolUoh ...

- 5V与3.3V器件电平转换

源:5V与3.3V器件电平转换 当你使用3.3V的单片机的时候,电平转换就在所难免了,经常会遇到3.3转5V或者5V转3.3V的情况,这里介绍一个简单的电路,他可以实现两个电平的相互转换(注意是相互哦 ...

- 一种电平转换的方法,使用CPLD

参考应用笔记 http://www.doc88.com/p-0197252336968.html 前言 在原理图设计初期,可能涉及到引脚电平的转换操作,比如主FPGA的某BANK电平为1.5V,但外围 ...

- Arduino 电平转换 升压 OUTPUT与9V/12V元件通信

原因 网络上有不少怎么让Arduino的5V电平转换成3.3V电平,从而和工作在3.3V下的芯片相互沟通的教程.但是如果想驱动高于5V电压的芯片,就找不到教程了.因此今天我来介绍一种方式,能让Ardu ...

- MSP430电平转换

说道到这个电平转换,写程序的时候居然还要示波器来观察现象,表示我们交的是211的学费,上的却不是211大学,创新实验室的仪器设备真的是少的可怜啊,我级不吐槽了说说这个电平转换的一些知识还有看法吧.. ...

- 单片机电平转换电路5V 3.3V串口通讯等(转)

源: 单片机电平转换电路5V 3.3V串口通讯等

- 5V系统和3.3V系统电平转换

在设计一个带MCU或者ARM系统电路时候,经常遇见MCU的VCC是3.3V,但是外围电路需要5V.有时候是反过来.虽然现在MCU的IO都声称支持TTL电平,但是我们谁也不想将MCU的IO口直接接上5V ...

随机推荐

- 将表格导出为excel

<table id="tableExcel" border="1"> <tr> <th>零</th> <t ...

- React自己写的一个地图小组件

由于今天比较闲,就玩了玩react,然后就封装了一个地图的组件,当然功能比较简单,因为就是随手写的小东西,但是由于引用了百度API和bee-mobile,所以用起来可能要薛微麻烦一点点,但是我保证,只 ...

- Power BI 与 Azure Analysis Services 的数据关联:4、Power BI 连接到Azure Analysis Services 并展示

Power BI 与 Azure Analysis Services 的数据关联:4.Power BI 连接到Azure Analysis Services 过使用服务器名称别名,用户可以使用较短 ...

- CSS expression属性

expression属性是在IE5版本之后支持使用的,用来把CSS属性和JavaScript脚本关联起来.简单粗暴的说,该属性是用来调用JavaScript代码的. CSS属性后面是一段JavaScr ...

- Mobile first! Wijmo 5 + Ionic Framework之:费用跟踪 App

费用跟踪应用采用了Wijmo5和Ionic Framework创建,目的是构建一个hybird app. 我们基于<Mobile first! Wijmo 5 + Ionic Framework ...

- Android事件总线(一)EventBus3.0用法全解析

前言 EventBus是一款针对Android优化的发布/订阅事件总线.简化了应用程序内各组件间.组件与后台线程间的通信.优点是开销小,代码更优雅,以及将发送者和接收者解耦.如果Activity和Ac ...

- 数据层的多租户浅谈(SAAS多租户数据库设计)

在上一篇“浅析多租户在 Java 平台和某些 PaaS 上的实现”中我们谈到了应用层面的多租户架构,涉及到 PaaS.JVM.OS 等,与之相应的是数据层也有多租户的支持. 数据层的多租户综述 多租户 ...

- 在 Android 手机上运行 Python 程序

- 彻底修改 Windows 系统用户名

在 Windows 安装的时候会输入一个用户名,电脑店装的一般都会给你设置成Admin之类的.这个时候你想要改成自己的,一般都是直接在 控制面板 > 用户帐户和家庭安全 > 用户帐户 &g ...

- 【转】URL编码(encodeURIComponent和decodeURIComponent)

转自http://blog.jhonse.com/archives/2032.jhonse 最近在用CI框架的时候,发现一个问题,URL的GET方式链接时,如果用中文字符的话,就会出现问题,提示:链接 ...