DDR中寄存器的问题

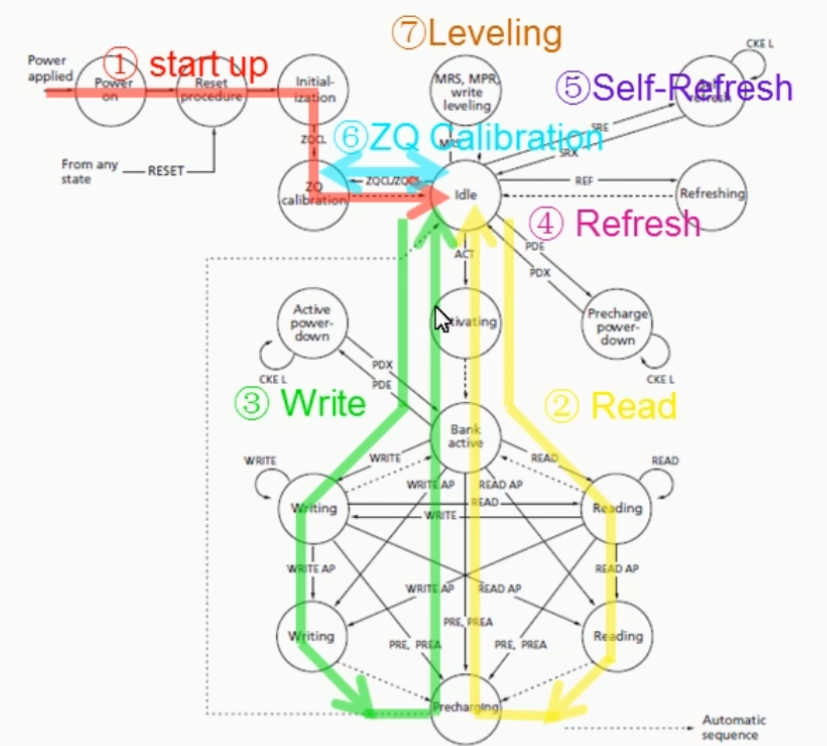

图中虚线是自动跳转,实线是通过发送命令才能跳转的。

下面是框中对应的命令。

ACT = ACTIVATE

MPR = Multipurpose register

MRS = Mode register set

PDE = Power-down entry

PDX = Power-down exit

PREA = PRECHARGE ALL

PRE = PRECHARGE

READ = RD, RDS4,

RDS8

ZQCL = ZQ LONG CALIBRATION

REF = REFRESH

SRE = Self refresh

entry

ZQCS = ZQ SHORT CALIBRATION

RESET = START RESET

WRITE = WR, WRS4, WRS8

PROCEDURESRX

= Self refresh exit

WRITE AP = WRAP, WRAPS4, WRAPS8

READ AP = RDAP, RDAPS4, RDAPS8

状态图:

Start-Up : Power on -> Reset Procedure -> Initialization -> ZQ Calibration -> IDLE

READ : idle -> Activating -> (Bank Active) -> Reading -> Precharging ->idle

Write :idle -> Activating -> bank active -> writing -> precharging ->idle

Refresh : idle -> Refreshing ->idle

Self-refresh : idle -> self-refresh ->idle

ZQ Caliration : idle -> ZQCL/ZQCS ->idle

Leveling : idle -> MRS,MPR,Write Leveling -> idle

Power Down :

复位(Reset)

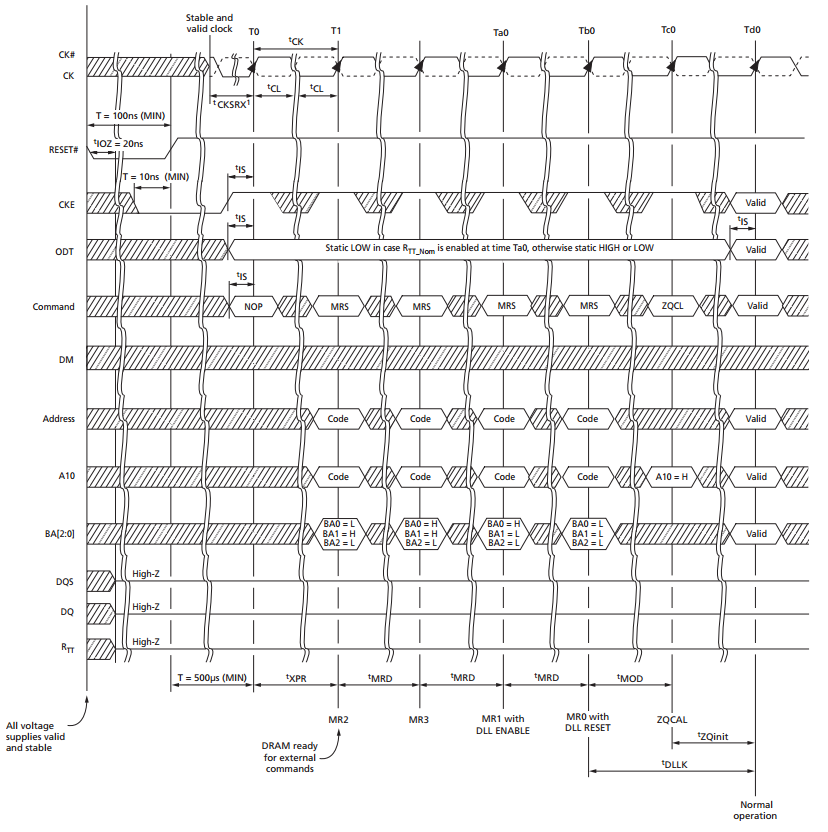

复位是异步复位,当拉低后要保持100ns,在些期间输出会被禁止,ODT被关闭(处于高阻)。

在RESET#拉高之前CKE应该拉低,当RESET拉高之后,DRAM必须要重新初始化。所有的

计数器—除刷新计数器外,都会复位,当RESET拉低之后 ,DRAM中存储的数据,也变为不

确定值。

操作中需要注意的点:

(1) 复位拉低要保持100ns;

(2) 在RESET#拉高之前CKE要保持低电平不变;

初始化(Initialization)

ZQCL: 上电初始化后,用完成校准ZQ电阻。ZQCL会触发DRAM内部的校准引擎,

一旦校准完成,校准后的值会传递到DRAM的IO管脚上,并反映为输出驱动和ODT阻值。

ZQCS: 周期性的校准,能够跟随电压和温度的变化而变化。校准需要更短的时间窗口,

一次校准,可以有效的纠正最小0.5%的RON和RTT电阻。

MRS (mode register set)

MODE Register Set, 模式寄存器设置。为了应用的灵活性,不同的功能、特征

和模式等在DDR3芯片上的Mode Register中,通过编程来实现。模式寄存器MR

没有缺省值,因此模式寄存器MR必须在上电或者复位后被完全初始化,这样才

能使得DDR可以正常工作。正常工作模式下,MR也可以被重新写入。模式寄存

器的设置命令周期tMRD就两次操作的最小时间。MRS命令要求所有bank处于

idle状态,并且MRS只能在precharged状态下进行。

模式寄存器,分为MR0、MR1、MR2和MR4。

MR0用来存储DDR3的不同操作模式的数据:包括突发长度、读取突发种类、CAS长度、测试模式、DLL复位等。

MR1用来存储是否使能DLL、输出驱动长度、Rtt_Nom、额外长度、写电平使能等。

MR2用来存储控制更新的特性, Rtt_WR阻抗,和CAS写长度。

MR3用来控制MPR。

• BA2 = 0, BA1 = 0, BA0 = 0 for MR0

• BA2 = 0, BA1 = 0, BA0 = 1 for MR1

• BA2 = 0, BA1 = 1, BA0 = 0 for MR2

• BA2 = 0, BA1 = 1, BA0 = 1 for MR3

MPR寄存器

MPR: Multi-purpose register. 多用途寄存器。MPR的功能是读出一个预先设定

的系统时序校准比特序列。为了使能MPR功能,需要在MRS的寄存器MR3的A2

位写1,并且在此之前需要将DDR3的所有bank处于idle状态; 一旦MPR被使能后,

任何RD和RDA的命令都会被引入到MPR寄存器中,当MPR寄存器被使能后, 除非

MPR被禁止(MR3的A2=0),否则就只有RD和RDA被允许。在MPR被使能的时候,

RESET功能是被允许的。

Precharge Power Down: bank在in-progress命令后关闭。

Active Power Down:bank在in-progress命令后依然打开。

Self refresh temperature(SRT)

当disable,手动更新的速率是以85度为标准的,并且要求器件的温度不能超过85

个人感觉这里面有三个概念要搞清楚,(自刷新)self refresh ,(自动刷新)ASR和SRT。

当ASR和SRT均未开开启时就是self refresh模式,self refresh的刷新频率为1x,它是按

照在85T内的正常温度范围内来刷新,如果温度超过85T,在85T~95T扩展温度范围,就

只能开启ASR或SRT,SRT开启之后就是按2x的刷新频率来刷新,而ASR是根据温度范

围来决定刷新的频率,如果在正常温度范围则为1x,如果是扩展温度范围则为2x。

但要注意,SRT 和 ASR不能同时开启。

有这样一句话:自动刷新用于正常操作模式 ,在自动刷新时 ,其他命令无法操作。

自刷新主要用于低功耗状态下的数据保存 。

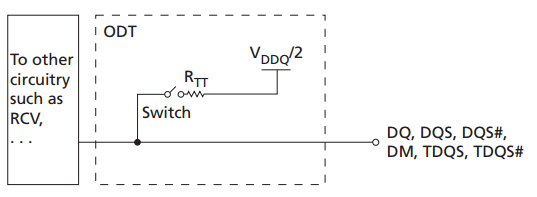

ODT(On-Die Termination)

动态ODT是DDR3新增加的功能有,DDR3的新动态ODT特性具有针对不同的负载条件

优化终结电阻值的灵活性,这样可以改善信号完整性,它还提供了管理终结功耗的一种

方法。动态ODT使DDR3器件能无缝地改变针对不同模块发出的“WRITE”命令之间的终

结电阻值。该特性是DDR2系统所不能提供的,在同一个器件上,DDR2需要总线空闲时

间来改变终结电阻值。

在DLL Disable Mode模式下是不支持ODT(NOM ODT和动态ODT)的,在DLL Disable Mode下

ODT管脚必须要拉低,RTT,nom MR1[9, 6, 2] 和 RTT(WR) MR2[10, 9]也要设置为0。

ODT分为常规ODT(NOM ODT)和动态ODT两种模式,分别对应Rtt_Nom和Rtt_WR两种终端值。

当ODT在模式寄存器中设置使能之后—无论是Rtt_Nom还是Rtt_WR,并把ODT管脚拉高,DRAM

将会终结 DQS, DQS#, DM, 和所有的DQ. 对于TDQS使能的x8 DRAM,TDQS和TDQS#也会被终结。

要使能Rtt_WR并非必须使能Rtt_Nom,两都是相互独立的,如果禁止Rtt_Nom使能Rtt_WR,DRAM只会在写操作时终结相应信号,

注意区分几个参数。

Rtt、Rtt.nom和Rtt(wr),, RTT(EFF)。

四个状态:使能(enabled),禁止(dsiabled),打开(turn on)和关闭(turn off)。

下图是一个简单框图。

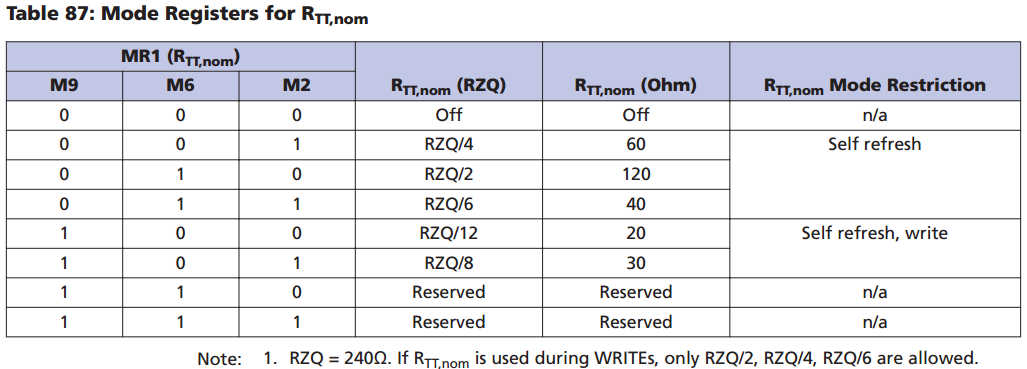

NOM ODT

RTT,nom取值是由MR1[9, 6, 2]来决定的。从下图中可以看出RTT,nom可以取2.4.6.8.12,RZQ是240Ω。如果RTT,nom应用在写操作过程中,。

常规的ODT(NOM ODT)可以用在备用(standby conditions)或者写操作中,Rtt_Nom用在写操作中,只能取RZQ/2, RZQ/4, 和 RZQ/6。但是在DDR3的读操作中不是能用终结电阻的。

动态ODT

动态ODT只应用于写周期,在Rtt_Nom 和 Rtt_WR均使能的情况下,DRAM会在写操作命令时把Rtt_Nom切换到Rtt_WR,当写突发完成后又会切换回Rtt_Nom,在终结阻值的切换过程是不需要MR寄存器去设置的。

Synchronous ODT

什么是同步ODT?

在self refresh模式或者在MR1与MR2中disable掉ODT时ODT管脚的电平被忽略。

当ODT (RTT_nom)无效时,ODT (RTT_nom)值是高阻Z。

使能动态ODT只能应用在写周期,并且在write leveling mode下不可用。动态ODT与ODT可以相互独立使用。

同步ODT参数。

DDR中寄存器的问题的更多相关文章

- 第五章之S5PV210将u-boot.bin从SD卡中搬到DDR中

1,在完成上一节的memory初始化后,接下来在arch/arm/cpu/armv7/start.S的160行:如下图 2,跳转到arch/arm/lib/board.c下的board_init_f函 ...

- DDR中常用概念

一.DDR中的基本术语 (2)逻辑Bank SDRAM的内部是一个存储阵列,类似于一张表格.和表格的检索原理一样,先指定一个行(Row),再指定一个列(Column),就可以准确地找到所需要的单元格, ...

- 转:DDR中端接技术基本概念

DDR中端接技术基本概念 版权声明:转载请注明出处:http://blog.csdn.net/lg2lh https://blog.csdn.net/lg2lh/article/details/90 ...

- DDR中的一些知识点说明(ODT,ZQ校准,OCT,TDQS)

ODT ( On-DieTermination ,片内终结)ODT 也是 DDR2 相对于 DDR1 的关键技术突破,所谓的终结(端接),就是让信号被电路的终端吸 收掉,而不会在电路上形成反射, 造成 ...

- 【STM32】MDK中寄存器地址名称映射分析

对于MCU,一切底层配置,最终都是在配置寄存器 51单片机访问地址 51单片机经常会引用一个reg51.h的头文件.下面看看它是怎么把名字和寄存器联系在一起的: 1 sfr p0=0x80; 2 p0 ...

- DDR中的命令

(3) 列地址选择(CAS#): 选择器件内感兴趣的地址列 行地址选择(RAS#): 选择设备中感兴趣的地址行. (4)(precharge)预充电 DRAM读取具有破坏性,也就是说,在读操作中会破坏 ...

- 【嵌入式开发】ARM 芯片简介 (ARM芯片类型 | ARM处理器工作模式 | ARM 寄存器 | ARM 寻址)

: 12MHz 晶振 对应 405 ~ 532 MHz 处理速度; -- : 16K 指令缓存, 16K 数据缓存; -- : 32KB 指令缓存, 32KB 数据缓存; (3) 内存接口对比 : 提 ...

- 【接口时序】8、DDR3驱动原理与FPGA实现(一、DDR的基本原理)

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:无 3.仿真工具:无 硬件平台: 1. FPGA型号:无 2. DDR3型号:无 二. 存储器的分类 存储器一 ...

- 深入分析DDR(转载)

深入分析:我们为何需要DDR2内存技术 http://www.cnblogs.com/thx-bj/archive/2008/04/02/1134040.html 文/IT168评测室特约 Myddn ...

随机推荐

- MVC与WebApi中的异常统一处理

1.简单例子 /// <summary> /// 全局页面控制器异常记录 MVC的异常处理 /// </summary> public class CustomErrorAtt ...

- Beanstalkd消息队列的安装与使用

一.Beanstalkd是什么? Beanstalkd是一个高性能,轻量级的分布式内存队列 二.Beanstalkd特性 1.支持优先级(支持任务插队)2.延迟(实现定时任务)3.持久化(定时把内存中 ...

- golang语言中os/exec包的学习与使用

package main; import ( "os/exec" "fmt" "io/ioutil" "bytes" ) ...

- 微信小程序解密

获取OpenId和SessionKey private string GetOpenIdAndSessionKeyString(string code) { string wxUrl = " ...

- 免费证书https://lamp.sh/ssl.html

https(全称:Hyper Text Transfer Protocol over Secure Socket Layer),是以安全为目标的 http 通道,简单讲是 http 的安全版.即 ht ...

- Bonding

一.简介 双网卡配置设置虚拟为一个网卡实现网卡的冗余,其中一个网卡坏掉后网络通信仍可正常使用,实现网卡层面的负载均衡和高可用性 二.原理 网卡工作在混杂(promisc)模式,接收到达网卡的所有数 ...

- 自适应手机网站meta name代码

<meta name="viewport" content="width=device-width,initial-scale=1.0"> co ...

- hdu 2647 (拓扑排序 邻接表建图的模板) Reward

题目链接http://acm.hdu.edu.cn/showproblem.php?pid=2647 老板给员工发工资,每个人的基本工资都是888,然后还有奖金,然后员工之间有矛盾,有的员工希望比某员 ...

- 1.3 Java中的标识符和关键字

1.标识符 含义:标识符用于给程序中的类.变量.方法命名的符号. 组成:数字(0-9).字母(a-z)(A-Z).下划线(_).美元符号$. 命名规则:1.数字不能够作为命名符号的开头 2.不能够使用 ...

- HDU 4455.Substrings

Substrings Time Limit: 10000/5000 MS (Java/Others) Memory Limit: 32768/32768 K (Java/Others)Total ...