16位CPU多周期设计

16位CPU多周期设计

这个工程完成了16位CPU的多周期设计,模块化设计,有包含必要的分析说明。

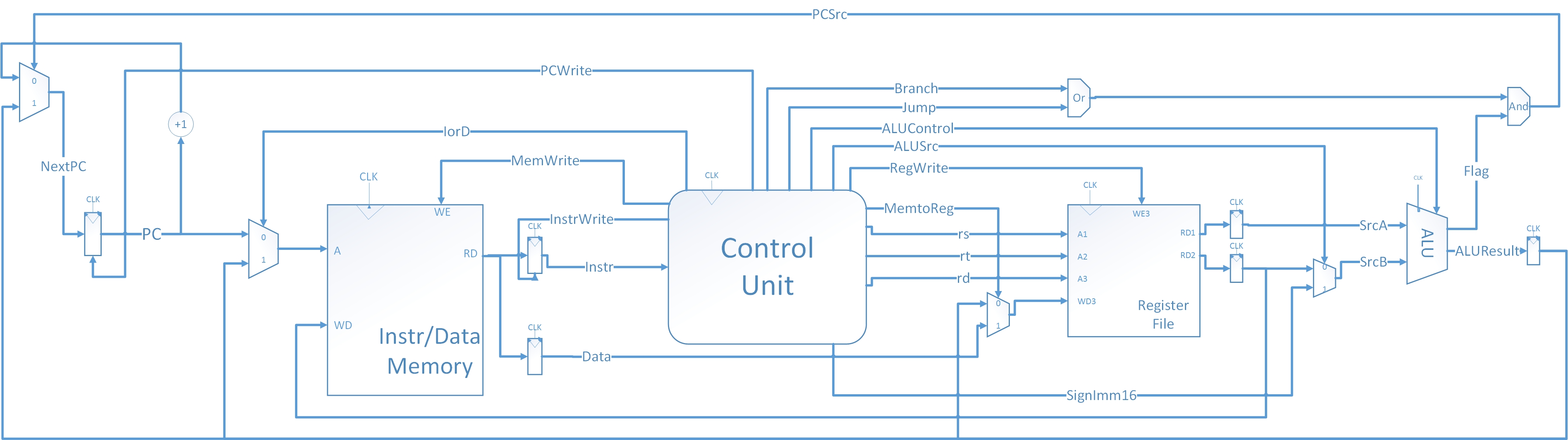

多周期CPU结构图

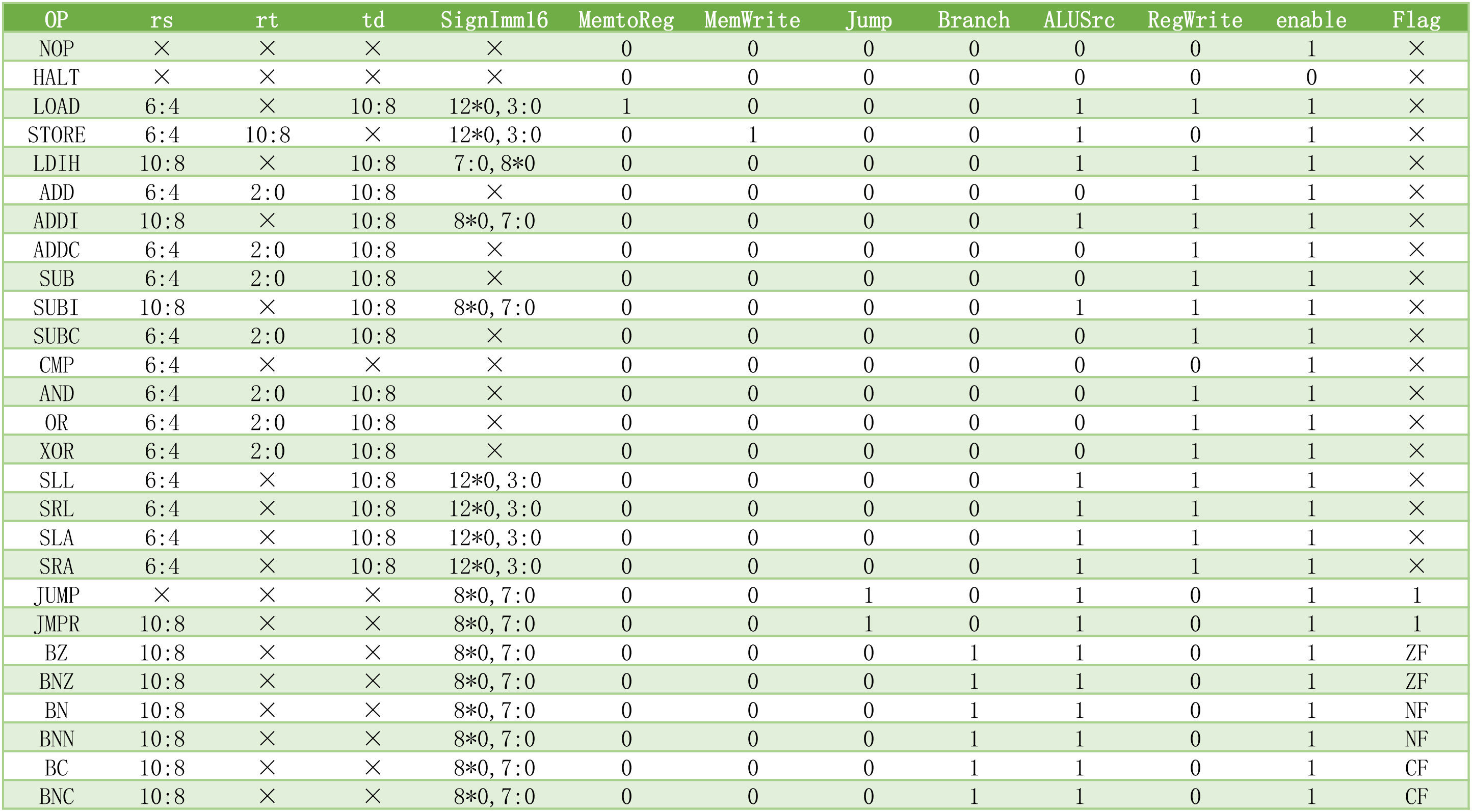

多周期CPU设计真值表

对应某一指令的情况,但仅当对应周期时才为对应的输出,不是组合逻辑

设计思路

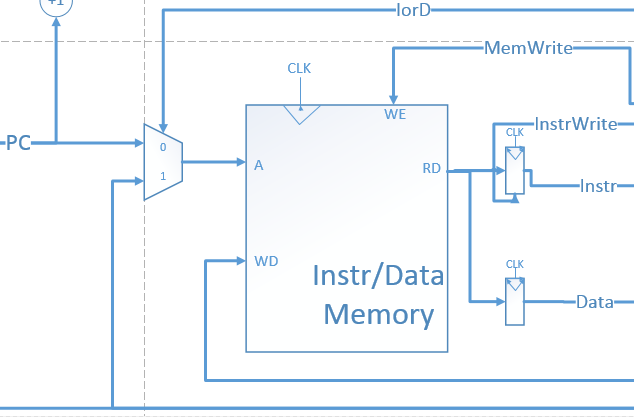

Instruction/Data Memory:

一共有两种模式:

1、 输入8位的地址PC,输出对应内存的16位指令内容

2、 输入8位的地址Address,输出对应内存的DataMemory的内容

输入写入内容WD,当WE写入信号为真的时候,写入到地址为Address的内存里面

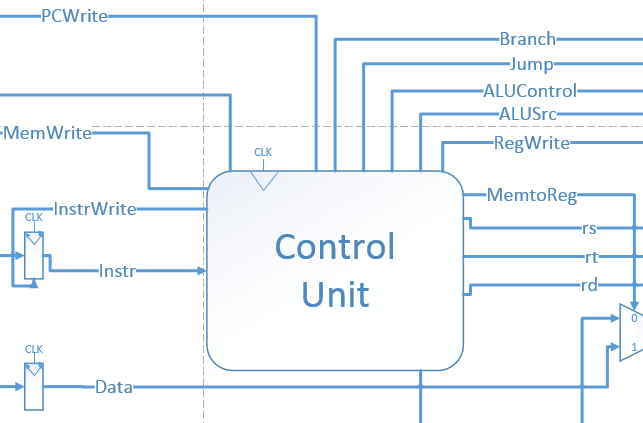

Control Unit

唯一输入16位的指令,根据状态转移图和真值表,输出唯一信号列表,转移方向有指令的高五位Op来决定,并且地址输出集成在控制单元模块中,简化了框图。

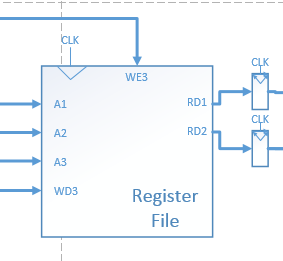

Register File

输入三个地址和写入内容,写入信号,输出两个地址对应的内容

由于单周期内不能一边读一边写,故有一个时钟信号,通过一级缓存,在下一个时钟信号来临时立即写入内存

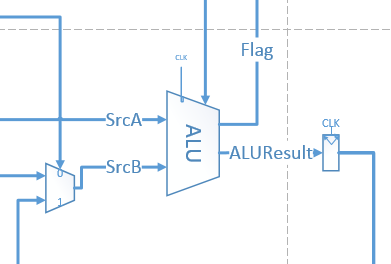

ALU

输入运算数和指令,输出运算结果以及标志位

由于单周期内,标志位并不在当前周期而在下一周期使用,故增加时钟信号,通过一级缓存,在下一个周期时判断使用

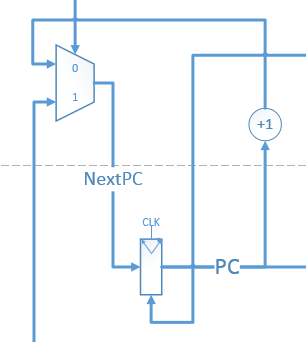

PC-NextPC

根据分支指令,跳转指令和标志位的组合逻辑,决定PC是+1还是到某目标位置,且这里需要一个enable信号进行PC写入控制

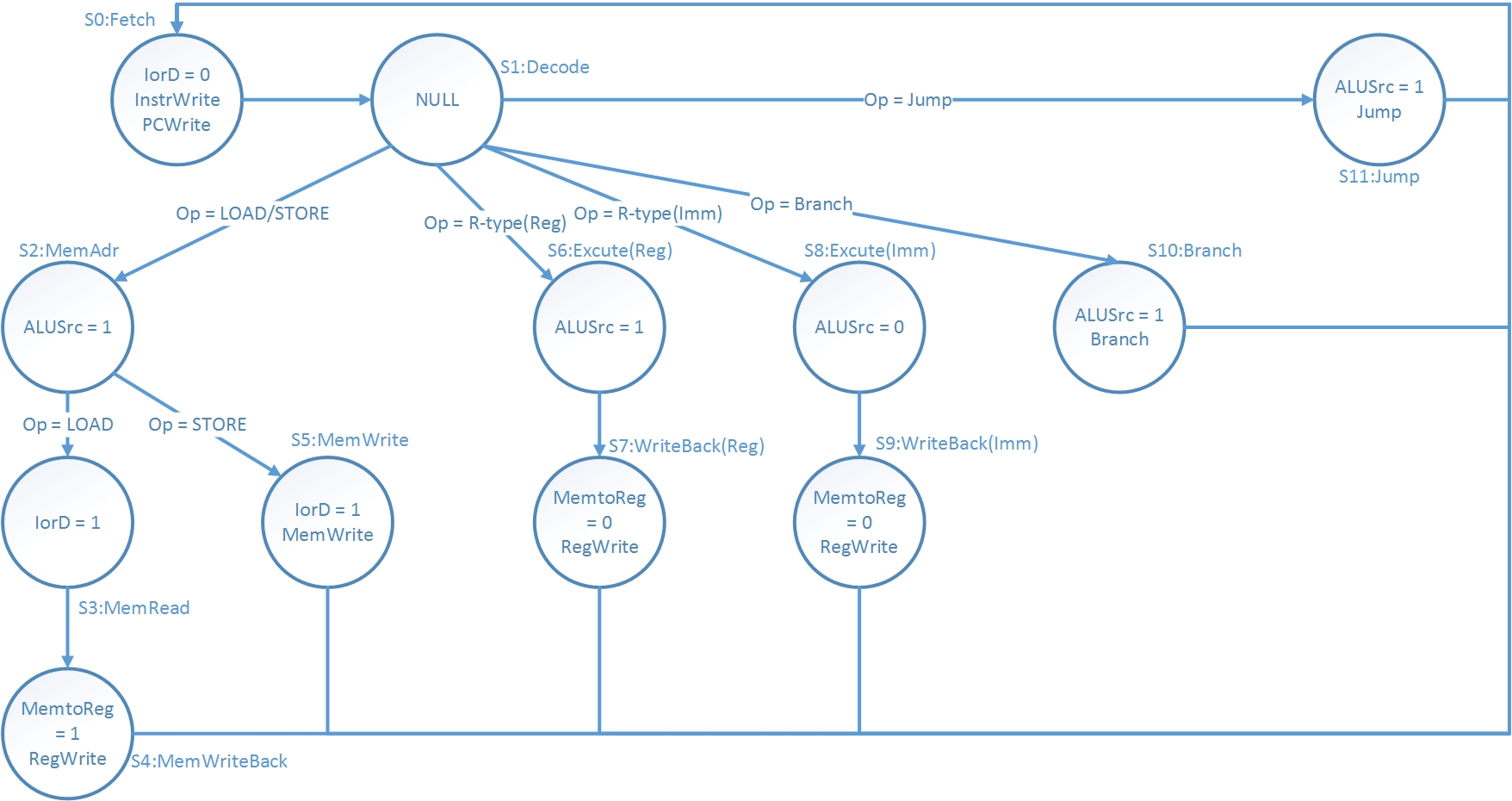

多周期CPU状态转移图

- 写入指令:需要最长的5个周期,读取指令一个周期,指令解码一个周期,寄存器寻址一个周期,读取Data一个周期,写入寄存器一个周期,总共用了五个周期。

- 存储指令:需要4个周期,读取指令一个周期,指令解码一个周期,寄存器寻址一个周期,写入寄存器一个周期,总共用了4个周期。

- 有关寄存器的R-type指令:需要4个周期,读取指令一个周期,指令解码一个周期,寄存器寻址一个周期,写入寄存器一个周期,总共用了4个周期。

- 有关立即数的R-type指令:需要4个周期,读取指令一个周期,指令解码一个周期,寄存器寻址和立即数获得一个周期,写入寄存器一个周期,总共用了4个周期。

- 分支指令:只需要3个周期,读取指令一个周期,指令解码一个周期,运算模块一个周期,总共需要3个周期。

- 跳转指令:只需要3个周期,读取指令一个周期,指令解码一个周期,立即数地址运算一个周期,总共需要3个周期。

特别解释:

i. 状态转移图仅列出了全部的enable信号和select信号,其余和时序逻辑无关的信号均为组合逻辑信号,不在状态转移图中列出,可直接看上面的真值表。

ii. 写入信号只在出现的状态中为真,其余状态均为假

iii. Docode状态里面确定真的不需要改变信号的值,所以为NULL

16位CPU多周期设计的更多相关文章

- verilog实现的16位CPU单周期设计

verilog实现的16位CPU单周期设计 这个工程完成了16位CPU的单周期设计,模块化设计,包含对于关键指令的仿真与设计,有包含必要的分析说明. 单周期CPU结构图 单周期CPU设计真值表与结构图 ...

- verilog实现的16位CPU设计

verilog实现的16位CPU设计 整体电路图 CPU状态图 idle代表没有工作,exec代表在工作 实验设计思路 五级流水线,增加硬件消耗换取时间的做法. 具体每一部分写什么将由代码部分指明. ...

- 16位cpu下主引导扇区及用户程序的编写

一些约定 主引导扇区代码(0面0道1扇区)加载至0x07c00处 用户程序头部代码需包含以下信息:程序总长度.程序入口.重定位表等信息 用户程序 当虚拟机启动时,在屏幕上显示以下两句话: This i ...

- 对所有CPU寄存器的简述(16位CPU14个,32位CPU16个)

32位CPU所含有的寄存器有:4个数据寄存器(EAX.EBX.ECX和EDX)2个变址和指针寄存器(ESI和EDI)2个指针寄存器(ESP和EBP)6个段寄存器(ES.CS.SS.DS.FS和GS)1 ...

- 16位/32位/64位CPU的位究竟是说啥

平时,我们谈论CPU,都会说某程序是32位编译,可以跑在32位机或64位机,或则是在下载某些开源包时,也分32位CPU版本或64CPU位版本,又或者在看计算机组成相关书籍时,特别时谈到X86 CPU时 ...

- Intel X86 32位CPU内存管理----《Linux内核源码情景分析》笔记(一)

Intel X86 32位CPU内存管理 在X86系列中,8086和8088是16为处理器,而从80386开始为32为处理器,80286则是该系列从8088到80386,也就是16位处理器到32位处理 ...

- 梦回----32位CPU和64位CPU的通用寄存器

1 32位Intel的CPU通用寄存器 32位CPU所含有的寄存器有:4个数据寄存器(EAX.EBX.ECX和EDX):2个变址和指针寄存器(ESI和EDI):2个指针寄存器(ESP和EBP):6个段 ...

- 通用32位CPU 常用寄存器及其作用

目录 32位CPU所含有的寄存器 数据寄存器 变址寄存器 指针寄存器 段寄存器 指令指针寄存器 标志寄存器 32位CPU所含有的寄存器 4个数据寄存器(EAX.EBX.ECX和EDX) 2个变址和指针 ...

- verilog实现16位五级流水线的CPU带Hazard冲突处理

verilog实现16位五级流水线的CPU带Hazard冲突处理 该文是基于博主之前一篇博客http://www.cnblogs.com/wsine/p/4292869.html所增加的Hazard处 ...

随机推荐

- CLRS:max_heap and min_heap operation (pseudocode)

//max_heap heap_maximum:return A[1] O(1); Extract_Heap_maximum:swap(A[1],A[heap.size]) adjust ...

- 使用fiddler2抓取手机发出的请求信息

fiddler2 简介:抓包软件,可以替换服务器js,从而实现本地调试 初始化设置: 1.工具——fiddler选项——常规——允许远程计算机连接(打钩) 2.按下图设置 3.设置连接,如 ...

- dell 网络产品线

https://en.wikipedia.org/wiki/Dell_Networking_Operating_System http://topics-cdn.dell.com/pdf/ DNOS ...

- 轻松找回Win7桌面“消失”的IE9图标

打开注册表编辑器(Win+R打开运行窗口,运行regedit命令),依次展开到 [HKEY_CURRENT_USER\Software\Microsoft\Windows\CurrentVersion ...

- 为何要使用Linux

摈弃 Windows 低效率的工作方式,发掘 Linux 身上的 UNIX 气质 我已经半年没有使用 Windows 的方式工作了.Linux 高效的完成了我所有的工作. GNU/Linux 不是每个 ...

- Ajax实现步骤和原理

1.获取ajax异步对象 IE4~IE12 : 使用new ActiveXObject("microsoft.xmlhttp"); 非IE : 使用new XMLH ...

- Tomcat启动过程(一):从BootStrap到EndPonit

Tomcat版本tomcat6.0.44观察catalina.sh文件,启动入口:org.apache.catalina.startup.Bootstrap,该类main方法执行下面三个方法----- ...

- POJ C程序设计进阶 编程题#2:四大湖

编程题#2:四大湖 来源: POJ(Coursera声明:在POJ上完成的习题将不会计入Coursera的最后成绩.) 注意: 总时间限制: 1000ms 内存限制: 65536kB 描述 我国有4大 ...

- SqlServer存储过程

新上线的车管系统,今天要给User添加权限,才发现这个后台加权限简直how to play .. 比如有人申请合肥的关务权限: 1.SITE 是合肥 2.ORG 有B81,P81,S81,M81等 3 ...

- 请注意designer中的NAME field

If you are trying to set the value of a field through PeopleCode and that field happens to be NAME t ...