VIVADO时序约束及STA基础

一、前言

无论是FPGA应用开发还是数字IC设计,时序约束和静态时序分析(STA)都是十分重要的设计环节。在FPGA设计中,可以在综合后和实现后进行STA来查看设计是否能满足时序上的要求。本文阐述基本的时序约束和STA操作流程。内容主要来源于《Vivado从此开始》这本书,我只是知识的搬运工。

二、时序约束与XDC脚本

时序约束的目的就是告诉工具当前的时序状态,以让工具尽量优化时序并给出详细的分析报告。一般在行为仿真后、综合前即创建基本的时序约束。Vivado使用SDC基础上的XDC脚本以文本形式约束。以下讨论如何进行最基本时序约束相关脚本。

1 时序约束首要任务是创建主时钟,主时钟即为时钟引脚进入时钟信号或高速收发器生成时钟。[create_clock]

create_clock -name clk_name -period N -waveform {pos_time neg_time} [get_ports port_name] (划线部分可选)

创建两个异步的主时钟:

create_clock -name clk_a -period 10 [get_ports clk_a]

create_clock -name clk_b -period 15 [get_ports clk_b]

set_clock_groups -asynchronous -group clk_a -group clk_b

当两个主时钟是异步关系,它们生成时钟同样是异步关系:

set_clock_groups -asynchronous -group [get_clocks clk_a -include_generated_clocks] \

-group [get_clocks clk_b -include_generated_clocks]

差分时钟仅约束P端口:

create_clock -name clk -period 10 [get_ports clk_p]

高速收发器生成时钟作为主时钟:

create_clock -name gt0_txclk -period 8 [get_pins GT0/.../TXOUTCLK]

有一种特殊情况无需与具体引脚绑定,即创建虚拟时钟。该约束用于设定输入/输出延迟。需要创建虚拟时钟的场景是输入FPGA的数据由FPGA内部产生时钟采样,如串口通信。

create_clock -name clk_v -period 5

2 创建主时钟后,需要约束生成时钟:[create_generated_clock]

生成时钟分为两种。由PLL MMCM等专用时钟单元生成产生的时钟信号,Vivado会自动产生相关约束。还有一种是自定义生成时钟,一般为逻辑分频得到。

时钟源是时钟端口:

create_generated_clock -name clk_div -source [get_ports clk] -divide_by 2 [get_pins rega/Q] 意思是在rega单元的Q引脚上的时钟信号clk_div是由clk经过2分频得到的生成时钟。

时钟源是引脚:

create_generated_clock -name clk_div -source [get_pins rega/C] -divide_by 2 [get_pins rega/Q]

除了使用-divide_by -multiply_by表示主时钟和生成时钟的频率关系,也可以用 -edges实现更精确的表达:

create_generated_clock -name clk_div -source [get_pins rega/C] -edges {1 3 5} [get_pins rega/Q]

相移关系使用-edge_shift命令描述。

该约束命令还常用于重命名时钟信号:

create_generated_clock -name clk_rename [get_pins clk_gen/.../CLKOUT0]

3 创建时钟组:[set_clock_groups]

a. 异步时钟情况:

set_clock_groups -asynchronous -group clk_a -group clk_b clk_a和clk_b是异步时钟。

b. 物理互斥情况:

create_clock -name clk_a -period 10 [get_ports clk]

create_clock -name clk_b -period 8 [get_ports clk] -add

create_clock -name clk_c -period 5 [get_ports clk] -add

set_clock_groups -physically_exclusive -group clk_a -group clk_b -group clk_c

该种情况仅是为了观察clk引脚时钟信号周期依次为10ns 8ns和5ns时,时序是否收敛。因此这三个时钟物理上不同时存在。

c. 逻辑互斥情况:

set_clock_groups -logically_exclusive\

-group [get_clocks -of [get_pins clk_core/.../CLKOUT0]] -group [get_clocks -of [get_pins clk_core/.../CLKOUT1]]

clkout0和clkout1送入到BUFGMUX中,后续根据sel信号确定选择哪一个作为工作时钟。此时clkout0和clkout1同时存在电路中,但仅有一个会作为后续电路工作时钟,因此逻辑上互斥。

特殊用法:当asynchronous 的group只有一个,说明改组内时钟是同步的,但与其他所以时钟异步。

4 设置伪路径:[set_false_path]

设置伪路径后,不再对特殊路径进行时序分析。特殊路径如测试逻辑、添加同步电路后的跨时钟域路径等。在两个时钟域之间应该相互设置为set_false:

set_false_path -from [get_clocks clk_a] -to [get_clocks clk_b]

set_false_path -from [get_clocks clk_b] -to [get_clocks clk_a]

5 常用时钟相关命令:

report_clocks:查看创建的所有时钟

report_property [get_clocks <clk_name>]:查看时钟clk_name的属性

report_clock_network:查看时钟的生成关系网络

report_clock_interaction:查看时钟交互关系

其中最后一项非常重要,经常被用于查看异步时钟域之间的路径是否安全。若存在不安全路径,需要添加同步、握手或FIFO后,设置为异步时钟组或false_path。

键入该命令后,会生成时钟交互矩阵。对角线是每个时钟内部路径,其他非黑色部分即为存在对应两个时钟的跨时钟域路径。红色部分是非安全路径,若不处理会产生亚稳态。

三、查看时序报告(STA)

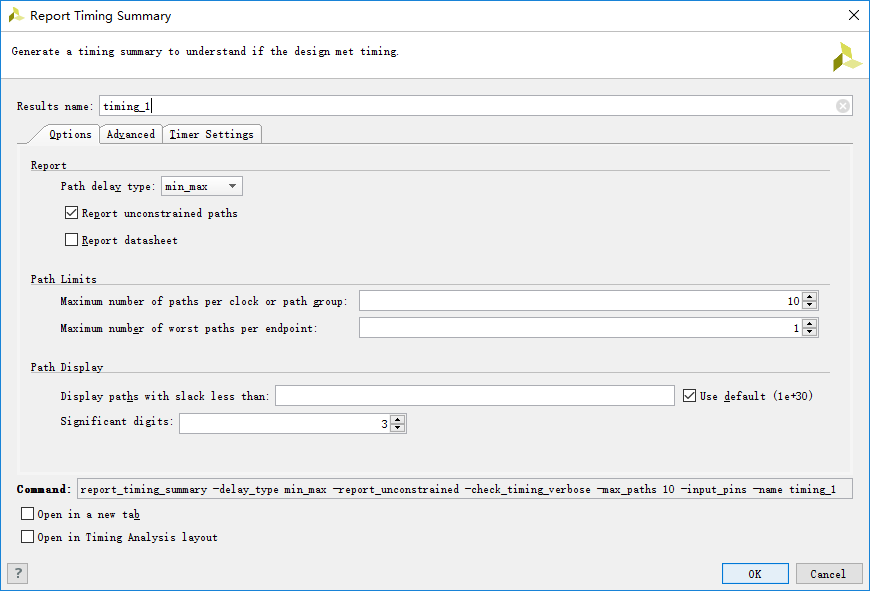

本节以一个有很多时序问题的工程为例进行讲解。在综合后即可打开时序概要查看时序报告。

打开后有如下界面:

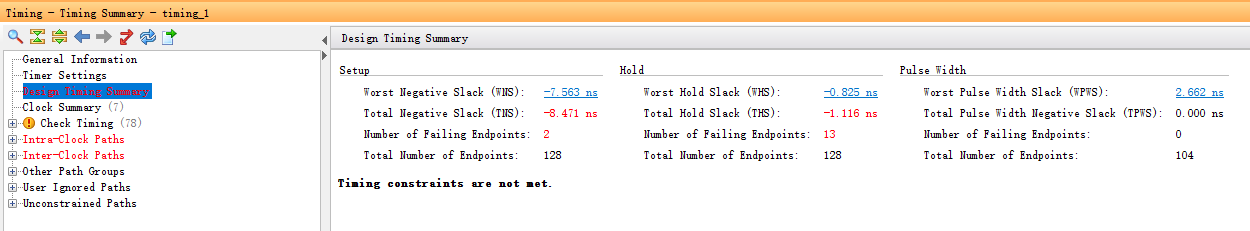

其中Design Timing Summary是时序概况,包括最大延迟分析、最小延迟分析以及脉冲宽度三个部分。其中WNS或WHS为负数,说明当前设计无法满足建立时间或保持时间要求,也就是说数据无法被稳定采样。

Clock Summary内的信息与使用report_clocks TCL脚本调出来的信息相似,包含了全部已创建的时钟信号。Check Timing部分则包含了未被约束的部分,我们可以根据该部分信息进一步添加必要的约束。Intra-Clock Paths和Inter-Clock Paths则分别描述了同步和异步电路时序路径的裕量参数。

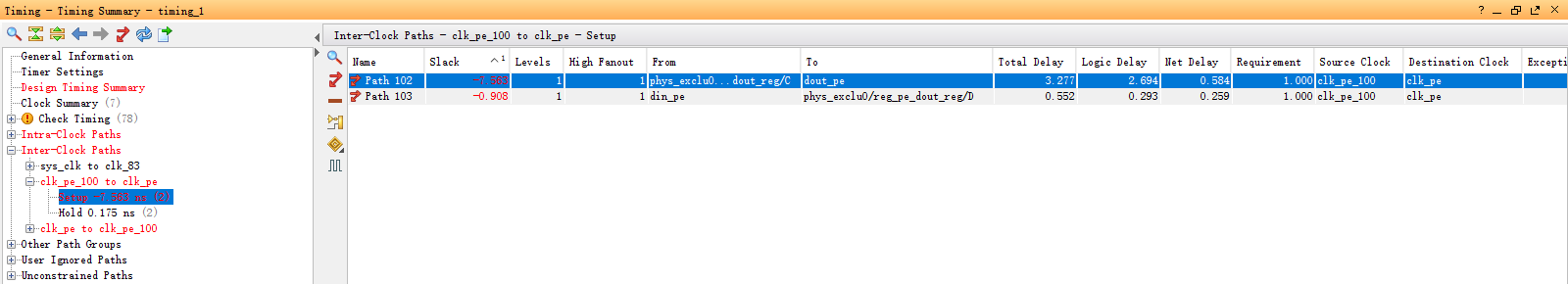

点击WNS或WHS后的数值可以直接找到时序裕量最差的路径:

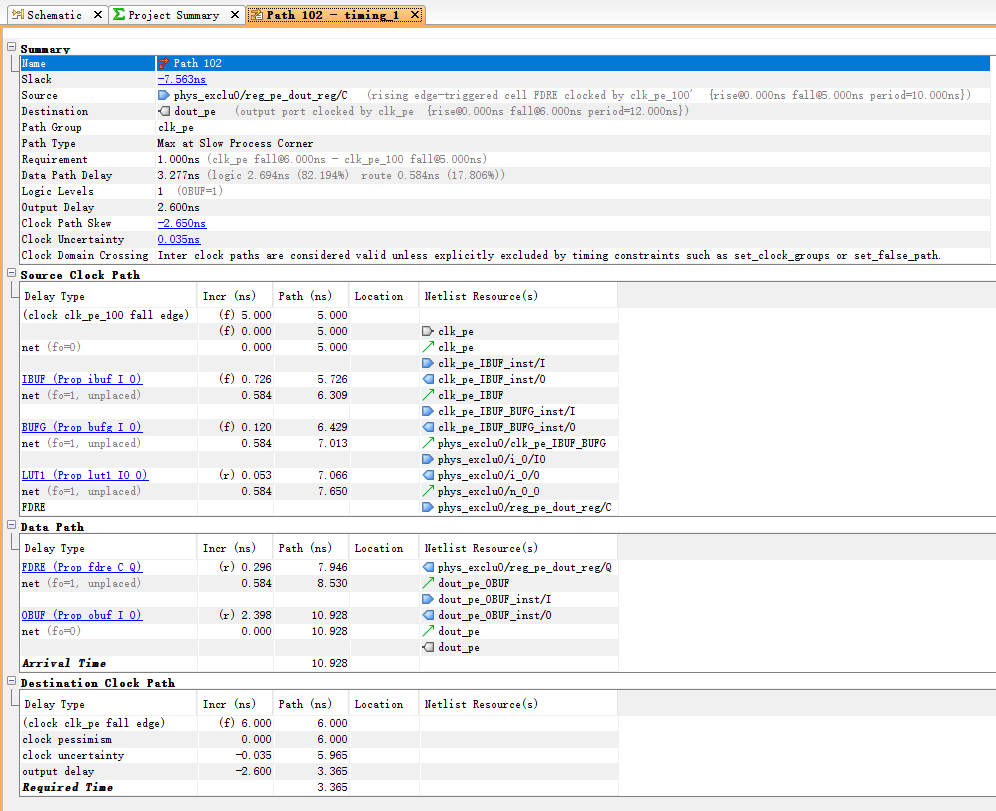

双击路径信息所在行任意位置,界面会跳转到该路径的详细信息界面:

四类时序路径中,除了FPGA输入端口到输出端口这一特殊情况外,其他时序路径均由源时钟路径、数据路径和目的时钟路径三部分构成。上表中各项的具体解释见官方文档UG908.

本文说明了时序约束和STA的关系,基本时序约束情形及相应的XDC脚本。之后简单介绍了如何在VIVADO中查看时序报告来分析时序问题。后续会以网络通信中常见的RGMII接口设计实例阐述I/O延迟约束部分。

VIVADO时序约束及STA基础的更多相关文章

- 【转载】【时序约束学习笔记1】Vivado入门与提高--第12讲 时序分析中的基本概念和术语

时序分析中的基本概念和术语 Basic concept and Terminology of Timing Analysis 原文标题及网址: [时序约束学习笔记1]Vivado入门与提高--第12讲 ...

- FPGA基础学习(5) -- 时序约束(实践篇)

目录 1. 理论回顾 2. 时间裕量 3. 最大延迟和最小延迟 4. 案例分析 参考文献: 距离上一篇有关时序的理论篇已经有一段时间了(可以参考博文FPGA时序约束--理论篇),实际上此段时间,甚至到 ...

- FPGA基础学习(4) -- 时序约束(理论篇)

在FPGA 设计中,很少进行细致全面的时序约束和分析,Fmax是最常见也往往是一个设计唯一的约束.这一方面是由FPGA的特殊结构决定的,另一方面也是由于缺乏好用的工具造成的.好的时序约束可以指导布局布 ...

- Tcl与Design Compiler (十)——其他的时序约束选项(一)

本文属于原创手打(有参考文献),如果有错,欢迎留言更正:此外,转载请标明出处 http://www.cnblogs.com/IClearner/ ,作者:IC_learner 之前讲了基本的时序路径 ...

- Quartus中添加时序约束

1.sdc文件也是要添加到Quartus 软件中,这样在执行Read SDC File命令时才能读到相应的文件. 2.在TimeQuest打开的条件下,重新编译工程之后要Update Timing N ...

- 【转载】如何在FPGA设计环境中添加加时序约束

转自:http://bbs.ednchina.com/BLOG_ARTICLE_198929.HTM 如何在FPGA设计环境中加时序约束 在给FPGA做逻辑综合和布局布线时,需要在工具中设定时序 ...

- Tcl与Design Compiler (十一)——其他的时序约束选项(二)

本文如果有错,欢迎留言更正:此外,转载请标明出处 http://www.cnblogs.com/IClearner/ ,作者:IC_learner 前面介绍的设计都不算很复杂,都是使用时钟的默认行为 ...

- FPGA时序约束——理论篇

在FPGA 设计中,很少进行细致全面的时序约束和分析,Fmax是最常见也往往是一个设计唯一的约束.这一方面是由FPGA的特殊结构决定的,另一方面也是由于缺乏好用的工具造成的.好的时序约束可以指导布局布 ...

- FPGA时序约束的几种方法 (转)

FPGA时序约束的几种方法 对自己的设计的实现方式越了解,对自己的设计的时序要求越了解,对目标器件的资源分布和结构越了解,对EDA工具执行约束的效果越了解,那么对设计的时序约束目标就会越清晰,相应地, ...

随机推荐

- PAT1124:Raffle for Weibo Followers

1124. Raffle for Weibo Followers (20) 时间限制 400 ms 内存限制 65536 kB 代码长度限制 16000 B 判题程序 Standard 作者 CHEN ...

- cmd登录远程Oracle数据库

在cmd中输入 user/password@Ip:port/sid 例如: laoda/123@192.168.4.161:1521/orcl laoda是用户名,123是密码.

- 影响 MySQL Server 性能的相关因素

MySQL 最多的使用场景是WEB 应用,那么我们就以一个WEB 应用系统为例,逐个分析其系统构成,进行经验总结,分析出数据库应用系统中各个环境对性能的影响. 商业需求对性能的影响 这里我们就拿一个看 ...

- HTTP和SOAP完全就是两个不同的协议

HTTP只负责把数据传送过去,不会管这个数据是XML.HTML.图片.文本文件或者别的什么.而SOAP协议则定义了怎么把一个对象变成XML文本,在远程如何调用等,怎么能够混为一谈. ...

- Linux时间子系统之(一):时间的基本概念

专题文档汇总目录 Notes:Linux时间基准点:Linux时间和broken-down time(struct tm):不同精度的时间表示time_t.timeval.timespec. 原文地址 ...

- 解决Kali用户名密码正确但是无法登陆的问题

本文由荒原之梦原创,原文链接:http://zhaokaifeng.com/?p=684 前言: 用户名和密码都正确,但是登陆Kali的时候总是提示用户名或密码错误,无法登陆,本文介绍一种解决办法. ...

- Scrapy 1.4 文档 01 初窥 Scrapy

初窥 Scrapy Scrapy 是用于抓取网站并提取结构化数据的应用程序框架,其应用非常广泛,如数据挖掘,信息处理或历史存档. 尽管 Scrapy 最初设计用于网络数据采集(web scraping ...

- PuTTY/终端使用复制、粘贴

Putty鼠标按钮选项 通过鼠标按钮选项可以控制鼠标来进行复制.粘贴操作,选项包括: 1.Windows选项: 2.混合模式(系统默认选项): 3.Xterm模式. 以上是三种模式选项的简单介绍,下面 ...

- Dreamweaver无法启动:xml parsing fatal error..Designer.xml错误解决方法

xml parsing fatal error:Invalid document structure,line:1,file:C:\Documents and Settings\Administrat ...

- linux下如何配置yum源

first:挂载本地镜像文件(挂载:意为将某个文件放置在系统的一个目录下) mkdir /media/cdrom #新建镜像文件挂载目录 cd /usr/local/src ...