Timing path

Timing path:从register clock/input port开始,经过一些combinational logic,终止在register data/output port。

PT以path grouping为单位来分析和报告timing。

DC,每个path group可以指定一个weight,来尽力做design optimizaiton,但是这个weight在PT中并没有用。

每个create clock命令都会生成一个对应的path group。

PT中还有自己的default group:clock_gating_default**:path以combinational element为终点。

async_default*:path以async的preset和clear为终点。

*default*:剩下的所有clock,如以output为终点的clock。

也可以自己定义group_path:group_path -name out1bus -to [get_ports OUT_1*] 然后可以报告该path group的timing。

report_timing命令中的属性:

Number of paths:-nworst 显示每个end point最worst的N条path,-max_paths 显示整个group的worst path的个数

Types of paths:-path_type full -delay_type max

Amount of detail

Startpoints,endpoint

-path_type full_clock/full_clock_expanded 显示完整的data path和clock path

full 显示完整data path

short 只显示一条data path的startpoint和endpoint

-transition_time 报告路径的transition time

-capacitance 报告路径的capacitance

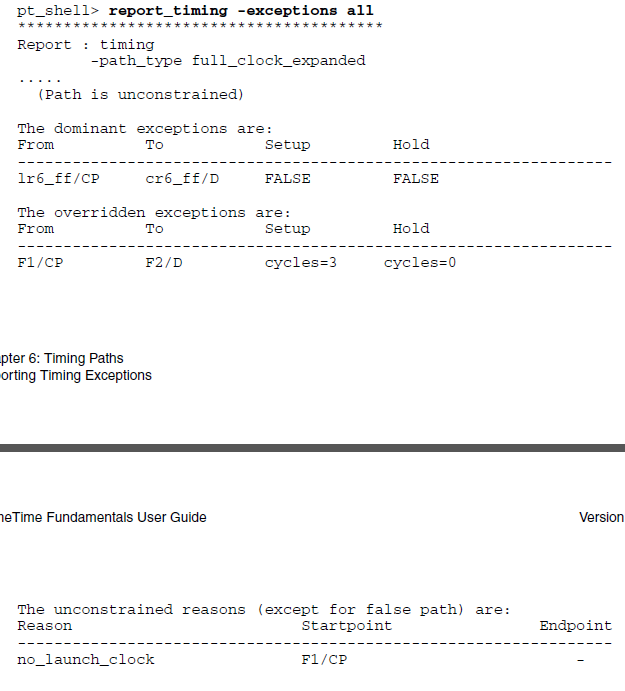

对于exception timing的rpt:

1)-exceptions dominant 报告路径中的exception constrained

2)-exceptions overridden 报告路径中被覆盖的exception constrained

3)-exceptions all 报告所有的exception path,包括unconstrained startpoint 和unconstrained endpoint

exceptions path的三种属性:方便进行filter

dominant_exception timing path的类型:false path, min_delay, max_delay, multicycle_path

endpoint_unconstrained_reason:no_capture_clock, dangling_end_point(floating point no timing constraints), danin_of_disable(disable timing arc)

startpoint_unconstrained_reason:no_launch_clock,dangling_start_point,fanout_of_disable

filter_collection $path {defined(dominant_exception)}

filter_collection $path {undefined(dominant_exception)}

get_timing_path更好的删选timing path

set x [get_timing_paths -from A -through B -to C]

report_timing $x -exceptions all

Path Sepecification Methods

-from $startpoint

-to $endpoint

-through

report_timing -from [get_clocks ...] -though $startpoint

report_timing -through $endpoint -to [get_clocks ...]

report_timing -through {B1 B2}

更加精细的方式:

-rise_from/-rise_to

-fall_from/-fall_through...

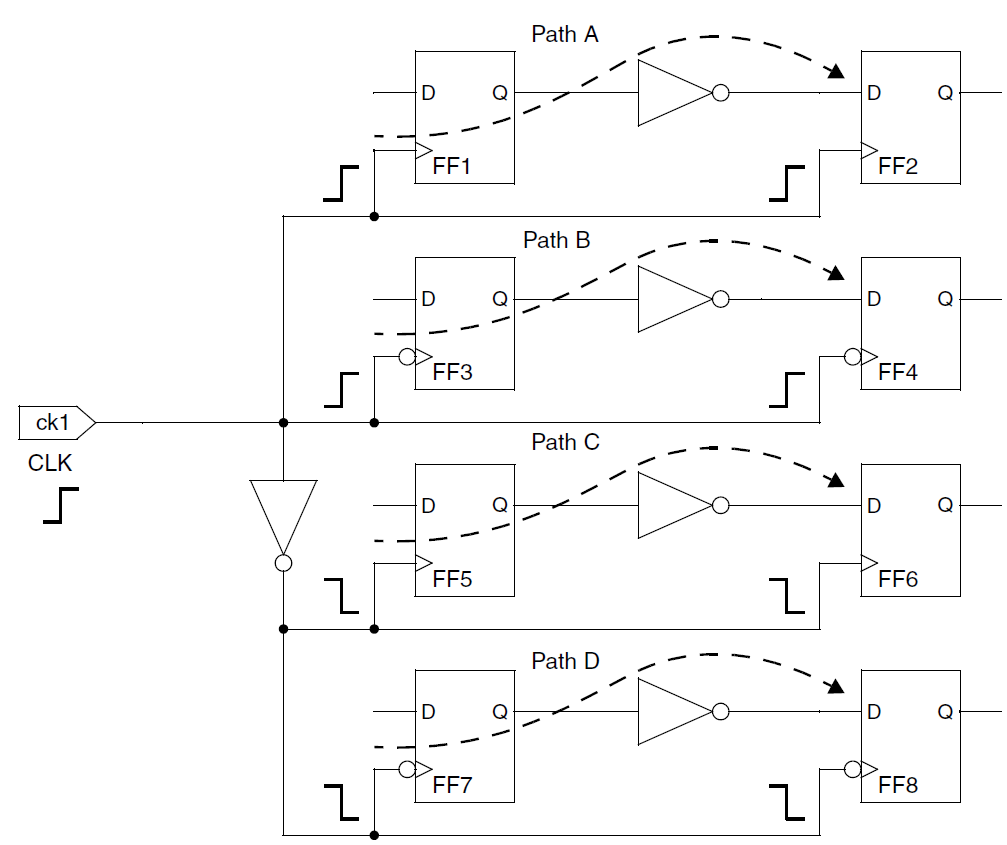

set_false_path -to [get_clocks CLK] :取以CLK为终点的timing path,data端的FF的clock是CLK

path:a,b,c,d有效

set_false_path -rise_from [get_clocks CLK] :以CLK为起点,且data端以clock的rising edge来触发

path:a,d有效

report_timing -rise_from [get_clock clk] -nworst 100

对于delay的report:

report_delay_calculation -from BLK1/A -to BLK1/z

Timing path的更多相关文章

- standard cell timing model

standard cell timing model 主要包括两方面的信息: Cell Delay calculation Output Transition calculation 首先,cel ...

- 读懂timing report

三部分:表头/launch path /capture path 1.表头 1) 工具版本信息:如示例中的18.10-p001,对某个具体项目timing signoff 工具的版本最好保证一致: 操 ...

- clock

Prime Time中的clock分析包括: 1)Multiple clocks,clock from port/pin,virtual clock. 2)Clock network delay an ...

- (数字IC)低功耗设计入门(六)——门级电路低功耗设计优化

三.门级电路低功耗设计优化 (1)门级电路的功耗优化综述 门级电路的功耗优化(Gate Level Power Optimization,简称GLPO)是从已经映射的门级网表开始,对设计进行功耗的优化 ...

- IN2REG group 的时序分析

针对 IN2REG 的 timing group,其 timing 模型是假设 input pin 外面有一个虚拟的reg(如图中的 reg1),这个虚拟reg的 clock 是 virtual cl ...

- clock gating check

在 sta 分析时,经常会碰到 clock gating cell (一般是 ICG cell 或者 latch)引起的 violation,这种 violation 很常见,而且往往很难修. 为什么 ...

- STA分析(七) sdc

STA分析前的环境设置,包括:setup clocks,specifying IO characteristics 1)定义一个master clock:create_clock -name .. - ...

- STA分析(一) setup and hold

timing check可以分为Dynamic Timing Analysis(Post_sim)和Static Timing Analysis STA:可以分析的很全面:仿真速度也很快:可以分析控制 ...

- FPGA静态时序分析基础

FPGA静态时序分析基础 基本概念 Skew: 时钟偏移 Skew表示时钟到达不同触发器的延时差别,Tskew = 时钟到达2号触发器的时刻 - 时钟到达1号触发器的时刻. Jitter: 时钟抖动 ...

随机推荐

- Java_Java Compiler 应用实例

转自:http://hejiangtao.iteye.com/blog/1399122 一直在用JDK1.5, 一直搞不清楚JDK1.6有啥特性, 就翻了翻, 发现这个Compiler API(JSR ...

- HttpClient_httpclient 4.3.1 post get的工具类

package com.ryx.util; import java.util.ArrayList; import java.util.List; import java.util.Map; impor ...

- Express 路由

路由 路由是指如何定义应用的端点(URIs)以及如何响应客户端的请求. 路由是由一个 URI.HTTP 请求(GET.POST等)和若干个句柄组成,它的结构如下: app.METHOD(path, [ ...

- 处理海量数据的高级排序之——希尔排序(C++)

希尔算法简介 ...

- HDU 4006 优先队列

The kth great number Time Limit: 2000/1000 MS (Java/Others) Memory Limit: 65768/65768 K (Java/Oth ...

- Redis菜鸟汇总

1.是完全开源免费的,用C语言编写的,遵守BSD协议,是一个高性能的(key/value)分布式内存数据库,基于内存运行并支持持久化的NoSQL数据库,是当前最热门的NoSql数据库之一,也被人们称为 ...

- BizTalk开发系列(二十七) 异常管理中的数据编码

在BizTalk的异常管理解决方案中.大部分是通过订阅相关的升级属性来接收消息,并在自定义的流程或发送端口进行处理.但不管怎样,一般会定义统一的 错误消息Schema,这样不仅可以让我们通过异常信息快 ...

- 关闭SSMS的事务自动提交,改为手动提交

SQLServer 2005-2008-2012使用Oracle时,默认是手动提交.而SQLServer2005中,默认是自动提交,但是SQLServer支持配置. 方法: 用SSMS连接到SQL S ...

- HDU 1565&1569 方格取数系列(状压DP或者最大流)

方格取数(2) Time Limit: 10000/5000 MS (Java/Others) Memory Limit: 65536/32768 K (Java/Others) Total S ...

- unity assert server 与 cache server

Asset server 其实就是unity提供的版本控制工具,不过我们都转到P4V了,上午尝试了一下,如果小团队使用还是不错的,使用过程大致如下,具体的还是要大伙去官网看喽 服务器安装文件下载: h ...