关于testbench

区别与verilog HDL代码,主要留意以下内容:

1,语言本身支持的特征和可综合的代码是两回事,不是所有verilog语言都可以转化为硬件的。

2,testbench作为top module,不需要任何输入和输出。

3,在testbench module中将要测试的模块例化为dut(名字可以任起),input要是reg类型,output要是wire类型,inout是reg。

4,initial和always是同时执行的,只是initial只执行一次。

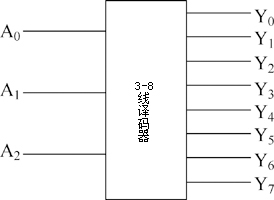

一.38译码器框图

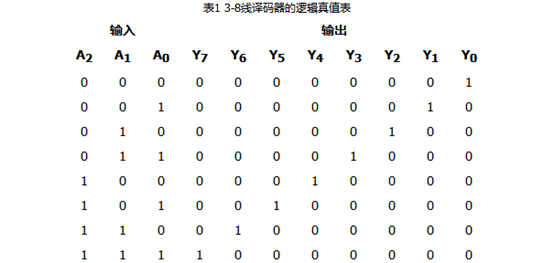

二、真值表

创建工程:

按照真值表定义编写Verilog程序:

module my_38(a,b,c,out);

input a;

input b;

input c;

output reg [7:0]out; //定义一个8位的位宽.只要是在always块中进行赋值的都要定义为reg类型。

always@(a,b,c)

begin

case ({a,b,c}) //{}位为位拼接,将信号拼接成一个三位的信号

3'b000: out=8'b0000_0001;

3'b001: out=8'b0000_0010;

3'b010: out=8'b0000_0100;

3'b011: out=8'b0000_1000;

3'b100: out=8'b0001_0000;

3'b101: out=8'b0010_0000;

3'b110: out=8'b0100_0000;

3'b111: out=8'b1000_0000;

endcase

end

endmodule

编写testbench测试文件:

`timescale 1ns/1ns

module

my38_tb;

reg a,b,c;

wire [7:0]

out my3_8 u1(

.a(a),

.b(b),

.c(c),

.out(out)); //顶层例化

initial begin

a=0;b=0;c=0;

#200;

a=0;b=0;c=1;

#200;

a=0;b=1;c=0;

#200;

a=0;b=1;c=1;

#200;

a=1;b=0;c=0;

#200;

a=1;b=0;c=1;

#200;

a=1;b=1;c=0;

#200;

a=1;b=1;c=1;

#200;

$stop;

end

endmodule

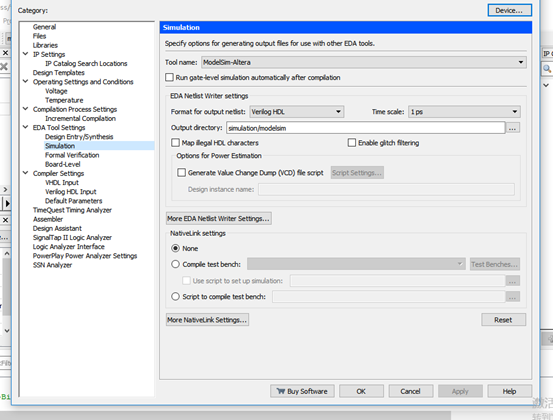

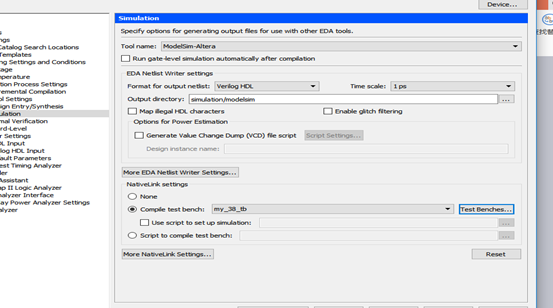

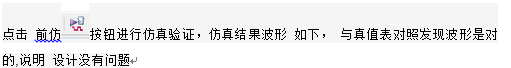

将testbench文件链接到仿真工具

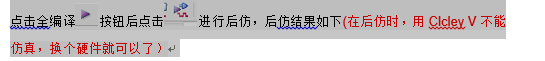

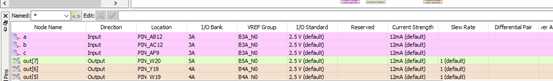

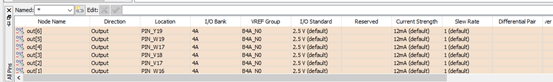

分配引脚

点击全编译按钮后,上电链接开发板,点击programmer,将系统生成的.sof文件烧写到开发板中。

本次实验中,testbench是用initial块给信号赋初值,initial块执行一次,

首先在写testbench时,应注意名称要和自己待仿真的工程名称要对应,比如自己的待仿真文件名称叫my_38,那么对于teshbench的名称则取一个叫my_38_tb,在书写testbench module name则取名叫my_38_tb,这样对于自己有好处,以免自己找不到自己写的文件。

关于testbench的更多相关文章

- UVM Top Testbench

top testbench在top_tb中包含进所有的文件,将DUT放在top_tb中(例化DUT),连接好各个端口,提供clk时钟和rst_n复位信号.最主要的是要给组件中的虚接口设置接口,一般是给 ...

- VHDL TestBench基础(转)

TestBench的主要目标是: 实例化DUT-Design Under Test 为DUT产生激励波形 产生参考输出,并将DUT的输出与参考输出进行比较 提供测试通过或失败的指示 TestBench ...

- VHDL的testbench的编写(转)

大多数硬件设计人员对verilog的testbench比较熟悉,那是因为verilog被设计出来的目的就是为了用于测试使用,也正是因为这样verilog的语法规则才被设计得更像C语言,而verilog ...

- quartus II 自动生成testbench

如果自己不想写这些testbench的这些固定格式,可以在quartus里自动生成testbench文件的模板,然后往里面写信号就行了 步骤:processing->start->star ...

- testbench中将外部数据引入输出的方法(转载)

在进行HDL的仿真测试时,除了用较为直观的波形仿真图像以外,通过编写测试文件testbench进行仿真并将仿真结果保存在对应的文件,显得尤为重要.文件的操作主要用到读和写两种操作. 1. 读操作 读操 ...

- 关于使用ModelSim中编写testbench模板问题

对于初学者来说写Testbench测试文件还是比较困难的,但Modelsim和quartus ii都提供了模板,下面就如何使用Modelsim提供的模板进行操作. Modelsim提供了很多Testb ...

- IIC模块TestBench的书写方法

今天在看黑金AX309FPGA开发板自带教程中的EEPROM那一章,考虑如何写其中iic_com模块的TestBench,难点在于1. 该模块存在一个inout型的端口信号:2. 时序较为复杂,不可能 ...

- Testbench(转)

本来还打算自己写下对Testbench的理解,后来发现百度百科名片解释得很好,所以就直接转了. 原文百度百科链接:http://baike.baidu.com/link?url=dxzsOAs32IE ...

- vcs+Makefile实现简单的testbench

网络上找的文章,实现了一遍. 步骤如下: 1. 创建verilog代码, 包括8位加法器代码和testbench代码. adder8.v module adder8 ( input clk, inpu ...

- Verilog TestBench Coding Style

Abtract 关于编写testbench的一些经验总结心得. Introduction 1.基本的Testbench结构 1)常用的编码结构 `timescale 1 ns / 1 ps ...

随机推荐

- C#最基本的Socket编程

示例程序是同步套接字程序,功能很简单,只是客户端发给服务器一条信息,服务器向客户端返回一条信息,是一个简单示例,也是一个最基本的socket编程流程. 简单步骤说明: 1.用指定的port, ip 建 ...

- nunjucks模板设计一个页面

使用nunjucks代替原来的ejs,因为这个更强大,是node中主流的模板引擎 nunjucks官网 配置使用 nunjucks 模板引擎 nunjucks 模板引擎没有对模板文件名的后缀名做特定限 ...

- python全栈学习 day03

换行符: \n 制表符: \t 字符串截取:顾头不顾尾 s[首:尾:步长] 首--->尾走向 和 步长方向一致 s[0:4:2] s[4:0:-2] a = "qwertyui&quo ...

- luoguP5219 无聊的水题 I 多项式快速幂

有一个幼儿园容斥:最大次数恰好为 $m=$ 最大次数最多为 $m$ - 最大次数最多为 $m-1$. 然后来一个多项式快速幂就好了. code: #include <cmath> #in ...

- 关于Hosts与network的异同之处

1.hosts文件,路径:/etc/hosts,此文间是在网络上使用的,用于解析计算机名称和IP地址的映射关系,功能相当于windows下面的c:\windows\system32\drivers\e ...

- Python标准库之hashlib模块与hmac模块

hashlib模块用于加密相关的操作.在Python 3.x里代替了md5模块和sha模块,主要提供 SHA1.SHA224.SHA256.SHA384.SHA512 .MD5 算法.如果包含中文字符 ...

- Pwnable.kr

Dragon —— 堆之 uaf 开始堆的学习之旅. uaf漏洞利用到了堆的管理中fastbin的特性,关于堆的各种分配方式参见堆之*bin理解 在SecretLevel函数中,发现了隐藏的syste ...

- 《剑指Offer》各面试题总结

目录 前言 面试题4 二维数组的查找 面试题5:替换空格 面试题6:从尾到头打印链表 面试题7:重建二叉树 面试题8:二叉树的下一个节点 面试题9:用两个栈实现队列 面试题10:斐波那契数列 面试题1 ...

- TensorFlow入门(矩阵基础)

1.placeholder 占位符 可以通过run方法传入值 测试代码如下: # encoding:utf-8 import tensorflow as tf # placeholder 占位符 可以 ...

- 1304F2 - Animal Observation (hard version) 线段树or单调队列 +DP

1304F2 - Animal Observation (hard version) 线段树or单调队列 +DP 题意 用摄像机观察动物,有两个摄像机,一个可以放在奇数天,一个可以放在偶数天.摄像机在 ...