ARMV8 datasheet学习笔记4:AArch64系统级体系结构之存储模型

1.前言

关于存储系统体系架构,可以概述如下:

|

存储系统体系结构的形式 |

VMSA |

|

存储属性 |

|

2. 存储系统体系结构

2.1. 地址空间

|

指令地址空间溢出 |

指令地址计算((address_of_current_instruction) + (size_of_executed_instruction))超过0xFFFF FFFF FFFF FFFF,PC变成不可知 |

2.2 Cache支持

- Caches的一般行为

(1)Cache中已解锁的项不会一直驻留在cache;

(2)Cache中锁定的项会保证会一直在cache中;

(3)任何时候具有cacheable属性的内存在当前异常级别或更高异常级别都可以分配到cache;

(4)不具有cacheable属性的内存不会分配到cache;

(5)一个cache项的释放会写回内存;

- Cache identification

|

Cache维护指令 |

(1) 影响整个cache,如IC IALLU; (2) 对某个地址的操作,如IC IVAU; (3) 对set/way的操作,如DC ISW |

|

Cache identification registers |

(1) Cache type寄存器(CTR_EL0) 定义了最小的指令cache line长度; 定义了最小的数据cache line长度; L1 Cache索引和tag策略 (2) single cache level ID寄存器(CLIDR_EL1) 实现了哪几级cache; 待续 (3) single cache size selection寄存器 待续 (4) cache size identification寄存器 是否支持写透、回写、读分配和写分配; 映射方式、sets/ways等 |

- Cacheablity,cache分配,cache瞬态

|

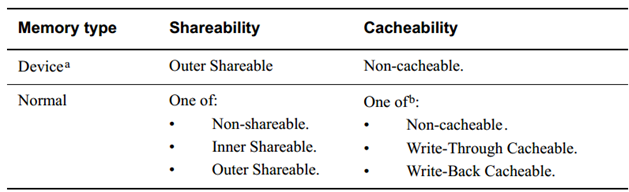

Cacheablity |

cacheablity只适用于normal memory,内存位置可定义为内部cache(如各PE内部的L1)或外部cache(各PE共享的L2);所有的device memory都作为non-cacheablity; cacheablity属性包含non-cacheablity;写透;写回。 |

|

Cache allocate hints |

待续 |

|

Cache transient hints |

待续 |

- Enable/disable内存的caching访问

- Reset的cache行为

(1)reset到自定义状态的所有cache可能是未知的;

(2)cacheablity控制域强制所有内存作为non-cacheablity

(3)在cache被使能前,cache初始化时必须被invalidate

(4)如(2)所述,reset所有的内存都被作为non-cacheablity,如果仍然允许cahce hit,则需:(1)提供确保cache正确初始化的机制;(2)清楚记录cache初始化;

(5)ARM建议任何时候需要无效cache时都要基于ARMV8 cache维护指令???

- Non-cacheable访问和指令cache

- 关于ARMV8的cache维护

|

术语 |

Level:cache的级别; |

|

Set:由多个连续的cache line组成一个组(set); Way: 每个set中冲突的备选表项的数目; |

|

|

(1)Clean:为确保更新到cache中的内容flush到内存; (2)Invalidate:确保内存中的修改,能够重新加载到cache; (3)Clean and invalidate:clean指令后跟一个invalidate指令,针对的是同一访问地址; |

|

|

(1)PoU(Point of Unification):对所有的PE可以观察到一致拷贝的点; (2)PoC(Point of Coherence):对系统中所有的agent可以观察到一致拷贝的点; |

|

|

(1)LoC(Level of Coherence):定义了 整个系统 clean或invalidate PoC时所要clean或invalidate的最后一级cache级别号,如:PoU为Level4,则LoC为3,执行clean和invalidate后会清空L1,L2, L3; (2)LoUU(Level of Unification, uniprocessor):定义了 PE clean或invalidate PoU时所要clean或invalidate的最后一级cache级别号; (3)LoUIS(Level of Unification, Inner Shareable):定义了 内部共享域 clean或invalidate PoU时所要clean或invalidate的最后一级cache级别号; |

|

|

ARMV8 cache层级抽象 |

操作VA的cache维护指令 |

|

操作set/way的cache维护指令 |

- Cache维护指令

|

指令cache维护指令 |

|

|

数据cache维护指令 |

|

|

EL0 cache维护指令的使能配置 |

|

|

Cache维护指令的行为 |

没有限制cache维护指令的行为,每个cache位置都可能被清空或无效 |

|

操作VA到PoU的影响 |

会影响共享域内的其它PE |

|

所有set/way维护指令的影响 |

只影响到运行指令的PE |

|

虚拟化和安全性维护指令的影响 |

每个安全状态有自己的物理地址空间,cache与物理地址关联 |

|

边界条件 |

维护指令会强制所有的内存访问为non-cache??? |

|

数据和指令cache维护指令的执行顺序和完成 |

|

|

运行cache维护指令 |

- Data cache zero指令

- cache lockdown

一个cache lock 可保证cache 中的内容一直被保留

- System level caches

|

不是体系结构定义的cache,不受体系结构定义的维护指令管理,主要包括三类: |

|

- 分支预测

|

ARMV8没有定义任何分之预测指令,如果体系结构中分支预测指令对所有agent是可见的,则cache维护指令也要与之适配 |

2.3 External abort

|

External abort |

存储系统中MMU和debug逻辑检测到的错误除外的其它错误,主要位于SOC外部 |

|

取指abort |

|

|

Data read/write abort |

|

|

External abort分类 |

|

|

奇偶校验错误/ECC错误报告 |

3. 参考文档

[1] DDI0487A_k_armv8_arm_iss10775.pdf

ARMV8 datasheet学习笔记4:AArch64系统级体系结构之存储模型的更多相关文章

- ARMV8 datasheet学习笔记4:AArch64系统级体系结构之编程模型(1)-EL/ET/ST

1.前言 ARMV8系统级编程模型主要包括异常级别.运行状态.安全状态.同步异常.异步异常.DEBUG 本文主要对系统级编程模型做一个概要介绍 2. 异常级别 2.1 Exception level概 ...

- ARMV8 datasheet学习笔记4:AArch64系统级体系结构之编程模型(4)- 其它

1. 前言 2.可配置的指令使能/禁用控制和trap控制 指令使能/禁用 当指令被禁用,则这条指令就会变成未定义 指令Trap控制 控制某条或某些指令在运行时进入陷阱,进入陷阱的指令会产生trap异常 ...

- ARMV8 datasheet学习笔记4:AArch64系统级体系结构之编程模型(3)- 异常

1.前言 本文介绍异常相关内容,包括异常类型,异常进入,异常返回,异常层次结构,异常的路由等 2. RESET ARMV8体系结构支持两种类型的RESET Cold reset:Reset PE所有 ...

- ARMV8 datasheet学习笔记4:AArch64系统级体系结构之编程模型(2)- 寄存器

1. 前言 2. 指令运行与异常处理寄存器 ARM体系结构的寄存器分为两类: (1)系统控制和状态报告寄存器 (2)指令处理寄存器,如累加.异常处理 本部分将主要介绍如上第(2)部分的寄存器,分为AA ...

- ARMV8 datasheet学习笔记5:异常模型

1.前言 2.异常类型描述 见 ARMV8 datasheet学习笔记4:AArch64系统级体系结构之编程模型(1)-EL/ET/ST 一文 3. 异常处理路由对比 AArch32.AArch64架 ...

- ARMV8 datasheet学习笔记3:AArch64应用级体系结构

1.前言 本文主要从应用的角度介绍ARMV8的编程模型和存储模型 2. AArch64应用级编程模型 从应用的角度看到的ARM处理器元素: 可见的元素(寄存器/指令) 说明 可见的寄存器 R0-R30 ...

- ARMV8 datasheet学习笔记1:预备知识

1. 前言 ARMv8的架构继承以往ARMv7与之前处理器技术的基础; 除了支持现有的16/32bit的Thumb2指令外,也向前兼容现有的A32(ARM 32bit)指令集. 基于64bit的AAr ...

- ARMV8 datasheet学习笔记4:AArch64系统级体系结构之Generic timer

1.前言 2.generate timer 2.1 概述 提供了一个系统计数器,用来实时测量流逝的时间: 提供了一个虚拟计数器,用来测量某个虚拟机上流逝的虚拟时间: 定时器,每隔一段时间会触发事件,支 ...

- ARMV8 datasheet学习笔记2:概述

1. 前言 本文主要概括的介绍ARMV8体系结构定义了哪些内容,概括的说: ARM体系结构定义了PE的行为,不会定义具体的实现 ARM体系结构也定义了debug体系结构和trace体系结构 ARM体系 ...

随机推荐

- (python爬取小故事网并写入mysql)

前言: 这是一篇来自整理EVERNOTE的笔记所产生的小博客,实现功能主要为用广度优先算法爬取小故事网,爬满100个链接并写入mysql,虽然CS作为双学位已经修习了三年多了,但不仅理论知识一般,动手 ...

- BZOJ 4009: [HNOI2015]接水果

4009: [HNOI2015]接水果 Time Limit: 60 Sec Memory Limit: 512 MBSubmit: 636 Solved: 300[Submit][Status] ...

- Shell基础知识(二)

对于一个shell脚本来说,第一行是 "#!/bin/bash",这条命令中的 "#!" 告诉系统该用哪一款解释器来对该脚本进行解释,后面的"/bin ...

- P1558 色板游戏 线段树+二进制状压

好,这个想法是我想拿去做HH的项链的.但是那个颜色有十万种...直接爆. 做这个倒是so easy 被两个地方坑了.1,a,b可能大小相反. 2,ask之前要down一波,我没down就挂了..... ...

- 【POJ1961】最短周期串/最大周期 kmp

引理:\(s[1,i]\) 具有长度为 \(len\) 的循环节的充要条件是:\(len\ |\ i,s[1,i-len]=s[len+1,i]\). 代码如下 #include <cstdio ...

- 12: MyBatis之传入参数parameterType

源链接地址:http://blog.csdn.net/liaoxiaohua1981/article/details/6862764

- 常用linux命令(项目部署)

centos 图形 命令行 界面切换 如果在图形界面下,按:Ctrl+Alt+F2进入如下命令行界面 -------------- 看当前目录的路径: pwd ................... ...

- Shell中while循环的done 后接一个重定向<

读文件的方法: 第一步: 将文件的内容通过管道(|)或重定向(<)的方式传给while 第二步: while中调用read将文件内容一行一行的读出来,并付值给read后跟随的变量.变量中就保存了 ...

- switch查询成绩、公司年销售额求和、根据工龄求工资

/* 1 编写代码实现如下内容:if语句实现考试成绩分等级(使用switch语句). [90-100] A等. [80-90) B等. [70-80) C等. [60-70) D等. [0-60) E ...

- Python协程笔记 - yield

生成器(yield)作为协程 yield实际上是生成器,在python 2.5中,为生成器增加了.send(value)方法.这样调用者可以使用send方法对生成器发送数据,发送的数据在生成器中会赋值 ...