Verilog中使用'include实现参数化设计

前段时间在FPGA上用Verilog写了一个多端口以太网的数据分发模块,因为每个网口需要独立的MAC地址和IP地址,为了便于后期修改,在设计中使用parameter来定义这些地址和数据总线的位宽等常量。

当时的做法是,顶层模块和子模块中都定义parameter型常数,在顶层模块引用子模块时,通过参数传递改变在被引用子模块中已定义的参数,实现在顶层模块统一管理参数的功能,代码如下

module top(); // 顶层模块

parameter eth1_ip_addr = {'d192, 8'd168, 'd100, 8'd1}; // 以太网1 IP地址 192.168.100.1

parameter eth2_ip_addr = {'d192, 8'd168, 'd100, 8'd2}; // 以太网2 IP地址 192.168.100.2 // 子模块1例化

sub1

#( .ip_addr(eth1_ip_addr) // 参数传递

)

sub1_inst( ); //端口映射 // 子模块2例化

sub2

#( .ip_addr(eth2_ip_addr) // 参数传递

)

sub2_inst( ); //端口映射

子模块1和2分别实现以太网1和2的收发功能,ip_addr为各自的本地IP地址,通过参数传递将eth1_ip_addr和eth2_ip_addr的值分别传递给两个子模块的ip_addr常数。

不过上述方法的缺点在于:

1. 当子模块的参数较多,并且要多次实例化时,代码会显得较为臃肿

2. 假如工程的层次有4层,某个参数只在第4层的模块使用到,为了实现将参数从顶层传递到第4层,第2层和第3层模块的参数列表中必须包含该参数。

解决上述问题有两种方法:

1. 使用defparam命令在顶层模块对子模块中的参数重定义,但是该方法同样存在一个问题:改变已经实例化后的模块中的参数,必须用英文小数点(.)表示层次逻辑关系,如下所示

module top;

reg clk;

reg [:] in1;

reg [:] in2;

wire [:] o1;

wire [:] o2;

// 子模块实例化

vdff m1 (o1, in1, clk);

vdff m2 (o2, in2, clk);

endmodule

// 子模块定义

module vdff (out, in, clk);

parameter size = , delay = ;

input [:size-] in;

input clk;

output [:size-] out;

reg [:size-] out; always @(posedge clk)

# delay out = in;

endmodule

// 参数重定义模块

module annotate;

defparam

top.m1.size = , // size参数的层次化表示

top.m1.delay = ,

top.m2.size = ,

top.m2.delay = ;

endmodule

具体使用方法见http://www.cnblogs.com/hechengfei/p/4116667.html

2. 使用`inculude预处理命令

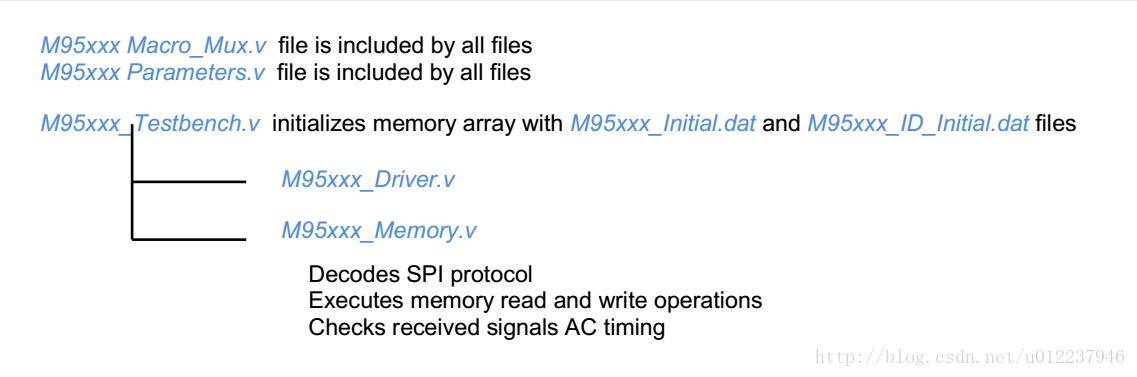

最近在STM官网上找M95xxx系列的EEPROM资料时,看到该芯片的Verilog Testbench模块,如下图所示

M95XXX_Macro_Mux.v:定义M95xxx系列芯片的AC参数

M95XXX_Parameters.v:定义Memory大小、有效地址位数和Page大小等参数

M95xxx_Testbench.v:链接 M95xxx_Driver.v和M95xxx_Memory.v

M95xxx_Driver.v:模拟M95xxx_Memory.v文件基于SPI接口的读写行为

M95xxx_Memory.v:M95xxx EEPROM的行为级描述模型

在上述文件中,M95XXX_Macro_Mux.v和M95XXX_Parameters.v定义了全局参数,被其他文件通过’include命令包含到文件内。具体使用方法如下

M95XXX_Parameters.v 参数定义文件

`define MEM_ADDR_BITS //memory address bits

`define PAGE_ADDR_BITS //page address bits

M95xxx_Driver.v 驱动文件

`include "M95XXX_Parameters.v"

reg[`MEM_ADDR_BITS-:] memory_address;

reg[`PAGE_ADDR_BITS-:] page_address;

可以看到要调用参数文件中参数时,需要:

1. 使用'include命令包含参数文件

2. 使用反引号+参数名的方式来调用该参数

STM MP95xxx系列EEPROM Verilog Testbench模型的链接地址:

https://gitee.com/hombeen/codes/y9rb0g7ej385sipqozvla95

Verilog中使用'include实现参数化设计的更多相关文章

- Verilog语法基础讲解之参数化设计

Verilog语法基础讲解之参数化设计 在Verilog语法中,可以实现参数化设计.所谓参数化设计,就是在一个功能模块中,对于一个常量,其值在不同的应用场合需要设置为不同的置,则将此值在设计时使用 ...

- 【实战】verilog中`define的使用记录

背景: 在最近实战开发中发现:对外部芯片进行初始化时,往往需要定义大量参数. 若直接在module中通过localparam或者parameter进行参数定义的话,会带来两个问题: 1.代码长度增加, ...

- C/C++ 中的include

当需要使用已有的方法或库时, 可以将它们的头文件#include进来. #include会在preprocess过程中被替换成它包含的代码. 头文件中包含了需要使用的函数/变量的声明. 当然声明与定义 ...

- Android在layout xml中使用include

Android include与merge标签使用详解 - shuqiaoniu的博客 - 博客频道 - CSDN.NEThttp://blog.csdn.net/shuqiaoniu/article ...

- system verilog中的跳转操作

在verilog中,使用disable声明来从执行流程中的某一点跳转到另一点.特别地,disable声明使执行流程跳转到标注名字的声明组末尾,或者一个任务的末尾. verilog中的disable命令 ...

- system verilog中的类型转换(type casting)、位宽转换(size casting)和符号转换(sign casting)

类型转换 verilog中,任何类型的任何数值都用来给任何类型赋值.verilog使用赋值语句自动将一种类型的数值转换为另一种类型. 例如,当一个wire类型赋值给一个reg类型的变量时,wire类型 ...

- 一段比较有意思的代码——介绍system verilog中的新增幅值语句

system verilog中新加了很多幅值语句,虽然都只适用于阻塞幅值,但是在某些场合中非常实用. 下面是一段有意思的代码,覆盖了一些用法. package definitions; typedef ...

- fatal error C1010: 在查找预编译头时遇到意外的文件结尾。是否忘记了向源中添加“#include "StdAfx.h"”? 解决方法

错误描述: fatal error C1010: 在查找预编译头时遇到意外的文件结尾.是否忘记了向源中添加“#include "StdAfx.h"”? 错误分析: 此错误发 ...

- EF Core 1.0中使用Include的小技巧

(此文章同时发表在本人微信公众号"dotNET每日精华文章",欢迎右边二维码来关注.) 题记:由于EF Core暂时不支持Lazy Loading,所以利用Include来加载额外 ...

随机推荐

- java 接口默认修饰符

概论: java接口可以是public 的,也可以是friendly的,但一定是abstracted的. java接口里的方法只能是public的.abstract的. java接口里的成员变量只能是 ...

- DevOps 发展融合运维可视化

DevOps,是开发(Development)和运维(Operations)的组合,代表一种文化.运动或实践,旨在促进软件交付和基础设施变更软件开发人员(Dev)和 IT 运维技术人员(Ops)之间的 ...

- spring boot(16)-mail发邮件

上一篇讲了如何处理异常,并且异常最终会写入日志.但是日志是写在服务器上的,我们无法及时知道.如果能够将异常发送到邮箱,我们可以在第一时间发现这个异常.当然,除此以外,还可以用来给用户发验证码以及各种离 ...

- Spring手册

一.Spring 简介 二.结构体系 三.七大主要模块 四.Spring Maven依赖 五 .Sprinf framework 一.Spring 简介 spring是一个开源的轻量级的应用开发框架, ...

- [翻译] CSStickyHeaderFlowLayout

CSStickyHeaderFlowLayout https://github.com/jamztang/CSStickyHeaderFlowLayout Parallax, Sticky Heade ...

- IP地址分类及CIDR划分方法

IP地址的分类和表示有三种形式,1.分类的IP地址.2.子网划分.3.无分类编址CIDR 1.分类的IP地址 IP地址:: = {<网络号>,<主机号>} 不同的网络号和主机号 ...

- Oracle 数据库创建(图形界面操作)

Oracle 创建数据库图文分解: 1. 选择所有程序->Oracle-OraDb11g_home1->Configuration and Migration Tools -> Da ...

- UVa 1412 - Fund Management(状压DP + 预处理)

链接: https://uva.onlinejudge.org/index.php?option=com_onlinejudge&Itemid=8&page=show_problem& ...

- BZOJ4259:残缺的字符串(FFT)

Description 很久很久以前,在你刚刚学习字符串匹配的时候,有两个仅包含小写字母的字符串A和B,其中A串长度为m,B串长度为n.可当你现在再次碰到这两个串时,这两个串已经老化了,每个串都有不同 ...

- BZOJ3160:万径人踪灭(FFT,Manacher)

Solution $ans=$回文子序列$-$回文子串的数目. 后者可以用$manacher$直接求. 前者设$f[i]$表示以$i$为中心的对称的字母对数. 那么回文子序列的数量也就是$\sum_{ ...