筛选最小值---verilog

筛选最小值---verilog

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: chensimin

//

// Create Date: 2018/12/07 15:30:20

// Design Name:

// Module Name: aes_dru

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////// module aes_dru ( input wire clk,

input wire rst ); //--------------------------------------------------------------------- //计数器,方便对生成的序列进行定位,仿真时,生成信号源的好思路 reg [:] cnt_for_serin = ; always @ (posedge clk or posedge rst)

begin

if(rst)

cnt_for_serin <= ;

else

cnt_for_serin <= cnt_for_serin + 'b1;

end //--------------------------------------------------------------------- //生成serin序列 reg serin = ; always @ (posedge clk or posedge rst)

begin

if(rst)

serin <= ;

else

begin

case(cnt_for_serin)

: serin <= 'b1;

: serin <= 'b0;

: serin <= 'b1;

: serin <= 'b0;

: serin <= 'b1;

default: serin <= serin;

endcase

end

end //--------------------------------------------------------------------- reg [:] inffs = ; always @ (posedge clk or posedge rst)

begin

if(rst)

inffs <= ;

else

inffs <= {inffs[:], serin};

end //--------------------------------------------------------------------- //边沿检测可以检测上升沿和下降沿 assign edge_detect = ^inffs[:]; //--------------------------------------------------------------------- //计算出两个脉冲之间的时钟周期 reg [:] min_cntr = ; always @ (posedge clk or posedge rst)

begin

if(rst)

min_cntr <= ;

else if(edge_detect)

min_cntr <= ;

else

min_cntr <= min_cntr + ;

end //--------------------------------------------------------------------- //对边沿脉冲进行计数 reg [:] update_cntr = ; always @ (posedge clk or posedge rst)

begin

if(rst)

update_cntr <= ;

else if(edge_detect)

update_cntr <= update_cntr + 'b1;

end //--------------------------------------------------------------------- //当边沿脉冲数满后,产生一个叫update_min的脉冲 wire update_min; assign update_min = update_cntr == {{'b1}}; //--------------------------------------------------------------------- //当updata_min脉冲到来时,最小值设定为全1,new_min成为更新min_capture的条件 reg [:] min_capture = ; always @ (posedge clk or posedge rst)

begin

if(rst)

min_capture <= ;

else if(edge_detect)

begin

if(update_min)

min_capture <= {{'b1}};

else if(new_min)

min_capture <= min_cntr;

end

end assign new_min = min_cntr < min_capture; //--------------------------------------------------------------------- //当结束完一个计数周期后,用min_hold 锁存本周期的最小值 reg [:] min_hold = ; always @ (posedge clk or posedge rst)

begin

if(rst)

min_hold <= ;

else if (edge_detect & update_min)

min_hold <= min_capture;

end //--------------------------------------------------------------------- // reg [:] sample_cntr = ; always @ (posedge clk or posedge rst)

begin

if(rst)

sample_cntr <= ;

else if (edge_detect | (sample_cntr >= min_hold))

sample_cntr <= ;

else

sample_cntr <= sample_cntr + ;

end //--------------------------------------------------------------------- endmodule /* add_force {/aes_dru/clk} -radix hex {1 0ns} {0 25000ps} -repeat_every 50000ps

add_force {/aes_dru/rst} -radix hex {1 0ns} {0 100ns} */

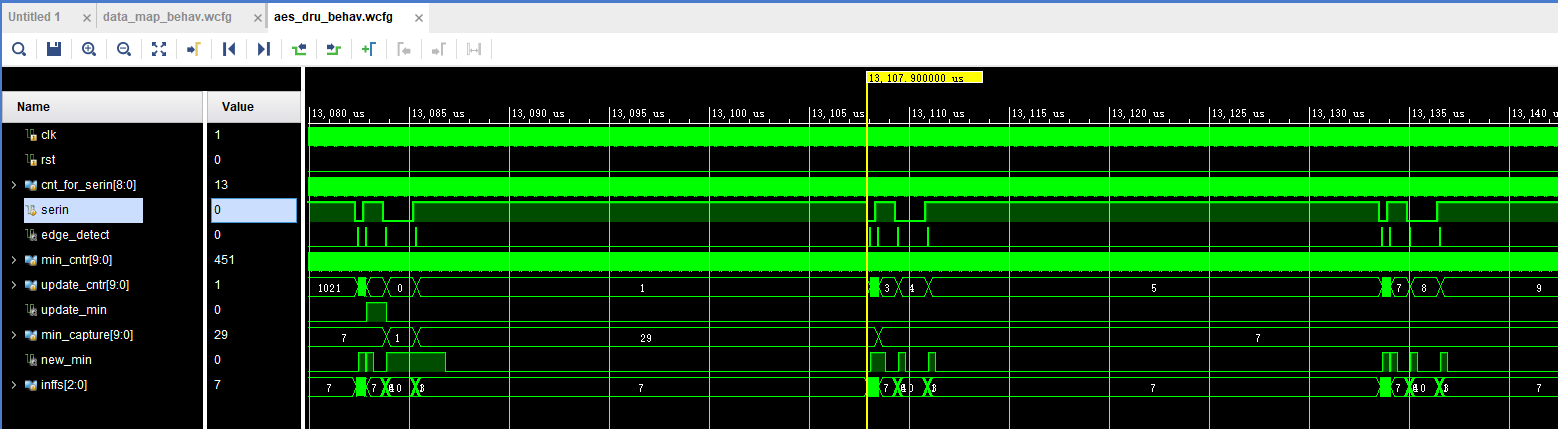

仿真结果:

筛选最小值---verilog的更多相关文章

- Leetcode:378. Kth Smallest Element in a Sorted Matrix

题目: Given a n x n matrix where each of the rows and columns are sorted in ascending order, find the ...

- MongoDB驱动之Linq操作

添加下面命名空间到您的程序中: using MongoDB.Driver.Linq; 声明一变量保存对集合的引用 var collection = database.GetCollection< ...

- nyoj847 S + T(贪心)

题目847 题目信息 执行结果 本题排行 讨论区 S + T 时间限制:1000 ms | 内存限制:65535 KB 难度: 描写叙述 给你一个长度为n的整数序列A1.A2,--,An,找出两个 ...

- Queue-PriorityQueue源码解析

Queue队列通常是先进先出(FIFO),但也有特殊的非FIFO,如本文也分析的PriorityQueue. Queue接口 Queue接口定义的方法: 添加元素接口: add(E e) -> ...

- MYSQL 二次筛选,统计,最大值,最小值,分组,靠拢

HAVING 筛选后再 筛选 SELECT CLASS,SUM(TOTAL_SCORES) FROM student_score GROUP BY CLASS HAVING SUM(TOTAL_SCO ...

- pandas 筛选某一列最大值最小值 sort_values、groupby、max、min

高效方法: dfs[dfs['delta'].isnull()==False].sort_values(by='delta', ascending=True).groupby('Call_Number ...

- 【转载】使用Pandas对数据进行筛选和排序

使用Pandas对数据进行筛选和排序 本文转载自:蓝鲸的网站分析笔记 原文链接:使用Pandas对数据进行筛选和排序 目录: sort() 对单列数据进行排序 对多列数据进行排序 获取金额最小前10项 ...

- 开始VS 2012中LightSwitch系列的第4部分:太多信息了!使用查询来排序和筛选数据

[原文发表地址] Beginning LightSwitch in VS 2012 Part 4: Too much information! Sorting and Filtering Data ...

- [ACM_其他] 总和不小于S的连续子序列的长度的最小值——尺缩法

Description: 给定长度为n的整数数列,A[0],A[1],A[2]….A[n-1]以及整数S,求出总和不小于S的连续子序列的长度的最小值.如果解不存在,则输出0. Input: 输入数据有 ...

随机推荐

- [python] [Jupyter Notebook]

最近又要用notebook 转一篇我原来写的安装教程 还是很好用的. IPython是一个 Python 的一个交互式 shell,它提供了很多内建的函数.Jupyter Notebook是IPyt ...

- verilog reg 初值问题

虽然没有写初值 但是硬件电路肯定有逻辑电平的如果是用fpga实现的 缺省值为全0 也可以在信号声明时指定初始值如果是asic实现 初始值是随机的(但也是某个电平) 声明时指定初值会被忽略 rtl仿真时 ...

- HTML语言发展史

.发展时间线 1982年,Tim Berners-Lee 建立 HTML 1993年,大學生的 Marc Andreessen 在他的 Mosaic 浏览器加入 标记,从此可以在Web頁面上浏览图片 ...

- arcgis 添加经纬度坐标点

ArcGIS 10.2导入X.Y坐标(经度.纬度),生成Shapefile点数据 参考博客很完整 基站-纬度-经度 1---- 2----X 经度 Y 纬度 Z高程(没有) 3---一开始只定 ...

- jquery 上滑加载更多

$(document).ready(function() { var totalPage = {$totalPage};//总页数 var page = {$page}; //起始页 var page ...

- navicat premium 安装破解(Mac & win)

1.windows请参考以下连接: https://www.jianshu.com/p/5f693b4c9468 2.mac安装教程 下载:http://www.pc6.com/mac/111878. ...

- 1. ReactJS基础(开发环境搭建)

本文主要介绍通过React官方提供的create-react-app脚手架进行开发环境的搭建. 1.安装node环境(安装过程这里不做介绍,可参考其他博文) 在cmd中输入node -v 如果可以看到 ...

- 浅析toString()和toLocaleString()的区别

翻看<javascript高级程序设计>,对toString()和toLocaleString()两者的区别并没有直白的说明,简单查阅了一下 ecmascript官方文档 和 MDN 二者 ...

- JSF相关介绍

About JavaServer Faces technology simplifies building user interfaces for JavaServer applications. D ...

- Python 3.6print 出现 SyntaxError: invalid syntax

开始使用sublime学习python,编写代码如图 Ctrl+B运行以后,报错 SyntaxError: invalid syntax 百度查询以后,大部分的回答都是说,python在3.0以后 ...