《FPGA全程进阶---实战演练》第九章 计数器要注意

本小节我们来做一个好玩的事情,就是计数器,还记得在做LED自加实验时我们就曾经提到过关于计数器的相关议题,那么这节我们就来讨论讨论。

探讨一下如下的问题:请用verilog记八个数的写法,分析这个可以更好的理解触发器的工作原理。

.

reg [:]cnt;

always@(posedge clk or negedge rst_n) begin

if(!rst_n)

cnt <= 'd0;

else if (cnt < 'd8)

cnt <= cnt + 'b1;

else

cnt <= 'd0;

end

.

reg [:]cnt;

always@(posedge clk or negedge rst_n) begin

if(!rst_n)

cnt <= 'd0;

else if (cnt < 'd8 - 1)

cnt <= cnt + 'b1;

else

cnt <= 'd0;

end

.

reg [:]cnt;

always@(posedge clk or negedge rst_n) begin

if(!rst_n)

cnt <= 'd1;

else if (cnt < 'd8 )

cnt <= cnt + 'b1;

else

cnt <= 'd1;

end .

reg [:]cnt;

always@(posedge clk or negedge rst_n) begin

if(!rst_n)

cnt <= 'd1;

else if (cnt < 'd7 )

cnt <= cnt + 'b1;

else

cnt <= 'd1;

end

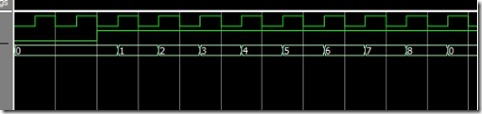

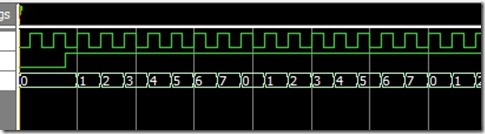

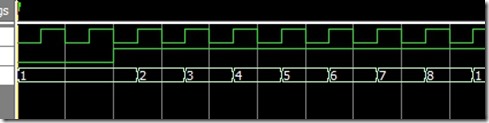

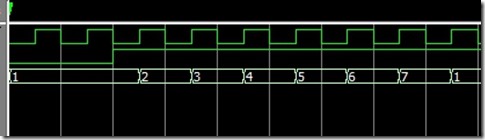

对应的仿真结果为:

1.计数为9个。

2.计数为8个

3.计数为8个

4.计数为7个

在else if语句中的判断条件为 cnt < 4’d7或者cnt <4’d8,以cnt < 4’d7为例,当cnt =4’d7显然是不满足条件的,所以利用跳出自加程序,执行else语句,但是cnt = 4’d7也会被打印输出,这是由于时序电路在时钟的节奏下一拍一拍的输出,当时钟上升沿来临时,这时cnt = 4’d7,然后等待下一个时钟沿到来把cnt = 4’d7打入到锁存器里面去,然后再在下一个时钟沿来临将cnt = 4’d0打入。以此类推。

针对上述的四种情况,大家在写一些利用计数器进行分频的程序时,若是精确控时,请注意cnt小于的常数是多少,这一点务必搞清楚。

《FPGA全程进阶---实战演练》第九章 计数器要注意的更多相关文章

- 《FPGA全程进阶---实战演练》第三十二章 Signal Tap II 应用实例

还有几天就要交文章终稿了,三年的研究生生活也快要结束了,时间飞快,岁月如梭,但学习技术的热情仍然不能松懈,不懂的东西太多,需要实时保持奋斗!!过些天会继续更新<FPGA全程进阶---实战演练&g ...

- 《FPGA全程进阶---实战演练》第五章 基于74HC595的LED操作

1基础理论部分 1.1分频 分频,是的,这个概念也很重要.分频是指将一单一频率信号的频率降低为原来的1/N,就叫N分频.实现分频的电路或装置称为“分频器”,如把33MHZ的信号2分频得到16.5MHZ ...

- 《FPGA全程进阶---实战演练》第四章之实验平台软硬件使用简介

本章主要是讲解读者在进行FPGA逻辑设计之前的准备工作,需要下载Quartus II软件和 Modelsim 软件,一个是用来进行FPGA逻辑设计,一个是用来对逻辑进行理论分析与验证. 1.1 qua ...

- 《FPGA全程进阶---实战演练》第二十一章 细说低速与高速电路设计之电阻 电容 电感 磁珠

1.1 什么是高速电路 信号的最高频率成分是取决于有效频率,而不是周期频率. 高速电路的定义是根据信号的有效频率来计算的,在现实世界中,任何信号都是由多个频率分量的正弦波叠加而成的.定义各正弦波分 ...

- 《FPGA全程进阶---实战演练》第十二章 二进制码与格雷码PK

大家在写程序的时候,可能会听闻,什么独热码,什么格雷码,什么二进制码等等,本节意在解释这几种编码之间的区别和优势以及用verilog怎么去实现,下面先介绍这几种编码的区别. 1 基础理论部分 1.1 ...

- 《FPGA全程进阶---实战演练》第十一章 VGA五彩缤纷

1基础理论部分 VGA(video graphics array)即视频图形阵列,是IBM在1987年随PS/2一起推出的使用模拟信号的一种视频传输标准.VGA相比与现在的视频传输接口来说已经过时,不 ...

- 《FPGA全程进阶---实战演练》第一章之如何学习FPGA

对于很多初学者,大部分都是急于求成,熟不知越是急于求成,最终越是学无所成,到头来两手空空,要学好FPGA,必须弄懂FPGA本质的一些内容. 1.FPGA内部结构及基本原理 FPGA是可以编程的,必须通 ...

- 《FPGA全程进阶---实战演练》第一章之FPGA介绍

1 什么是FPGA FPGA也即是Field Programmable Gate Array的缩写,翻译成中文就是现场可编程门阵列.FPGA是在PAL.GAL.CPLD等可编程器件的基础上发展起来的新 ...

- 《FPGA全程进阶---实战演练》第二章之焊接板子及调试注意事项

1.若是读者第一次做板子,强烈建议画完PCB板后将PCB图打印出来,然后对照你买的芯片将芯片放置对 应的位置,然后查看所有的封装格式适不适合,否则等你做出板子来后再试,为时晚矣.笔者虽然知道要这么 做 ...

随机推荐

- 关于CAE的那点儿破事儿【二】

前面在<关于CAE的那点破事儿>一文中,主要提到了CAE是什么.CAE能做些什么.人在CAE应用中的作用以及CAE从业中应当具有哪些基本素质.然而CAE是一把双刃剑,如果不能在工程应用中很 ...

- [SQL in Azure] Configure a VNet to VNet Connection

http://msdn.microsoft.com/en-us/library/azure/dn690122.aspx Configure a VNet to VNet Connection 2 ou ...

- mysql++ Query

mysqlpp:: Query类存储了Connection的指针,可以用它进行SQL语句的增删改查. 连上数据库后,使用mysqlpp::Connection::query()获取Query对象 Qu ...

- 【转】【WebStorm】利用WebStorm来管理你的Github

用webstorm上传代码时,首先要先下载git,网址一搜就可以搜到,然后开始配置webstorm,打开webstorm,在file-settings中直接搜索github,然后输入自己github的 ...

- 【转】如何在Mac上卸载Java及安装Java

如何在 Mac 上卸载 Java? 本文适用于: 平台: Macintosh OS X Java 版本: 7.0, 8.0 使用终端卸载 Oracle Java 注:要卸载 Java,必须具有管理员权 ...

- 不要问我有多懒,写个脚本跑django

写django的都知道,要跑起django测试环境,只需要 python manage.py runserver 就可以了,但是时间一长,就觉得敲这个命令太浪费时间了,而我又是个懒人. 同事用的是ct ...

- 消息队列RabbitMQ基础知识详解

一: 什么是MQ? MQ全称为Message Queue, 消息队列(MQ)是一种应用程序对应用程序或者模块对模块的通信方法.MQ是消费-生产者模型的一个典型的代表,一端往消息队列中不断写入消息,而另 ...

- Faiss教程:入门

Faiss处理固定维度d的数据,矩阵每一行表示一个向量,每列表示向量的一项.Faiss采用32-bit浮点型存储. 假设xb为数据集,维度为\(nb\times{d}\):xq是查询数据,维度为\(n ...

- [转]Bootstrap table后端分页(ssm版)

原文地址:https://www.cnblogs.com/flyins/p/6752285.html 说明bootstrap table可以前端分页,也可以后端sql用limit分页.这里讲的是后端分 ...

- 用B表更新A表

UPDATE dbo.POR_LOT SET POR_LOT.SHIPPED_FLAG =B.SHIPPED_FLAGFROM POR_LOT A INNER JOIN ( SELECT T5.LOT ...