74HC595驱动(并转串,fpga与时钟匹配,fpga与外部芯片的连接注意事项)

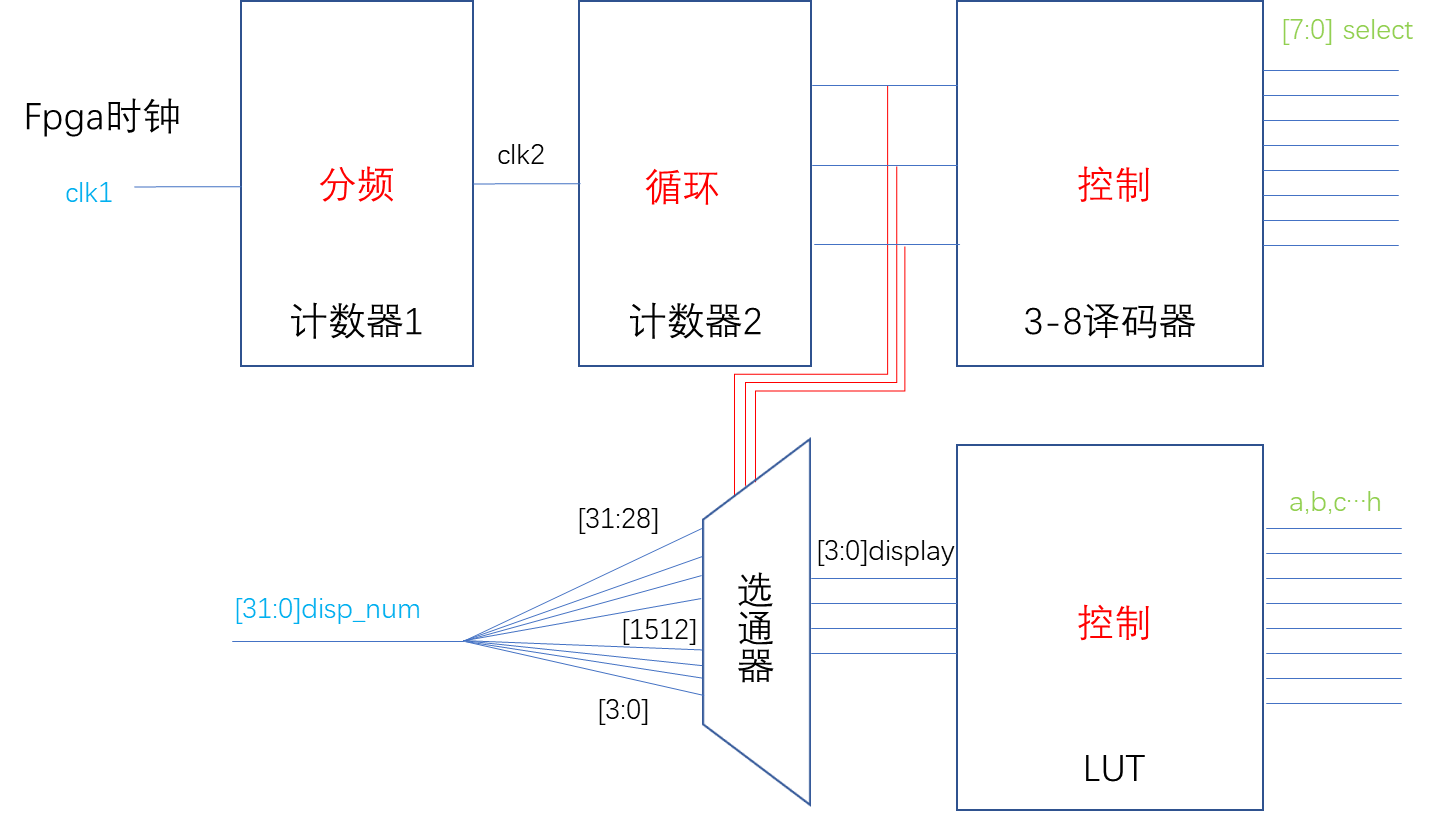

上一次设计的动态扫描数码管显示电路模型如上,这是一个32位并行数据[31:0]disp_num选通输出并行数据[7:0]select和[7:0]段选的电路。因此需要输出16个信号

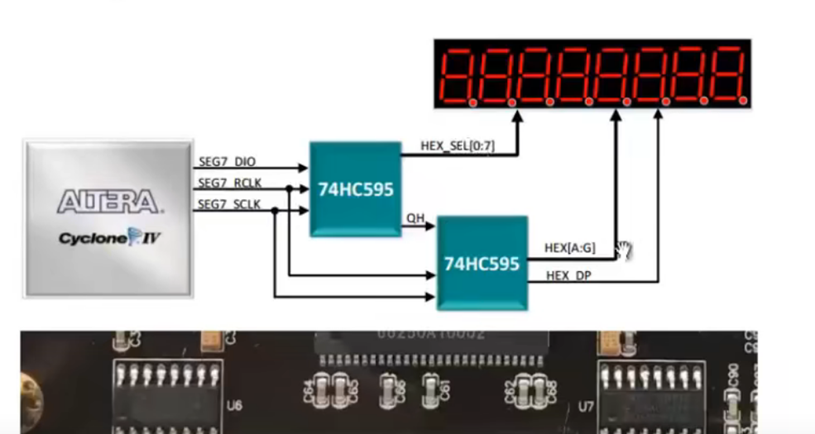

而在开发板上的电路与这个的接口不同,如下:

这个开发板设计的fpga只有有三个输出,接到2片级联的74HC595芯片上,并行输出段选和位选数据。

这三个输出分别为:DIO(串行数据),SCLK(与74HC595匹配的时钟信号),RCLK(锁存器使能信号)

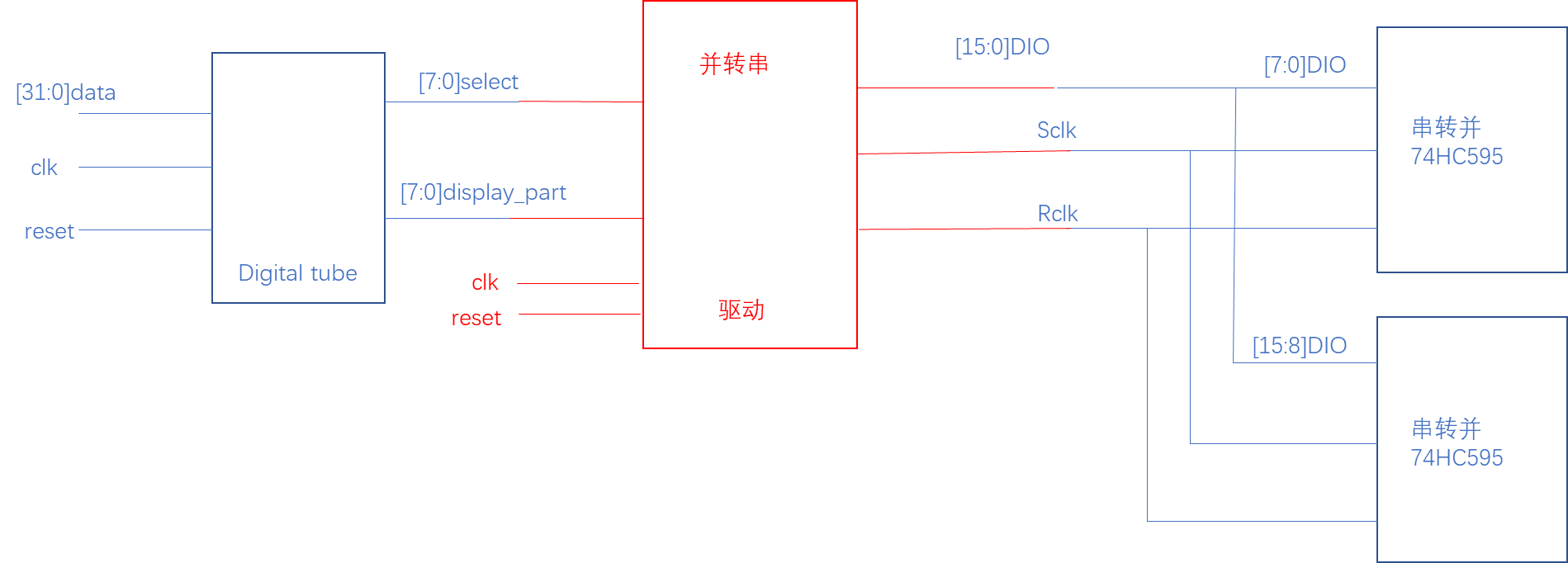

因此,想要在这片开发板上控制数码管显示,就得修改代码。

在上一次代码的基础上,把输出的16位并行数据转化为串行数据从DIO端口输出。(并行数据转串行数据:逐个输出即可)。

由于74HC595时钟信号频率与fpga芯片的时钟信号频率不相等,fpga芯片的时钟频率为50MHz,而74HC595时钟频率在不同的驱动电压下不同,在3.3VS可以达到6~30MHz,为了方便,我们可以根据fpga50MHz的时钟产生一个12.5MHz的信号作为74HC595的SCLK信号输入 。

为了数据传输的稳定,在传输串行数据时,我们可以在SCLK的低电平时刻从fpga中输出一个数据,在SCLK上升沿到来时输入到74HC595,这样子防止亚稳态的产生。

每16个数据传输完成后,再让锁存器使能信号有效,这样子一次性把16个数据从两片移位寄存器中传到锁存器中,输出给数码管。

对于74HC595芯片,其设计就是一个移位寄存器(实现串行数据转换为并行数据),如图所示:

16个输出Q并行输出。

module drive_digital_tube(

clk,

reset,

data,

s_en,

DIO,

sclk,

rclk,

s_done

);

input clk;//50MHz

input reset;

input [15:0]data;

input s_en;

output reg DIO;

output reg sclk;

output reg rclk;

output reg s_done; reg [1:0]div_cnt;// 分频计数器,频率为25MHz

always@( posedge clk or negedge reset)

begin

if (!reset)

div_cnt <= 2'd0 ;

else if(div_cnt == 1)

div_cnt <= 2'd0 ;

else

div_cnt <= div_cnt + 1'd1 ;

end wire pulse25M; //频率为25MHz的取样脉冲

assign pulse25M = ( div_cnt == 2'd1 ) ? 1 : 0 ; reg [5:0]cnt;//计数33个状态

always@(posedge clk or negedge reset)

begin

if(!reset)

cnt <= 6'd0 ;

else if (s_en)

begin

if (pulse25M)

begin

if(cnt == 6'd33)

cnt <= 6'd0 ;

else

cnt <= cnt + 1 ;

end

end

else

cnt <= 6'd0 ;

end always@(posedge clk or negedge reset)

begin

if(!reset)

begin

DIO <= 0 ;

sclk <= 0 ;

rclk <= 0 ;

s_done = 0 ;

end

else if(s_en)

begin

if (pulse25M)

case(cnt)//sclk为12.5MHz信号,rclk为输出使能(所有数据取完后),在sclk的低电平时取值,可以稳定,在sclk上升沿到来时可稳定输出

0:begin DIO <= 0 ;sclk <= 0 ;rclk <= 0 ;s_done = 0 ;end

1: sclk <= 1 ;

2:begin DIO <=data[15] ;sclk <= 0 ; end

3:sclk <= 1 ;

4:begin DIO <=data[14] ;sclk <= 0 ; end

5:sclk <= 1 ;

6:begin DIO <=data[13] ;sclk <= 0 ; end

7:sclk <= 1 ;

8:begin DIO <=data[12] ;sclk <= 0 ; end

9:sclk <= 1 ;

10:begin DIO <=data[11] ;sclk <= 0 ; end

11:sclk <= 1 ;

12:begin DIO <=data[10] ;sclk <= 0 ; end

13:sclk <= 1 ;

14:begin DIO <=data[9] ;sclk <= 0 ; end

15:sclk <= 1 ;

16:begin DIO <=data[8] ;sclk <= 0 ; end

17:sclk <= 1 ;

18:begin DIO <=data[7] ;sclk <= 0 ; end

19:sclk <= 1 ;

20:begin DIO <=data[6] ;sclk <= 0 ; end

21:sclk <= 1 ;

22:begin DIO <=data[5] ;sclk <= 0 ; end

23:sclk <= 1 ;

24:begin DIO <=data[4] ;sclk <= 0 ; end

25:sclk <= 1 ;

26:begin DIO <=data[3] ;sclk <= 0 ; end

27:sclk <= 1 ;

28:begin DIO <=data[2] ;sclk <= 0 ; end

29:sclk <= 1 ;

30:begin DIO <=data[1] ;sclk <= 0 ; end

31:sclk <= 1 ;

32:begin DIO <=data[0] ;sclk <= 0 ; rclk <= 1 ;end

33:begin sclk <= 1 ; rclk <= 0 ;s_done = 1 ;end

default ;

endcase

end

else

begin

DIO <= 0 ;

sclk <= 0 ;

rclk <= 0 ;

s_done = 0 ;

end

end end

module

`timescale 1ns / 1ns

module drive_digital_tube_tb(

); reg clk ;

reg reset;

reg s_en;

reg [15:0]data;

wire DIO;

wire sclk;

wire rclk;

wire s_done ; drive_digital_tube drive_digital_tube_sim(

clk,

reset,

data,

s_en,

DIO,

sclk,

rclk,

s_done

); initial clk = 1;

always #10 clk = ! clk ;

initial

begin

reset = 0 ;

data = 0 ;

s_en = 0 ;

#201;

reset = 1 ;

s_en = 1 ;

data = 16'ha55a;

@(negedge s_done);

s_en = 0;

#200;

s_en = 1;

data = 16'h7597;

@(negedge s_done);

s_en = 0;

#200;

s_en = 1;

data = 16'h6425;

@(negedge s_done); $stop ;

end endmodule

注意:

①有的内部变量由于没有真正用上,在仿真时波形为X,会使结果错误。检查alyays里面有没有 posedge reset,没有的话可能会出现这种情况。

②对于输入的数据,最好拿一个寄存器把当下的值存下来(添加一个控制信号),再慢慢输出,不然可能会造成输入数据不稳定,传输结果错误。

③fpga与外部芯片连接的场景:大部分情况下需要fpga产生一个时钟信号来驱动外部芯片,因此,对于fpga既要提高数据又要提高时钟的情况,我们可以在自己提供的时钟的低电平时刻输出数据,这样子可以保证外部芯片输入数据的稳定,在时钟上升沿到来时已经稳定,不会产生亚稳态。

74HC595驱动(并转串,fpga与时钟匹配,fpga与外部芯片的连接注意事项)的更多相关文章

- 关于 FPGA 和 外部芯片接口时序设计

在看这篇文章之前, 建议先好好读下这篇文章.http://download.csdn.net/detail/angelbosj/8013827. 因为我不太会用 VISio.要是哪位网友能告诉我.怎么 ...

- FPGA的时钟质量对设计的影响

小梅哥编写,未经许可严禁用于任何商业用途 近期,一直在调试使用Verilog编写的以太网发送摄像头数据到电脑的工程(以下简称以太网图传).该工程基于今年设计的一款FPGA教学板AC620.AC620上 ...

- Xilinx FPGA全局时钟和全局时钟资源的使用方法

对FPGA的全局时钟了解不多,遂转载一篇文档: http://xilinx.eetop.cn/?action-viewnews-itemid-42 目前,大型设计一般推荐使用同步时序电路.同步时序电路 ...

- FPGA多时钟处理应用

FPGA项目设计中,通常会遇到多时钟处理.即一个PLL输出多个时钟,根据条件选择合适的时钟用作系统时钟.方案一: 外部晶振时钟进入PLL,由PLL输出多个时钟,MUX根据外部条件选择时钟输出做为系统使 ...

- 7系列FPGA的时钟资源——UG472

时钟架构总览 7系的FPGA使用了专用的全局(Global)和区域(Regional)IO和时钟资源来管理设计中各种的时钟需求.Clock Management Tiles(CMT)提供了时钟合成(C ...

- xilinx FPGA全局时钟资源的使用

1.什么是xilinx fpga全局时钟资源 时钟对于一个系统的作用不言而喻,就像人体的心脏一样,如果系统时钟的抖动.延迟.偏移过大,会导致系统的工作频率降低,严重时甚至会导致系统的时序错乱,实现不了 ...

- FPGA异步时钟设计中的同步策略

1 引言 基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统.但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免. ...

- FPGA跨时钟域握手信号的结构

FPGA跨时钟数据传输,是我们经常遇到的问题的,下面给出一种跨时钟握手操作的电路结构.先上图 先对与其他人的结构,这个结构最大的特点是使用 req 从低到高或者高到低的变化 来表示DIN数据有效并开始 ...

- FPGA开发时钟资源评估需要考虑的问题

在第一个独立开发的FPGA项目中,使用了Altera平台的三速以太网IP,工作在100M模式下,外部输入的PHY时钟频率为25MHz. 由于在前期没有注意这个外部输入的时钟,导致最后不得不在板子上飞线 ...

随机推荐

- Azure DevOps (十三) 通过Azure Devops部署一个Go的Web应用

前几篇文章中,我们分别实现通过azure来部署.NET和Springboot的应用,今天我们来研究一下如何部署一套Go的Web应用上去. 文章配套视频专栏: https://space.bilibil ...

- python 通过线上API查询ip归属地

API为国外API,频率限制1分钟45个ip 脚本如下 1 #!/usr/bin/env python3 2 #-*-coding:utf-8-*- 3 4 import requests,re,js ...

- 以圆类 Circle 及立体图形类 Solid 为基础设计圆柱类 Cylinder

学习内容:以圆类 Circle 及立体图形类 Solid 为基础设计圆柱类 Cylinder 代码示例: import java.util.Scanner;class Point3{ private ...

- Vue问题

vue问题 #(1)vouter的addRoutes方法---用户权限 //自定义添加路由方法,防止重复添加路由 #使用后 路由结构 const user = () => import('../ ...

- map计算

map理解 参考1: https://github.com/rafaelpadilla/Object-Detection-Metrics 参考2:https://github.com/rafaelpa ...

- 带你学习MindSpore中算子使用方法

摘要:本文分享下MindSpore中算子的使用和遇到问题时的解决方法. 本文分享自华为云社区<[MindSpore易点通]算子使用问题与解决方法>,作者:chengxiaoli. 简介 算 ...

- 20212115 实验二 《python程序设计》实验报告

实验二 计算器设计 #20212115 2021-2022-2 <python程序设计> 实验报告二 课程: 课程:<Python程序设计>班级: 2121姓名: 朱时鸿学号: ...

- rabbitMq急速安装教程

背景 我们在工作中很多时候其实也用过mq.但是仅仅只是会用,所以老猫在此想完整地归纳一下mq相关的知识点,在此分享给大家.首先给大家带来的是mq的单机急速安装.操作系统时centos7.(本来想记录到 ...

- python自动将新生成的报告作为附件发送并进行封装

发送报告作为自动化部署来讲是一个重要的环节,废话不多说直接上代码吧,如果想更细致的了解内容查阅本博主上篇基本发送文章 特别叮嘱一下:SMTP协议默认端口25,qq邮箱SMTP服务器端口是465 别出丑 ...

- 1. Docker的中央仓库安装设置及镜像的操作

具体也可参考:https://developer.aliyun.com/mirror/docker-ce?spm=a2c6h.13651102.0.0.3e221b11G7cfhr https://d ...