FPGA管脚约束

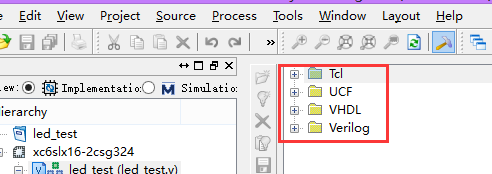

Edit → language templates :

打开即可查看基本语法。

一、xilinx中的约束文件

1、约束的分类

利用FPGA进行系统设计常用的约束主要分为3类。

(1)时序约束:主要用于规范设计的时序行为,表达设计者期望满足的时序条件,知道综合和布局布线阶段的优化算法等。

(2)布局布线约束:主要用于指定芯片I/O引脚位置以及指导软件在芯片特定的物理区域进行布局布线。

(3)其它约束:指目标芯片型号、接口位置、电气特性等约束属性。

2、约束的主要作用

(1)提高设计的工作效率

对很多数字电路设计来说,提高工作频率是非常重要的,因为高的工作频率意味着高效的电路处理能力,通过附加约束可以控制逻辑的综合、映射、布局和布线,以减少逻辑和布线的延迟,从而提高工作效率。

(2)获得正确的时序分析报告

几乎所有的FPGA设计平台都包含静态时序分析工具,利用这类工具可以获得映射或者是布局布线后的时序分析报告,从而对设计的性能做出评估。静态时序分析工具以约束作为判断时序是否满足设计要求的标准,因此要求设计者正确输入约束,以便静态时序分析工具输出正确的时序分析报告。

(3)指定FPGA引脚位置与电气标准

FPGA的可编程性使电路板设计加工和FPGA设计可以同时进行,而不必等FPGA引脚位置的完全确定,从而节约了系统开发时间。电路板加工完成后,设计者要根据电路板的走线对FPGA加上引脚位置约束,以保证FPGA与电路板正确连接。另外通过约束还可以指定I/O引脚所支持的接口标准和其他电气特性。为了满足日新月异的通信发展,Xilinx新型FPGA可以通过I/O引脚约束设置支持,诸如AGP、BLVDS、CTT、GTL、GTLP、HSTL、LDT、LVCMOS、LVDCI、LVDS、LVPECL、LVDSEXT、LVTTL、PCI、PCIX、SSTL、ULVDS等丰富的I/O接口标准。

(4)利于模块化设计

通过区域约束还能在FPGA上规划各个模块的实现区域,通过物理布局布线约束完成模块化设计等。

3、UCF约束文件

ISE 通过综合工具XST对设计进行约束,XST的综合约束文件时XCF文件,而在布局布线阶段,最重要的约束文件是用户约束文件UCF(user constraint file),两者有着千丝万缕的联系,UCF几乎支持XCF的所有约束语言和命令。通常在使用XST综合流程时,仅仅通过综合属性设置来设置全局的综合策略与参数,细化的约束是通过实现阶段的约束文件UCF完成的。因此,UCF文件时约束文件的核心,通过编译UCF文件可以实现时序、布局布线约束以及其他约束的绝大部分功能。

二、约束设计实例

A-时序约束

时序约束分为周期约束、I/O时序约束、分组约束和专门约束

1、周期约束

周期约束是一个基本时序和综合约束,它附加在时钟网络上,时序分析工作根据周期约束检查时钟域内所有同步器件的时序是否满足要求,它将检查与同步时序约束端口相连接的所有路径的延迟,但不会检查PAD到寄存器路径。

周期约束的语法如下:

TIMESPEC “TS_identifier”=PERIOD “TNM_reference” period {High|low}[high_or_low_time]

说明:

(1) TIMESPEC是一个基本时序相关约束标识

(2) TM_identifier包括字母TM和一个标识符identifier共同组成一个时序规范。

(3) 参数period为要求的时钟周期,可以使用ps、ns、us或者ms等单位,大小写都可以,缺省单位为ns

(4) “{}”为必选项,HIGH|LOW关键词指出时钟周期里的第一个脉冲是高电平还是低电平

(5) “[]”内为可选项,high_or_low_time为脉冲的延续时间,缺省单位是ns,默认占空比为50%

(6) 定义时钟周期约束时,首先需要对待约束的时钟网络上附加一个TNM_NET约束,把由该时钟驱动的所有同步器件定义为一个分组,然后使用TIMESPEC约束定义时钟周期。

【例1】 周期约束设计实例

NET “usr_clk” TNM_NET= “usr_clk”;

TIMESPEC “TS_usr_clk” = PERIOD “usr_clk” 5.0ns

例1中第一条约束定义时钟usr_clk驱动的所有同步器件为一个分组;第二条约束定义其周期为5ns,即200MHZ

2、I/O时序约束

I/O时序约束定义了时钟和I/O接口之间的时序关系,只用于与I/O接口相连的信号,不能用于内部信号。

I/O时序约束可以约束输入数据、输出数据相对于时钟的时序关系,从而在综合实现中调整布局布线,是正在开发的FPGA的输入建立时间、输出保持时间保持系统要求。

I/O时序约束的语法如下:

OFFSET=IN “offset_time” [units] BEFORE “clk_name” [TIMEGRP “group_name”];

OFFSET=OUT “offset_time” [units] AFTER “clk_name” [TIMEGRP “grout_name”];

说明:

(1)OFFSET、IN、BEFORE是I/O时序约束输入建立时间标识,具体含义为:输入数据与时钟的时序关系满足offset_time定义的时间

(2)OFFSET、OUT、AFTER是I/O时序约束输出保持时间标识,具体含义为:输出数据与时钟的时序关系满足offset_time定义的时间

(3)”offset_time”是约束要求的时间

(4)”clk_name”为参考时钟

(5)[TIMEGRP “grout_name”]为约束的寄存器组。

【例2】I/O时序约束

INST “io_emif_data<0>” TNM=TS_emif_data;

INST “io_emif_data<1>” TNM=TS_emif_data;

INST “io_emif_data<2>” TNM=TS_emif_data;

INST “io_emif_data<3>” TNM=TS_emif_data;

INST “io_emif_data<4>” TNM=TS_emif_data;

INST “io_emif_data<5>” TNM=TS_emif_data;

INST “io_emif_data<6>” TNM=TS_emif_data;

INST “io_emif_data<7>” TNM=TS_emif_data;

NET “IO_emif_clk” TNM_NET= I_emif_clk;

TIMEGRP “TS_emif_data” OFFSET = OUT 7ns AFTER “I_emif_clk”;

例2表示,约束定义TS_emif_data寄存器组与时钟I_emif_clk的关系为时钟有效后7ns输出TS_emif_data寄存器的可靠数据。

3、分组约束

分组约束是将一些具有相同时序要求的器件归为一组,进行相同的时序约束。

分组约束的语法如下:

{NET|INST} “net_name” TNM_NET= [predefined_group] identifier;

{NET|INST|PIN} “net_or_pin_or_inst_name” TNM = [predefined_group] identifier;

(1) INST、NET和PIN为信号,引脚等关键词。

(2) TNM为分组约束关键词

(3) TNM_NET为分组约束关键词,其作用于TNM加在网上是基本相同,即把该网线所在路径上的所有有效同步元件作为命名组的一部分。不同之处在于当TNM约束加在PAD NET 上时,TNM的值将被赋予PAD,而不是该网线所在的路径上的同步元件,即TNM的约束不能穿过IBUF。而用TNM_NET约束就不会出现这种情况。

(4) identifier为标识符

(5) predefined_group为预先定义组标识符

分组约束的例子参见【例2】

4、专门约束

约束文件设计的一般策略是首先设定整体约束,例如PERIOD、OFFSET等,然后对局部的电路附加专门约束,这些专门约束通常比整体约束宽松,通过在可能的地方尽量放松约束可以提高布局布线通过率,减小布局布线的时间。

(1) FROM_TO约束

FROM_TO约束在两个定义的组之间进行时序约束,对两者之间的逻辑和布线延迟进行控制。

语法如下:TIMESPEC “TS_name”= FROM “group1” TO “group2” value;

其中value为延迟时间,可以使具体数值或表达式。

(2) MAXDELAY约束

MAXDELAY约束定义了特定路径上的最大延迟。

语法如下:

NET “net_name” MAXDELAY = value units;

B-布局布线约束

布局布线约束包括引脚约束与位置约束

1、引脚约束

约束FPGA输入输出引脚的具体位置。

引脚约束的语法如下:

NET “net_name” LOC= “PIN”;

说明:

(1) NET,LOC引脚约束关键词

(2) “net_name”为FPGA内部定义的输入输出信号名称;

(3) “PIN”为FPGA实际引脚名称。

【例3】 引脚约束实例

NET “sys_rst_n” LOC= “J12”;

2、位置约束

位置约束是通过约束语法将设计中的某些硬件结构约束到指定的位置。

位置约束的语法如下。

(1) INST “instance_name” LOC=location;

对设计中的硬件约束到具体位置,可以约束的硬件结构包括:寄存器、IOB、LUT、BRAM、乘法器、PLL等。

(2) INST “instance_name” RLOC= location;

对设计中的硬件约束到相对位置, 可约束的硬件结构包括:寄存器、IOB、LUT、BRAM、乘法器、PLL等。必须与RLOC_ORIGIN配套使用。

(3) INST “instance_name” RLOC_ORIGIN =location;

与RLOC对应,指定RLOC的起始位置约束,与RLOC配套使用。

(4) INST “instance_name“ HU_SET=value;

高级属性定义约束,定义独立的组,与RLOC配套使用,以保持结构的完整性。

【例4】 位置约束设计实例1

INST “u_receive_serdes/gtp_dual_i” LOC = GTP_DUAL_X0Y0;

INST “u_idelayctrl” LOC=IDELAYCTRL_X2Y1;

INST “u_en_dqs_ff” LOC=SLICE_X0Y51;

INST “u_iddr_dq_ce” LOC=”ILOGIC_X0Y102;

例4的4个约束分别约束了GTP模块、IDELAYCTRL、SLICE以及ILOGIC.

【例5】 位置约束实例2

INST “delay_inout_u/in1” RLOC_ORIGIN=X00Y60;

INST”delay_inout_u/in1” RLOC=X0Y0;

INST”delay_inout_u/in2” RLOC=X0Y1;

INST”delay_inout_u/*” HU_SET=MA;

例5利用了RLOC_ORIGIN以及RLOC和HU_SET定义了一个相对位置约束。其中*为通配符,指”delay_inout_u/”内所有元件具有的属性。

C-其他约束

除了时序约束以及引脚和位置约束外,Xilinx公司还提供了其他一些约束,例如:

(1) PULLDOWN约束

NET “pad_net_name” PULLDOWN

说明:下拉约束,输出低电平,以避免在无驱动时三态门的输出悬空。

(2) PULLUP约束

NET “pad_net_name” PULLUP

说明:上拉约束,输出高电平,以避免在无驱动时三态门的输出悬空。

(3) IOSTANDARD

NET “pad_net_name” IOSTANDARD = iostandard_name

说明:输入输出引脚电平约束

(4) DRIVE

INST “instance_name” DRIVE= {2|4|6|8|12|16|24};

说明:输出电流能力约束,可选为2mA, 4mA, 6mA, 8mA, 12mA, 16mA, 24mA电流输出,默认值为12mA输出。

(5) SLEW

NET “FAST_OUT” SLEW=”FAST”

说明:输出斜率控制,可选为FAST以及SLOW,可以提高设计的信号完整性。

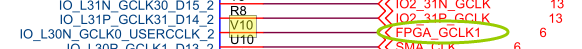

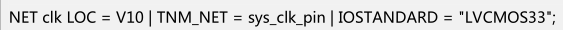

1-普通的I/O只约束管脚和电压

NET “端口名称” LOC = 引脚编号 | IOSTANDARD = “电压”;

例如时钟管脚:

又

从而可以写成:

FPGA管脚约束的更多相关文章

- xilinx Vivado的使用详细介绍(2):创建工程、添加文件、综合、实现、管脚约束、产生比特流文件、烧写程序、硬件验证

xilinx Vivado的使用详细介绍(2):创建工程.添加文件.综合.实现.管脚约束.产生比特流文件.烧写程序.硬件验证 Author:zhangxianhe 新建工程 打开Vivado软件,直接 ...

- (qsf文件 、 tcl文件 和 csv(txt)文件的区别) FPGA管脚分配文件保存、导入导出方法

FPGA管脚分配文件保存方法 使用别人的工程时,有时找不到他的管脚文件,但可以把他已经绑定好的管脚保存下来,输出到文件里. 方法一: 查看引脚绑定情况,quartus -> assignment ...

- quartus2中FPGA管脚分配保存方法(转)

一.摘要 将Quartus II中FPGA管脚的分配及保存方法做一个汇总. 二.管脚分配方法 FPGA 的管脚分配,除了在QII软件中,选择“Assignments ->Pin”标签(或者点击按 ...

- Altera FPGA管脚弱上拉电阻详细设置方法

Altera FPGA管脚弱上拉电阻的软件设置方法 在使用 Altera 的 FPGA 时候, 由于系统需求, 需要在管脚的内部加上上拉电阻. Quartus II 软件中在 Assignment E ...

- FPGA管脚分配文件保存方法

使用别人的工程时,有时找不到他的管脚文件,但可以把他已经绑定好的管脚保存下来,输出到文件里. 方法一: 查看引脚绑定情况,quartus -> assignment -> Pins,打开F ...

- 使用Tcl脚本分配FPGA管脚

自己主动生成Tcl文件 Project -> Generate Tcl File for Project... 弹出例如以下对话框.设置脚本路径. 编辑引脚 使用set_location_ass ...

- FPGA综合的约束

近日发现,有些逻辑电路的综合时间约束和布局布线约束相差太大时,难以布通.此时,应该选择尽量接近的时钟约束.

- 项目小程序笔记-登录界面+FPGA管脚分配文件生成

声明:只是为了记录我遇到的一些问题,其中有我理解错的望勿参考. (1)qt designer设计好窗口 主窗口: 登录窗口: 关于qt designer的使用,大可以百度,很简单的,要注意的是部件的参 ...

- Xilinx FPGA用户约束文件(转自xilinx ISE 开发指南

FPGA设计中的约束文件有3类:用户设计文件(.UCF文件).网表约束文件(.NCF文件)以及物理约束文件(.PCF文件),可以完成时序约束.管 脚约束以及区域约束.3类约束文件的关系为:用户在设计输 ...

随机推荐

- (转)Unity3D占用内存太大的解决方法

自:http://www.cnblogs.com/88999660/archive/2013/03/15/2961663.html 最近网友通过网站搜索Unity3D在手机及其他平台下占用内存太大. ...

- 今天微信小程序发现wx.request不好使了,调试报错: 小程序要求的 TLS 版本必须大于等于 1.2

今天微信小程序发现wx.request不好使了,调试报错: 小程序要求的 TLS 版本必须大于等于 1.2 查官方文档 解决方法 在 PowerShell中运行以下内容, 然后重启服务器 # Enab ...

- cocos2d-x -3.81+win7+vs2013开发环境创建新的项目

cocos2d-x -3.81+win7+vs2013开发环境创建新的项目 1.准备阶段 (1) vs2013下载及安装 (2)cocos2d-x 3.8.1下载及解压 (3)python下载及安装( ...

- Win7没有防火墙:0x80070422

在"MSDN我告诉你"下载的官方原版Window7 64位,安装后防火墙是这样的: 点击"使用推荐设置",报错:0x80070422,估计是因为使用PE中的工具 ...

- ZH奶酪:Ubuntu客户端通过SSH方式远程登录Ubuntu服务器

1.概述 传统的远程登录(telnet,rlogin)时不安全的,他们在网络上用明文传输口令和数据,SSH则是安全的,openssh提供两种级别的验证方式. (1)基于口令的安全验证:知道服务器的帐号 ...

- Java的类名与文件名必须一致(转)

原文:http://blog.csdn.net/shaoxiaoning/article/details/40424087 1.Java保存的文件名必须与类名一致: 2.如果文件中只有一个类,文件名必 ...

- Java多线程(1) 创建

一.线程的生命周期及五种基本状态 关于Java中线程的生命周期,首先看一下以下这张较为经典的图: Java线程具有五中基本状态 新建状态(New):当线程对象对创建后,即进入了新建状态,如:Threa ...

- LDA主题模型浅析

上个月参加了在北京举办SIGKDD国际会议,在个性化推荐.社交网络.广告预测等各个领域的workshop上都提到LDA模型,感觉这个模型的应用挺广泛的,会后抽时间了解了一下LDA,做一下总结: (一) ...

- JavaScript 纯粹对象

JavaScript 纯粹对象 1.定义: 通过 "{}" 或者 "new Object" 创建的对象,像new Date(),new String()都不是纯 ...

- 按部就班——图解配置IIS5的SSL安全访问(转)

作者:mikespook 版本:1.0 最后更新:2004-12-22 16:04 按部就班——图解配置IIS5的SSL安全访问... 1 写在前面的... 1 第一步: 准备工作... ...