clock gating check

在 sta 分析时,经常会碰到 clock gating cell (一般是 ICG cell 或者 latch)引起的 violation,这种 violation 很常见,而且往往很难修。

为什么 gating cell 容易出问题?出了 violation 又该如何解呢?

首先,gating cell 容易出问题是因为其一般出现在 clock path 的中间,而且往往比较靠近 clock source,其latency 较小,当 tool 去check gating cell 的timing 时,其sink point 是在gating cell上,而 CTS 的sink point 是在 gating cell 后面的register, 所以对包含 gating cell 的 path 就会出现:launch clock 较长,而 latch clock 很短的情况,于是导致严重的 setup violation。

################## update 0321 #########################

以 ICG cell 为例,常见的 clock gating check 的 path 如下图:

图中 Reg1 产生 clock enable 信号,用来控制 ICG cell 的开关状态,

在 cts 阶段,tool 在图中会看到两个 sink 点: Reg1/CK, Reg2/CK ,

所以 tool 会对这两个点做 balance,那么做完 cts 后就有: T1 =~ T2 + T3 ;

但是在 sta 时,由于 enable 信号是由 CLK 采集的,所以需要 check 从 Reg1 到 ICG cell 的 timing,

此时 launch clock latency = T1 , capture clock latency = T2,

又因为 T1 =~ T2 + T3 , 所以可以认为 T1 >> T2,

这样 capture clock 就比 launch clock 短很多,很容易出现 setup violation !

那么这种 violation 该怎么解呢?

两种思路: 1) 缩短 data path 或者 launch clock, 2) 垫长 capture clock

首先,垫长 capture clock 不太可行,因为 gating cell 一般都比较靠近 source 点,后面 fanout 较多,影响可能比较大;

而缩短 data path 也不好做到,因为从 start register 到 gating cell 一般比较近,能够缩的余地不大;

所以综合考虑,缩短 launch clock path (即缩短T1)是最佳选择。

缩短 T1 可以用 float pin 来实现,

set_clock_tree_exceptions -float_pin Reg1/CK -float_pin_rise 0.5

甚至可以考虑 抓出所有产生 enable 信号的 register,让它们单独 cts,不要和 gated clock 做 balance

#######################################################

一般 clock gating cell 是 AND 、OR 、latch、ICG ,常见的的一种 gating 结构如下图:

图中的 register 是用于同步 EN 信号,防止出现亚稳态或毛刺

如果将这个 reg 和 AND 封装起来做成单个cell,就是一个简单的 ICG cell。

此外,用 AND 做的 gating cell 容易产生 clock glitch或 clipped clock,原因如下图:

##################################################################

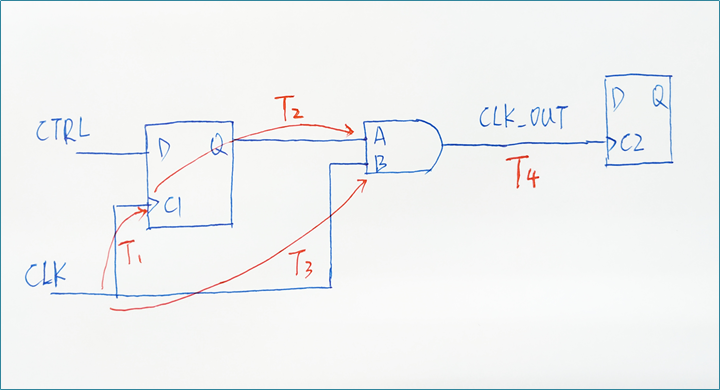

典型的 clock gating check timing path 如下图:

图中gating cell 的 B 端是clk,A 端是 enable,A 端的电平变化可以控制 B 端的 clk 是否送出去,以此控制gating cell 的开关

首先 CTS 是去 balance “从source 到 C1(就是T1)” 和 “从 source 到 C2(就是T3+T4)” 这两段clock,即 T1 =~ T3+T4;而 gating check 时,launch clock path 是 从source到C1(就是T1),而 latch clock path 是 从source到B(就是T3),又因为gate cell 一般靠近source,所以这里 T3 比 T1 小得多,skew 超大,于是 gating check 就会出现较大的 setup violation。

那么这种 violation 改如何解呢?

两种思路: 缩短 data path 或者 launch clock path, 垫长 latch clock path

首先,垫长 latch clock path 不太可行,因为 gating cell 一般都比较靠近 source 点,后面fanout较多,影响可能比较大;

而缩短data path 也不好做到,因为从 start register 到 gating cell 一般比较近,能够缩的余地不大;

所以综合考虑,缩短 launch clock path (即缩短T1)是最佳选择。

缩短 T1 可以用 float pin 来实现,

set_clock_tree_exceptions -float_pin C1 -float_pin_rise 0.5

其它与 clock gating 相关知识:

1. set_clock_gating_check -setup 0.2 开启 gating check 并预留 0.2 的 setup margin,设置这个margin 可以压短 data path

2. DC 综合时可以用 set_clock_gate_latency,在综合时就考虑到 gating path 的 timing 问题

3. gating cell 一般是 AND ,OR ,latch,ICG

clock gating check的更多相关文章

- clock gating and PLL

一个gating的clock是指:clock network除了包含inverter和buffer外,还有其他logic. PrimeTime会自动的对gating input进行setup和hold ...

- clock时钟

①时钟的偏移(skew):时钟分支信号在到达寄存器的时钟端口过程中,都存在有线网等延时,由于延时,到达寄存器时钟端口的时钟信号存在有相位差,也就是不能保证每一个沿都对齐,这种差异称为时钟偏移(cloc ...

- P & R 11

要做好floorplan需要掌握哪些知识跟技能? 首先熟悉data flow对摆floorplan 有好处,对于减少chip的congestion 是有帮助的,但是也不是必需的,尤其是EDA工具快速发 ...

- clock sense和analysis mode

PrimeTime会自动track clock tree中的inverter和buffer,从而得到每个register的clock sense. 如果clock tree中,只有buffer和inv ...

- Universal Asynchronous Receiver/Transmitter

USART簡介與特性 NRZ標準資料格式(Mark/Space) 半雙工/全雙工 Synchronous 同步傳輸 CLOCK SKEW Asynchronous 非同步傳輸 半/全雙工.同步/非同步 ...

- 2. [mmc subsystem] mmc core数据结构和宏定义说明

一.host相关 1.struct mmc_host struct mmc_host是mmc core由host controller抽象出来的结构体,用于代表一个mmc host控制器. 数据结构如 ...

- Linux内核配置选项

http://blog.csdn.net/wdsfup/article/details/52302142 http://www.manew.com/blog-166674-12962.html Gen ...

- 最新内核3.4)Linux 设备树加载I2C client adapter 的流程(内核3.4 高通)【转】

转自:https://blog.csdn.net/lsn946803746/article/details/52515225 版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转 ...

- 从ICG cell 在 library 中的定义说起

如Coding 时需要考虑什么样的代码风格会使gating 的效率更高:综合时需要特别设置要插入的gating 类型,每个gating 的fanout 范围,是否可以跨层次,是否需要做physical ...

随机推荐

- a 链接点击下载

1. 将链接设置为.zip 结尾2.在a元素中添加download 属性,(目前只有chrome.firefox和opera支持) function download(src) { var $a = ...

- centos7 mysql8.0 RPM软件包方式安装

1下载安装包:https://dev.mysql.com/downloads/mysql/8.0.html 2.解压安装包后可以看下如下文件列表 3.在当前目录打开终端 查看并卸载 mariadbrp ...

- 图像矫正-基于opencv实现

一.引言 上篇文章中四种方法对图像进行倾角矫正都非常有效.Hough变换和Radon相似,其抗干扰能力比较强,但是运算量大,程序执行慢,其改进方法为:我们可以不对整幅图像进行操作,可以在图像中选取一块 ...

- <Android 基础(三十一)> ObjectAnimator

简介 ObjectAnimator,是ValueAnimator的子类,支持利用目标视图的属性来实现动画效果.构造ObjectAnimator的时候,将会提取对应的参数来定义动画对象和对象属性.合适的 ...

- json 平面转树状 child [zhuan]

<script> /** * json格式转树状结构 * @param {json} json数据 * @param {String} id的字符串 * @param {String} 父 ...

- Oracle 修改oracle数据库名

Oracle 修改oracle数据库名 by:授客 QQ:1033553122 1.确保你有个可用于数据库恢复的,完整的数据库备份 2.确保数据库处于mount,非open状态,并且在加载前先以imm ...

- input radio单选框样式优化

HTML代码: <form> <div> <input id="item1" type="radio" name="it ...

- 【Python】keras卷积神经网络识别mnist

卷积神经网络的结构我随意设了一个. 结构大概是下面这个样子: 代码如下: import numpy as np from keras.preprocessing import image from k ...

- Ionic模版的使用

Hybird HTML5 App(移动应用开发)之4.Ionic模版的使用 在Windows系统下使Ionic模版,可以使用之前安装的Git工具中的Git Bash.在Mac系统中可以直接使用系统自带 ...

- 【JAVA】使用 jedis操作redis——连接、存储数据、切库等

本篇运用Java调用jedis包(jedis在线文档API ),做简单操作实例. 安装jedis 1. 2.9.0 jar 版本下载: jedis-2.9.0.jar 2. 新建项目,添加该驱动包 连 ...