基于FPGA的通信系统实验

伪随机信号发生器

1、伪随机信号发生器原理

伪随机信号发生器又叫PN序列发生器或者是m序列发生器。m序列是一种线性反馈寄存器序列,m序列的产生可以利用r级寄存器产生长度为2^r-1的m序列,该实验中采用3级寄存器产生7序列发生器。其原理框图如下:(实验中反馈的信号采用异或进行反馈)

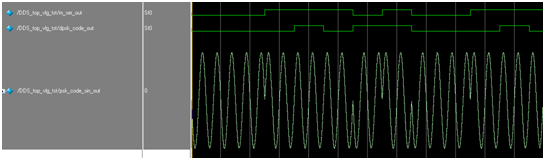

仿真波形:

2、实验代码

|

module m_ser( clk, reset_n, load, m_ser_out ); input clk; input reset_n; input load; output m_ser_out; wire clk; wire reset_n; wire load; reg m_ser_out; ] m_code; always@(posedge clk ornegedge reset_n) begin if(!reset_n) begin m_code<=3'b000; m_ser_out<=1'b0; end else if(load) begin m_code<=3'b001;//置数初始化 ]; end else begin ]; 和0进行异或然后放到0 ]; end end endmodule |

2ASK调制

1、原理

在通信系统中,有时经常需要进行二进制数字调制。2ASK即是二进制幅值键控,2ASK的调制原理就是:基带信号为"0"时,输出保持为"0",基带信号为"1"时,输出一个特定频率的信号,如下图所示:

原理图如下:

2、实验仿真

通过仿真结果可以看出,当data_in输入为高时,调制输出一定频率的信号,输入为低时,调制输出低电平。

3、实验代码

|

module ask( clk, reset_n, data_in, ask_code_out ); input clk; input reset_n; input data_in; output ask_code_out; wire clk; wire reset_n; wire data_in; ]clk_cnt; reg clk_div; always@(posedge clk ornegedge reset_n)//产生分频信号 begin if(!reset_n) begin clk_cnt<=3'd0; clk_div<=1'b0; end else if(clk_cnt==3'd1) begin clk_div<=~clk_div; clk_cnt<=3'd0; end else clk_cnt<=clk_cnt +1'b1; end assign ask_code_out=(data_in)? clk_div :1'b0; endmodule |

2FSK调制

1、原理

2FSK的调制原理是当基带信号为"0"时,输出一个固定频率为f1的信号,当基带信号为"1"时,输出一个固定频率为f2的信号。如下图所示:

原理图如下:

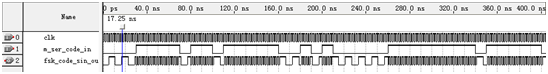

2、实验仿真

3、实验代码

|

module fsk_code( clk, m_ser_code_in, fsk_code_sin_out ); input clk; input m_ser_code_in; output fsk_code_sin_out; wire clk; wire m_ser_code_in; ]cnt; wire f1; reg f2; always@(posedge clk ) begin if(cnt==3'd2) begin cnt<=3'd0; f2<=~f2; end else cnt<=cnt+1'b1; end assign f1=clk; assign fsk_code_sin_out=(m_ser_code_in)? f1:f2; endmodule |

2PSK调制

1、2PSK调制原理

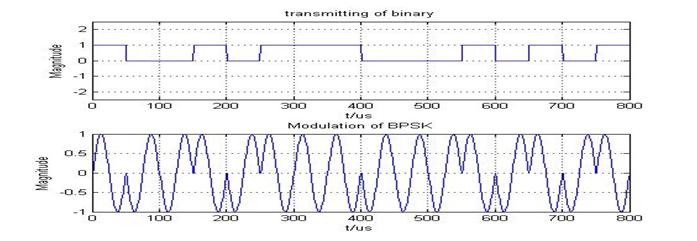

在PSK调制时,载波的相位随调制信号状态不同而改变。如果两个频率相同的载波同时开始振荡,这两个频率同时达到正最大值,同时达到零值,同时达到负最大值,此时它们就处于"同相"状态;如果一个达到正最大值时,另一个达到负最大值,则称为"反相"。一般把信号振荡一次(一周)作为360度。如果一个波比另一个波相差半个周期,我们说两个波的相位差180度,也就是反相。当传输数字信号时,"1"码控制发0度相位,"0"码控制发180度相位。调制原理如下:

在PSK调制时,载波的相位随调制信号状态不同而改变。如果两个频率相同的载波同时开始振荡,这两个频率同时达到正最大值,同时达到零值,同时达到负最大值,此时它们就处于"同相"状态;如果一个达到正最大值时,另一个达到负最大值,则称为"反相"。一般把信号振荡一次(一周)作为360度。如果一个波比另一个波相差半个周期,我们说两个波的相位差180度,也就是反相。当传输数字信号时,"1"码控制发0度相位,"0"码控制发180度相位。调制原理如下:

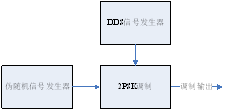

2、实验原理图说明

当伪随机信号发生器输出"1"时,PSK调制输出0度相位的正弦波形;当伪随机信号发生器输出"0"时,PSK调制输出180度相位的正弦波形;在这里,不详细说明"伪随机信号发生器"和"DDS信号发生器的原理",具体可以参考相应的章节。

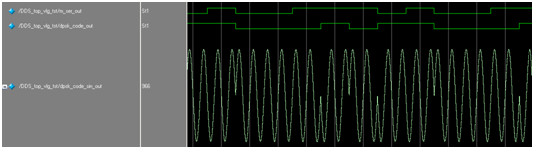

3、仿真效果

采用ModelSim进行仿真:

4、实验代码

|

度相位,"0"码控制发180度相位 module psk_code( clk, m_ser_code_in, dds_sin_data_in2,//10k正弦波 dds_sin_data_in3,//10k正弦波,相位相差180 psk_code_sin_out// ); input clk; input m_ser_code_in; ]dds_sin_data_in2; ]dds_sin_data_in3; ]psk_code_sin_out; wire clk; wire m_ser_code_in; ]dds_sin_data_in2; ]dds_sin_data_in3; assign psk_code_sin_out=(m_ser_code_in)? dds_sin_data_in2:dds_sin_data_in3; endmodule |

2DPSK调制

1、2DPSK原理

在2PSK中,是利用载波相位的绝对数值来传送数字信息,因而称为绝对调相;2DPSK即是二进制差分相移键控,不利用载波相位传送数字信息,而是利用前后码元的相对相位变化传送数字信息。

实现相对调相的常用方法有:先对数字基带信号进行差分编码,将绝对编码转换成差分编码,然后再进行绝对调相。

将数字基带信号由绝对编码转成差分编码的方法为:将前一个输出码元和当前的输入码元进行异或,这样就可以产生相对码。

其原理图为:

2、实验设计

将伪随机信号发生器产生的m序列进行差分编码,再将相对码进行2DPSK调制,当出现"0"码则输出0度相位正弦波,"1"码控制发180度相位正弦波。

3、实验仿真

将绝对编码转为相对编码

2DPSK调制:

4、实验代码

|

度相位,"1"码控制发180度相位 module dpsk_code( clk, reset_n,// m_ser_code_in,//PN序列输入 dpsk_code_out,//dpsk调制输出 dds_sin_data_in2,//10k正弦波 dds_sin_data_in3,//10k正弦波,相位相差180 dpsk_code_sin_out ); input clk; input reset_n; input m_ser_code_in; ] dds_sin_data_in2; ] dds_sin_data_in3; output dpsk_code_out; ]dpsk_code_sin_out; wire clk; wire reset_n; wire m_ser_code_in; ] dds_sin_data_in2; ] dds_sin_data_in3; reg dpsk_code_reg; //差分编码 always@(posedge clk ornegedge reset_n) begin if(!reset_n) begin dpsk_code_reg<=1'b0; end else dpsk_code_reg<=dpsk_code_reg ^ m_ser_code_in;//前一个码元与输入的码元进行异或 end assign dpsk_code_out=dpsk_code_reg; assign dpsk_code_sin_out=(dpsk_code_reg)? dds_sin_data_in3 : dds_sin_data_in2; endmodule |

每日推送不同科技解读,原创深耕解读当下科技,敬请关注微信公众号“科乎”。

基于FPGA的通信系统实验的更多相关文章

- 基于FPGA的飞机的小游戏

基于FPGA的飞机的小游戏 实验原理 该实验主要分为4个模块,采用至上而下的设计方法进行设计.由50M的晶振电路提供时钟源,VGA显示控制模块.图形显示控制模块.移动模块的时钟为25M,由时钟分频电路 ...

- 基于SoCkit的opencl实验1-基础例程

基于SoCkit的opencl实验1-基础例程 准备软硬件 Arrow SoCkit Board 4GB or larger microSD Card Quartus II v14.1 SoCEDS ...

- 基于FPGA的图像去噪

目录 结构图 其中FPGA 控制模块为核心,通过它实现视频图像数据的获取.缓存.处理和控制各模块间通讯[1].由CCD 相机对目标成像,高速图像数据由camera link 实时传输[2],经信号转换 ...

- 基于FPGA的IIR滤波器

基于FPGA的IIR滤波器 by方阳 版权声明:本文为博主原创文章,转载请指明转载地址 ...

- 基于FPGA的VGA显示静态图片

终于熬到暑假了,记过三四周的突击带考试,终于为我的大二画上了一个完整的句号,接下来终于可以静心去做自己想做的事情了,前一阵子报了一个线上培训班,学学Sobel边缘检测,之前一直在学习图像处理,但是因为 ...

- 基于FPGA的Uart接收图像数据至VGA显示

系统框图 前面我们设计了基于FPGA的静态图片显示,接下来我们来做做基于FPGA的动态图片显示,本实验内容为:由PC端上位机软件通过串口发送一幅图像数据至FPGA,FPGA内部将图像数据存储,最后扫描 ...

- 基于FPGA的中值滤波算法实现

在这一篇开篇之前,我需要解决一个问题,上一篇我们实现了基于FPGA的均值滤波算法的实现,最后的显示效果图上发现有一些黑白色的斑点,我以为是椒盐噪声,然后在做基于FPGA的中值滤波算法的实验时,我发现黑 ...

- 基于FPGA的肤色识别算法实现

大家好,给大家介绍一下,这是基于FPGA的肤色识别算法实现. 我们今天这篇文章有两个内容一是实现基于FPGA的彩色图片转灰度实现,然后在这个基础上实现基于FPGA的肤色检测算法实现. 将彩色图像转化为 ...

- 基于FPGA的数字识别的实现

欢迎大家关注我的微信公众号:FPGA开源工作室 基于FPGA的数字识别的实现二 作者:lee神 1 背景知识 1.1基于FPGA的数字识别的方法 通常,针对印刷体数字识别使用的算法有:基于模版 ...

随机推荐

- MFC MDI 获取当前视图

==================================声明================================== 本文原创,转载在正文中显要的注明作者和出处,并保证文章的完 ...

- IO系统性能之一:衡量性能的几个指标

作为一个数据库管理员,关注系统的性能是日常最重要的工作之一,而在所关注的各方面的性能只能IO性能却是最令人头痛的一块,面对着各种生涩的参数和令人眼花缭乱的新奇的术语,再加上存储厂商的忽悠,总是让我们有 ...

- C++杂谈(二)初识vector容器与迭代器

教科书中失踪的vector 很奇怪的一件事情,在当时学习C++的时候,老师并没有讲授容器的内容,当时参考的谭浩强老师的红皮C++也没有这个内容,不知为何.后来再学C++,发现容器是一个很重要的概念,在 ...

- IE6-9不支持Textarea的maxlength属性

给textarea标签添加一个maxlength=200,测试工程师提bug说IE9没起作用.后一测试,发现IE10一下的浏览器均不支持 <textarea maxlength="20 ...

- mysql服务器配置

mysql的配置文件 /etc/mysql/my.cnf 发现如下配置 # Instead of skip-networking the default is now to listen only ...

- System V IPC(2)-信号量

一.概述 System V信号量与System V消息队列不同.它不是用来在进程间传递数据.它主要 ...

- Windows 10 L2TP 809错误

今天不知道为什么,一直工作正常的L2TP不能连接了.我用的是Surface Pro 3,Windows 10 专业版,操作系统一直保持自动更新,而且最近也没有安装什么软件.点击连接后,等一段时间就报8 ...

- ajax小结

1. http是一种无状态协议 2. http请求:四部分组成 ① http 请求的方法或动作,如:GET / POST ② 正在请求的URL,总得知道请求的地址是什么 ③ 请求头,包含一些客户端环境 ...

- 给IIS添加CA证书以支持https

一.在IIS中生成Certificate Signing Request (CSR) 个人理解:生成CSR就是生成“私钥/公钥对”之后从中提取出公钥. 1. 打开IIS Manager,在根节点中选择 ...

- 【HTML5】标记文字

1.用基本的文字元素标记内容 先看显示效果: 对应HTML代码: <!DOCTYPE html> <html lang="en"> <head> ...