fpga串口通信

串口的全程为串行接口,也称为串行通信接口,是采用串行通信方式的扩展接口。与串口对应的并行接口,例如高速AD和DA,

这些都是用的并行接口,而且在编程也简单一些。

串口有一下特点:

(1)通信线路简单,只要一对传输线就可以实现双向通信。

(2)布线简单,成本低。

(3)通信距离长,可以实现数米到数千米的通信距离。

(4)传输速率慢。

常见的串口速率如4800 , 9600 , 115200bps,代表每秒钟发送多少bit数据,例如9600bps就代表1秒内发送9600bit数据。

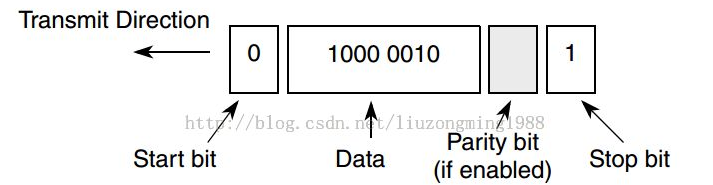

串口协议 : 协议比较简单,一般都是10位数据,1个起始位 低电平 ,然后八个数据位,低位在前,一个奇偶校验位,平时

一般不用,最后是一位停止位高电平,这样一帧数据发送结束。

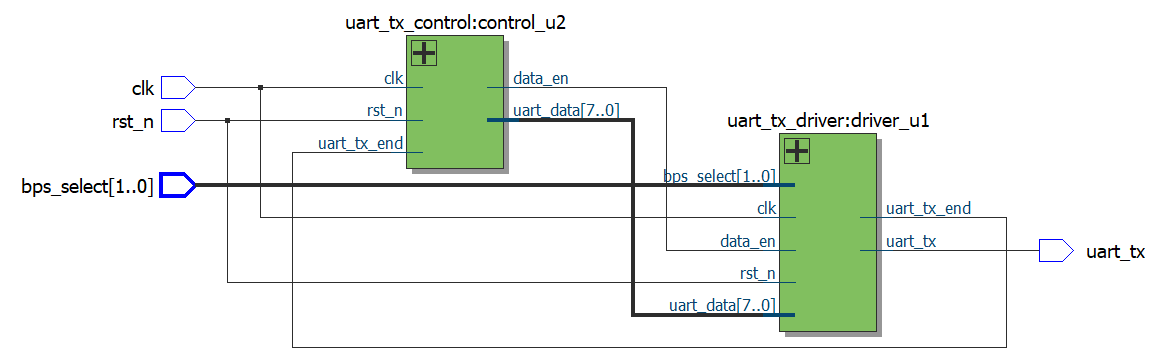

下面介绍一下我的程序框架:

整体框架分为两个部分:一个是串口驱动部分 另一个是串口数据控制部分。串口驱动部分负责串口驱动和波特率的选择,串口数据控制模块

负责控制数据内容的控制和发送速度的控制。

从上面时序图可以看出,每10ms发送一帧数据,这里data_en负责波特率驱动使能,uart_tx_end有两个功能,一个是关闭data_en使能,另一个是给10ms计数器

清零。

/*----------------------------------------------------------------------- Date : 2017-09-03

Description : Design for uart_driver. -----------------------------------------------------------------------*/ module uart_tx_driver

(

//global clock

input clk , //system clock

input rst_n , //sync reset //uart interface

output reg uart_tx , //user interface

input [:] bps_select , //波特率选择

input [:] uart_data ,

input data_en , //发送数据使能

output reg uart_tx_end

); //--------------------------------

//Funtion : 参数定义 parameter BPS_4800 = 'd10417 ,

BPS_9600 = 'd5208 ,

BPS_115200 = 'd434 ; reg [:] cnt_bps_clk ;

reg [:] bps ;

reg bps_clk_en ; //bps使能时钟

reg [:] bps_cnt ;

wire [:] BPS_CLK_V = bps >> ;

//--------------------------------

//Funtion : 波特率选择 always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

bps <= 'd0;

else if(bps_select == 'd0)

bps <= BPS_115200;

else if(bps_select == 'd1)

bps <= BPS_9600;

else

bps <= BPS_4800;

end //--------------------------------

//Funtion : 波特率计数 always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt_bps_clk <= 'd0;

else if(cnt_bps_clk >= bps - && data_en == 'b0)

cnt_bps_clk <= 'd0;

else

cnt_bps_clk <= cnt_bps_clk + 'd1;

end //--------------------------------

//Funtion : 波特率使能时钟 always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

bps_clk_en <= 'd0;

else if(cnt_bps_clk == BPS_CLK_V - )

bps_clk_en <= 'd1;

else

bps_clk_en <= 'd0;

end //--------------------------------

//Funtion : 波特率帧计数 always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

bps_cnt <= 'd0;

else if(bps_cnt == )

bps_cnt <= 'd0;

else if(bps_clk_en)

bps_cnt <= bps_cnt + 'd1;

end //--------------------------------

//Funtion : uart_tx_end always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

uart_tx_end <= 'd0;

else if(bps_cnt == )

uart_tx_end <= 'd1;

else

uart_tx_end <= 'd0;

end //--------------------------------

//Funtion : 发送数据 always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

uart_tx <= 'd1;

else case(bps_cnt)

'd0 : uart_tx <= 1'd1; 'd1 : uart_tx <= 1'd0; //begin

'd2 : uart_tx <= uart_data[0];//data

'd3 : uart_tx <= uart_data[1];

'd4 : uart_tx <= uart_data[2];

'd5 : uart_tx <= uart_data[3];

'd6 : uart_tx <= uart_data[4];

'd7 : uart_tx <= uart_data[5];

'd8 : uart_tx <= uart_data[6];

'd9 : uart_tx <= uart_data[7]; 'd10 : uart_tx <= 1; //stop

default : uart_tx <= ;

endcase

end endmodule

/*----------------------------------------------------------------------- Date : 2017-XX-XX

Description : Design for . -----------------------------------------------------------------------*/ module uart_tx_control

(

//global clock

input clk , //system clock

input rst_n , //sync reset //user interface

output reg [:] uart_data ,

output reg data_en ,

input uart_tx_end ); //--------------------------------

//Funtion : 参数定义 parameter DELAY_10MS = 500_000 ;

reg [:] cnt_10ms ;

wire delay_10ms_done ; //data define

reg [:] cnt_1s; //--------------------------------

//Funtion : cnt_10ms always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt_10ms <= 'd0;

else if(cnt_10ms == DELAY_10MS - && uart_tx_end == 'd1)

cnt_10ms <= 'd0;

else

cnt_10ms <= cnt_10ms + 'd1;

end assign delay_10ms_done = (cnt_10ms == DELAY_10MS - ) ? 'd1 : 1'd0; //--------------------------------

//Funtion : data_en always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

data_en <= 'd0;

else if(delay_10ms_done)

data_en <= 'd1;

else if(uart_tx_end)

data_en <= 'd0;

end ///////////////////////数据测试/////////////////////////////

//--------------------------------

//Funtion : cnt_1s always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt_1s <= 'd0;

else if(cnt_1s == 49_999_999)

cnt_1s <= 'd0;

else

cnt_1s <= cnt_1s + 'd1;

end //--------------------------------

//Funtion : uart_data always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

uart_data <= 'd0;

else if(uart_data >= )

uart_data <= 'd0;

else if(cnt_1s == 49_999_999)

uart_data <= uart_data + 'd1;

end endmodule

fpga串口通信的更多相关文章

- 基于FPGA的红外遥控解码与PC串口通信

基于FPGA的红外遥控解码与PC串口通信 zouxy09@qq.com http://blog.csdn.net/zouxy09 这是我的<电子设计EDA>的课程设计作业(呵呵,这个月都拿 ...

- PC和FPGA间的串口通信实现

应用笔记 V1.0 2015/03/26 PC和FPGA间的串口通信实现 概述 本文将介绍PC和FPGA间的串口通信实现的基本思路和Verilog代码,对于通信而言,收发双方都要有相应的控制. ...

- FPGA串口波特率简析

以前用单片机,一直都是直接用就行,设置波特率时,直接写9600就行,一直没有仔细考虑过,今天打算用FPGA写个串口程序时才知道,原来根本就是没弄明白.一下是我的一些见解.如果诸位看官觉得不对,欢迎指正 ...

- RS232串口通信

RS232串口经常使用在PC机与FPGA通信中,用于两者之间的数据传输,因为UART协议简单.易实现,故经常使用. DB9接口只需要使用3根线,RXD(2).TXD(3)和GND(5),如下图所示.而 ...

- .NET 串口通信

这段时间做了一个和硬件设备通信的小项目,涉及到扫描头.输送线.称重机.贴标机等硬件.和各设备之间通信使用的是串口或网络(Socket)的方式.扫描头和贴标机使用的网络通信,输送线和称重机使用的是串口通 ...

- BluetoothChat用于蓝牙串口通信的修改方法

本人最近在研究嵌入式的串口通信,任务是要写一个手机端的遥控器用来遥控双轮平衡小车.界面只用了一个小时就写好了,重要的问题是如何与板子所带的SPP-CA蓝牙模块进行通信. SPP-CA模块自带代码,在这 ...

- Win10 IoT C#开发 4 - UART 串口通信

Windows 10 IoT Core 是微软针对物联网市场的一个重要产品,既可以开发设备UI与用户交互式操作,又可以控制GPIO等接口,使得原来嵌入式繁琐的开发变得简单.通过Remote Debug ...

- 使用Java实现简单串口通信

最近一门课要求编写一个上位机串口通信工具,我基于Java编写了一个带有图形界面的简单串口通信工具,下面详述一下过程,供大家参考 ^_^ 一: 首先,你需要下载一个额外的支持Java串口通信操作的jar ...

- Java 串口通信

在Windows系统下,用Java开发串口通信相关的程序时,需要用到几个文件. (1)win32com.dll 要放在jdk\jre\bin目录下. (2)comm.jar 和javax.comm.p ...

随机推荐

- MVC使用RDL报表

MVC使用RDL报表 这次我们来演示MVC3怎么显示RDL报表,坑爹的微软把MVC升级到5都木有良好的支持报表,让MVC在某些领域趋于短板 我们只能通过一些方式来使用rdl报表. Razor视图不支持 ...

- 了解你的被测系统(why?)

了解你的被测系统(why?) 如何做好系统集成测试[二.了解你的被测系统] 如果看完了第一篇文章,你的答案是Yes.我们可以继续讨论如何做系统集成测试啦. 了解你的被测系统(why?) 一如既 ...

- c# 自定义多选下拉列表2

以下为工作中遇到的,备注一下 先需要几个辅助类 #region GripBounds using System.Drawing; internal struct GripBounds { ; ; pu ...

- hive left outer join的问题

最近BA用户反馈有两句看似很像的语句返回的结果数不一样,比较奇怪,怀疑是不是Hive的Bug Query 1 返回结果数6071 select count(distinct reviewid) as ...

- 【DOS】这个命令太牛逼了

删除一个程序了后 竟然上不了网了 运行下列命令重启后就可以了 实在是救了我系统一命 命令如下: netsh winsock reset

- easyui datagrid自定义操作列

通过formatter方法给Jquery easyui 的datagrid 每行增加操作链接 我们都知道Jquery的EasyUI的datagrid可以添加并且自定义Toolbar, 这样我们选择一行 ...

- 案例研究:Web应用出现间歇性的SqlException

案例研究:Web应用出现间歇性的SqlException 2013-07-29 14:36 by 微软互联网开发支持, 231 阅读, 3 评论, 收藏, 编辑 最近有客户找到我,说他们生产环境的事件 ...

- 桥接模式及C++实现 C++设计模式-AbstractFactory抽象工厂模式

桥接模式及C++实现 桥接模式 先说说桥接模式的定义:将抽象化(Abstraction)与实现化(Implementation)分离,使得二者可以独立地变化. 桥接模式号称设计模式中最难理解的模式之一 ...

- [Android学习笔记4]四大应用组件之一:Service 上

一.什么是Service 一个Service就是一个能够在后台执行长时操作的应用程序组件,并且不提供用户界面.一个应用程序组件能够启动一个Service,即使用户切换到另一个应用程序,这个Servic ...

- 【Linux】CentOS 学习笔记之二(命令)

打开文件夹: cd finename 创建目录:mkdir /filename mkdir -p /test/123/111 (多级目录) 删除目录: rmdir 删除目录或文件: r ...