学会使用Hdlbits网页版Verilog代码仿真验证平台

给大家推荐一款网页版的 Verilog代码编辑仿真验证平台,这个平台是国外的一家开源FPGA学习网站,通过“https://hdlbits.01xz.net/wiki/Main_Page” 地址链接进入网页,在该网页上可以进行Verilog代码的编写、综合,而且最后还能够仿真出波形来验证设计代码的正确性,该验证平台是基于Icarus Verilog(简称iVerilog,比较著名的开源HDL仿真工具,也有对应的安装版本)的,让你随时随地只需登录网页就能够享受Verilog编程仿真的乐趣!

一、官方模板演示

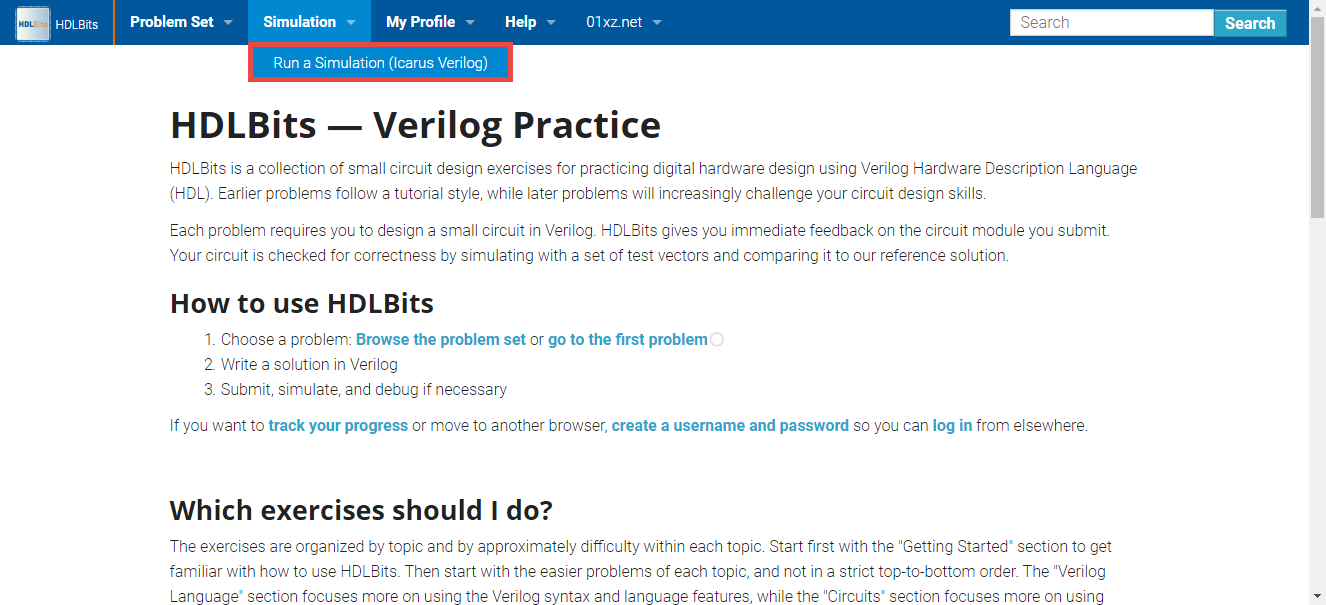

1、首先打开“https://hdlbits.01xz.net/wiki/Main_Page”,打开后的界面如下图所示,全英文显示。如果感觉自己的英文水平欠佳,可以使用谷歌浏览器打开该网页,并选择在线翻译功能,翻译的正确率还是很高的。

2、点击Simulation下的 ”Run a Simulation(lcarus Verilog)“。

3、打开后的界面如下图所示,代码编辑框中给出了一个简单的例子。

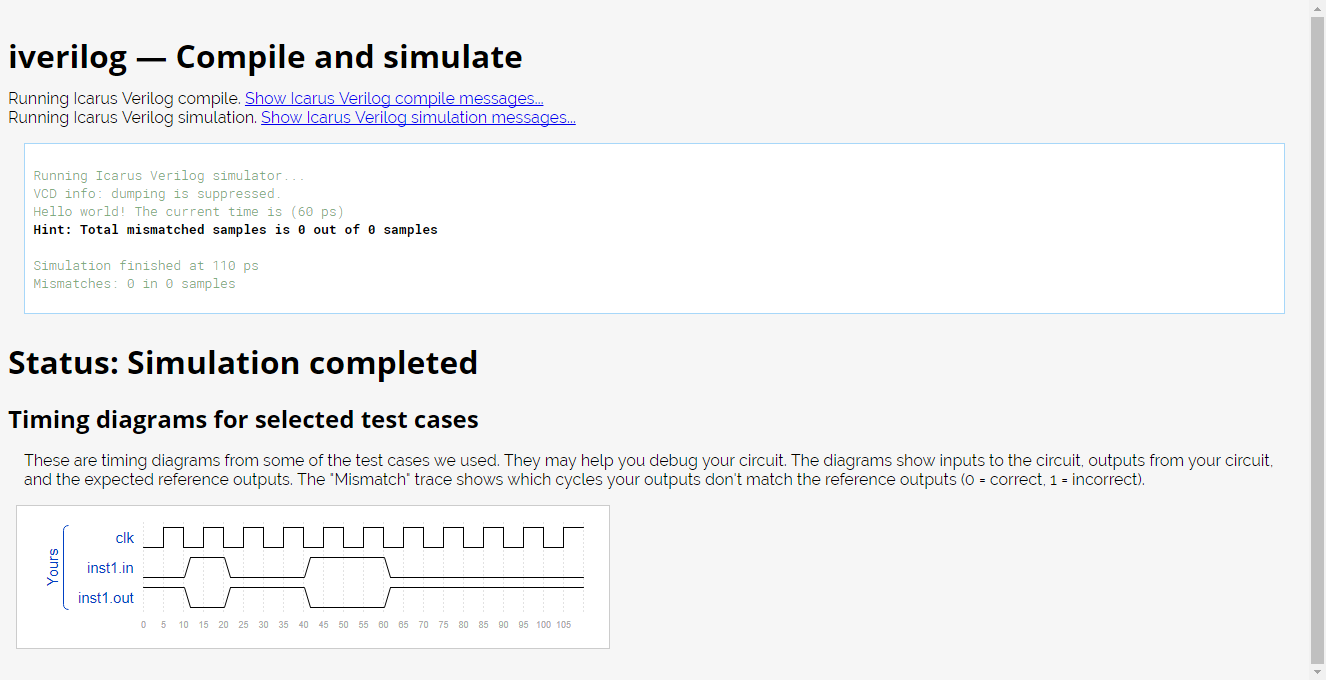

4、点击下面的“Submit(new window)“在新界面中进行仿真。

5、在新打开的界面中我们可以看到编译的信息和仿真波形图。

二、实例演示

虽然看完了官方的模板演示,但我们要想立刻仿真验证自己设计的代码并不是那么容易,需要进行一番摸索。下面就是大家进行一个呼吸灯的设计实例演示。

1、学习过FPGA的朋友都知道要想对FPGA逻辑进行仿真一定要具备两个文件,一个是RTL代码文件,用来综合生成硬件电路的部分;第二个就是Testbench文件,用来验证RTL代码功能的仿真文件,这两者缺一不可。

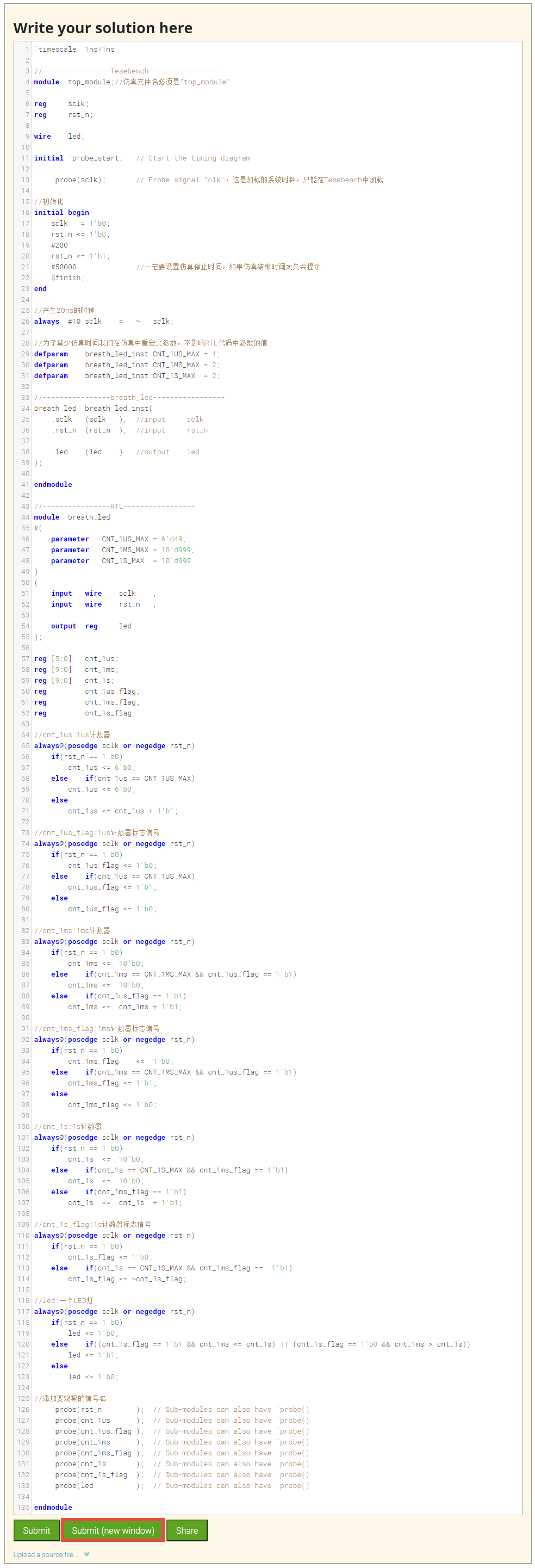

2、根据观察发现官方模板中的代码编辑部分有两个module,大家也都知道一个.v 文件中只能有一个模块,也就是只能有一个module,而这里面有两个,那肯定就不对了。再仔细观察会发现代码编辑区域中的上半部分就是Testbench,而下半部分则是RTL代码,再结合仿真出的波形来更看验证了这个想法。原来 RTL 代码和Testbench都写在了一个编辑框里。

3、但是我们在提供的模板中发现一些我们平时几乎没有见过的新语法,如第4行的”initial `probe_start“、第6行的”`probe(clk)“、第26行的”`probe(in)“,通过模板的注释和多次实验发现这是官方定义的一个”宏“,也就是通过这个”宏“调用“probe”探针的功能,我们不用管这个”宏“是如何定义的,我们只需要会调用就可以了。

4、下面我们通过该网页来仿真验证一下自己设计的呼吸灯的例子。详细代码如下(呼吸灯逻辑和Testbench代码的编写方法这里我们不做讲解,会在以后的文章中再进行详细说明),下面代码可以全部直接复制使用(代码中的注释请详细阅读)。

`timescale 1ns/1ns //----------------Tesebench-----------------

module top_module; //仿真文件名必须是“top_module” reg sclk;

reg rst_n; wire led; initial `probe_start; // Start the timing diagram `probe(sclk); // Probe signal "clk",这是加载的系统时钟,只能在Tesebench中加载 //初始化

initial begin

sclk = 'b0;

rst_n <= 'b0;

#

rst_n <= 'b1;

# //一定要设置仿真停止时间,如果仿真结束时间太久会提示

$finish;

end //产生20ns的时钟

always #10 sclk = ~sclk; //为了减少仿真时间我们在仿真中重定义参数,不影响RTL代码中参数的值

defparam breath_led_inst.CNT_1US_MAX = ;

defparam breath_led_inst.CNT_1MS_MAX = ;

defparam breath_led_inst.CNT_1S_MAX = ; //----------------breath_led-----------------

breath_led breath_led_inst(

.sclk (sclk ), //input sclk

.rst_n (rst_n), //input rst_n .led (led ) //output led

); endmodule //----------------RTL-----------------

module breath_led

#(

parameter CNT_1US_MAX = 'd49,

parameter CNT_1MS_MAX = 'd999,

parameter CNT_1S_MAX = 'd999

)

(

input wire sclk ,

input wire rst_n , output reg led

); reg [:] cnt_1us;

reg [:] cnt_1ms;

reg [:] cnt_1s;

reg cnt_1us_flag;

reg cnt_1ms_flag;

reg cnt_1s_flag; //cnt_1us:1us计数器

always@(posedge sclk or negedge rst_n)

if(rst_n == 'b0)

cnt_1us <= 'b0;

else if(cnt_1us == CNT_1US_MAX)

cnt_1us <= 'b0;

else

cnt_1us <= cnt_1us + 'b1; //cnt_1us_flag:1us计数器标志信号

always@(posedge sclk or negedge rst_n)

if(rst_n == 'b0)

cnt_1us_flag <= 'b0;

else if(cnt_1us == CNT_1US_MAX)

cnt_1us_flag <= 'b1;

else

cnt_1us_flag <= 'b0; //cnt_1ms:1ms计数器

always@(posedge sclk or negedge rst_n)

if(rst_n == 'b0)

cnt_1ms <= 'b0;

else if(cnt_1ms == CNT_1MS_MAX && cnt_1us_flag == 'b1)

cnt_1ms <= 'b0;

else if(cnt_1us_flag == 'b1)

cnt_1ms <= cnt_1ms + 'b1; //cnt_1ms_flag:1ms计数器标志信号

always@(posedge sclk or negedge rst_n)

if(rst_n == 'b0)

cnt_1ms_flag <= 'b0;

else if(cnt_1ms == CNT_1MS_MAX && cnt_1us_flag == 'b1)

cnt_1ms_flag <= 'b1;

else

cnt_1ms_flag <= 'b0; //cnt_1s:1s计数器

always@(posedge sclk or negedge rst_n)

if(rst_n == 'b0)

cnt_1s <= 'b0;

else if(cnt_1s == CNT_1S_MAX && cnt_1ms_flag == 'b1)

cnt_1s <= 'b0;

else if(cnt_1ms_flag == 'b1)

cnt_1s <= cnt_1s + 'b1; //cnt_1s_flag:1s计数器标志信号

always@(posedge sclk or negedge rst_n)

if(rst_n == 'b0)

cnt_1s_flag <= 'b0;

else if(cnt_1s == CNT_1S_MAX && cnt_1ms_flag == 'b1)

cnt_1s_flag <= ~cnt_1s_flag; //led:一个LED灯

always@(posedge sclk or negedge rst_n)

if(rst_n == 'b0)

led <= 'b0;

else if((cnt_1s_flag == 'b1 && cnt_1ms <= cnt_1s) || (cnt_1s_flag == 1'b0 && cnt_1ms > cnt_1s))

led <= 'b1;

else

led <= 'b0; //添加要观察的信号名

`probe(rst_n ); // Sub-modules can also have `probe()

`probe(cnt_1us ); // Sub-modules can also have `probe()

`probe(cnt_1us_flag); // Sub-modules can also have `probe()

`probe(cnt_1ms ); // Sub-modules can also have `probe()

`probe(cnt_1ms_flag); // Sub-modules can also have `probe()

`probe(cnt_1s ); // Sub-modules can also have `probe()

`probe(cnt_1s_flag ); // Sub-modules can also have `probe()

`probe(led ); // Sub-modules can also have `probe() endmodule

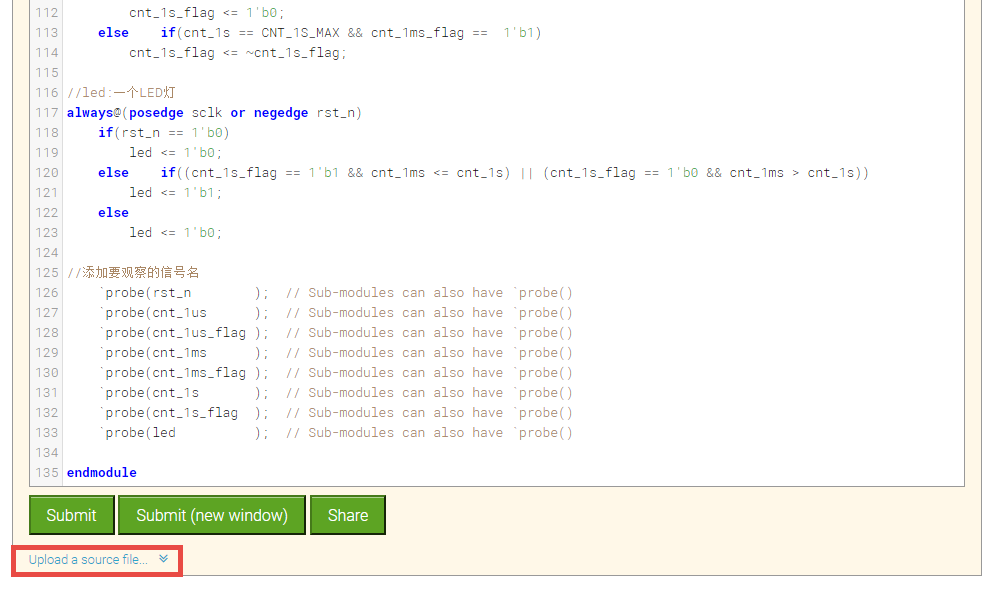

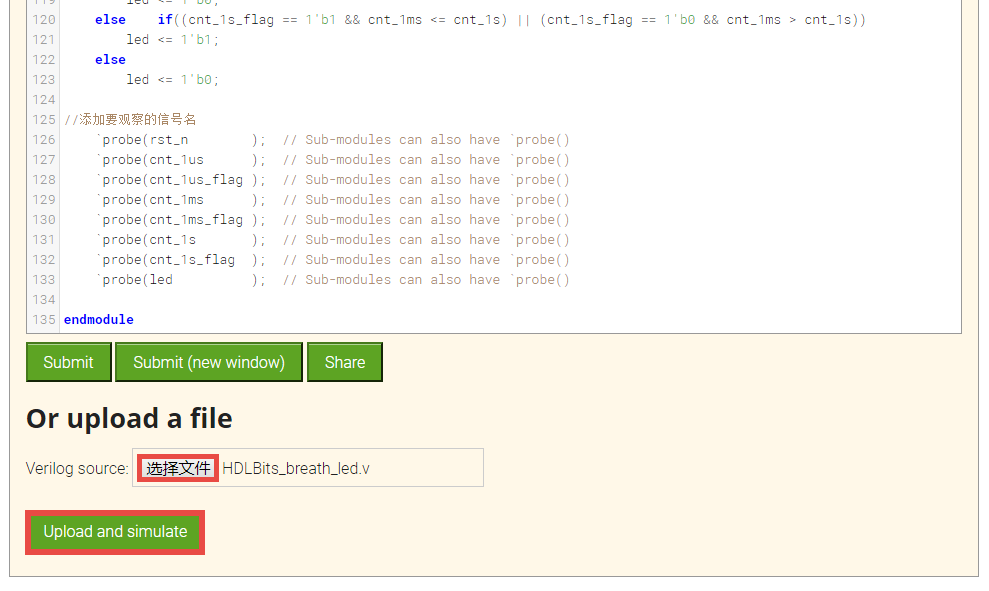

5、将上面编写好的Testbench代码和RTL代码放到一个文件中(Testbench在上面,RTL代码在下面,仅在该平台仿真时可以将两种文件放在一起,在其他平台仿真时要独立放到两个.v文件中),然后复制粘贴到代码编辑框中,点击“Submit(new window)“执行仿真。

6、也可以将写好的Testbench代码和RTL代码放到同一个.v文件中,然后点击下面的代码编辑框下面的“Upload a source file...”,在展开的界面中选择添加.v文件后,再点击”Upload and simulate”启动仿真。

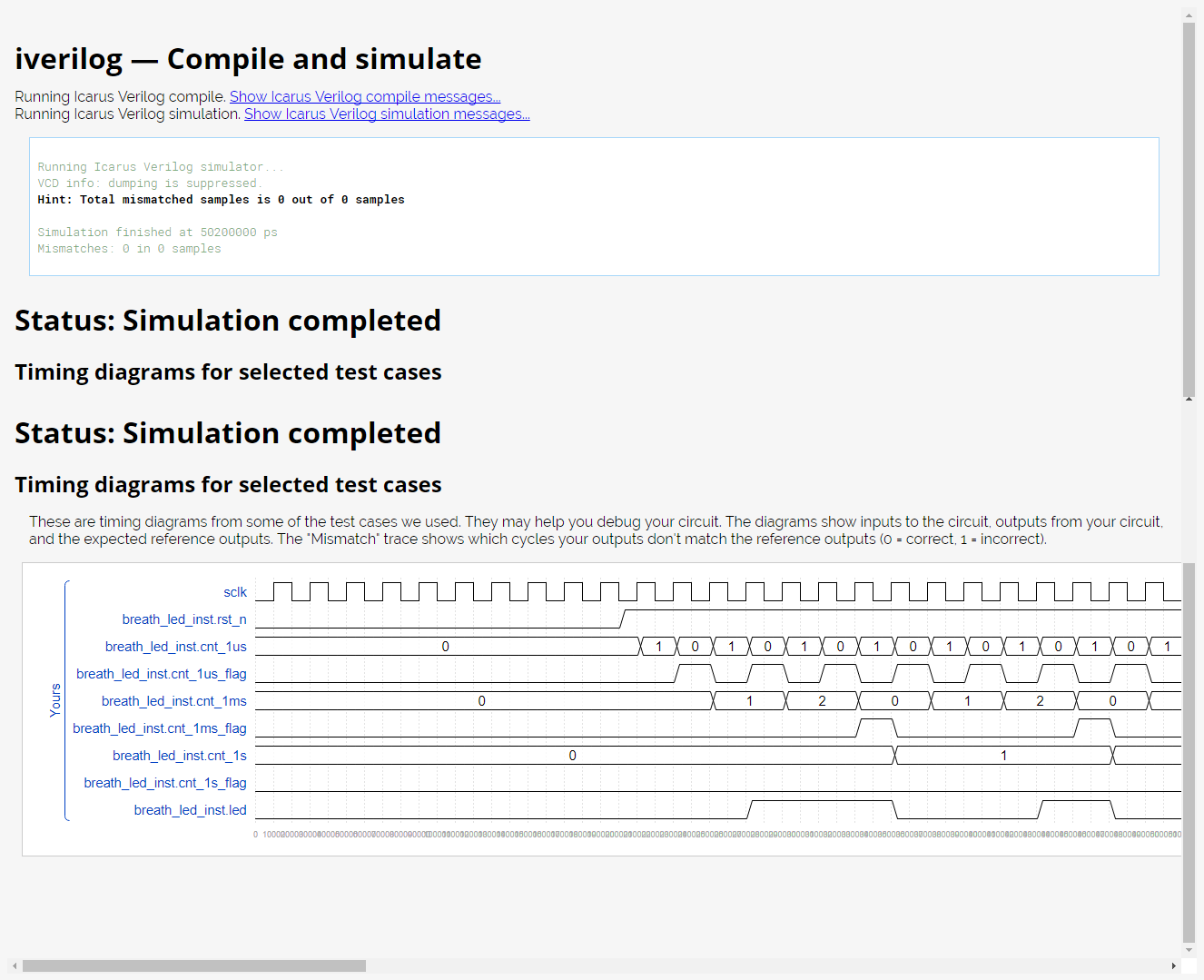

7、仿真波形如下所示,因为界面空间有限,拖动波形显示框下面的滚动条,可以看到后面的波形显示。

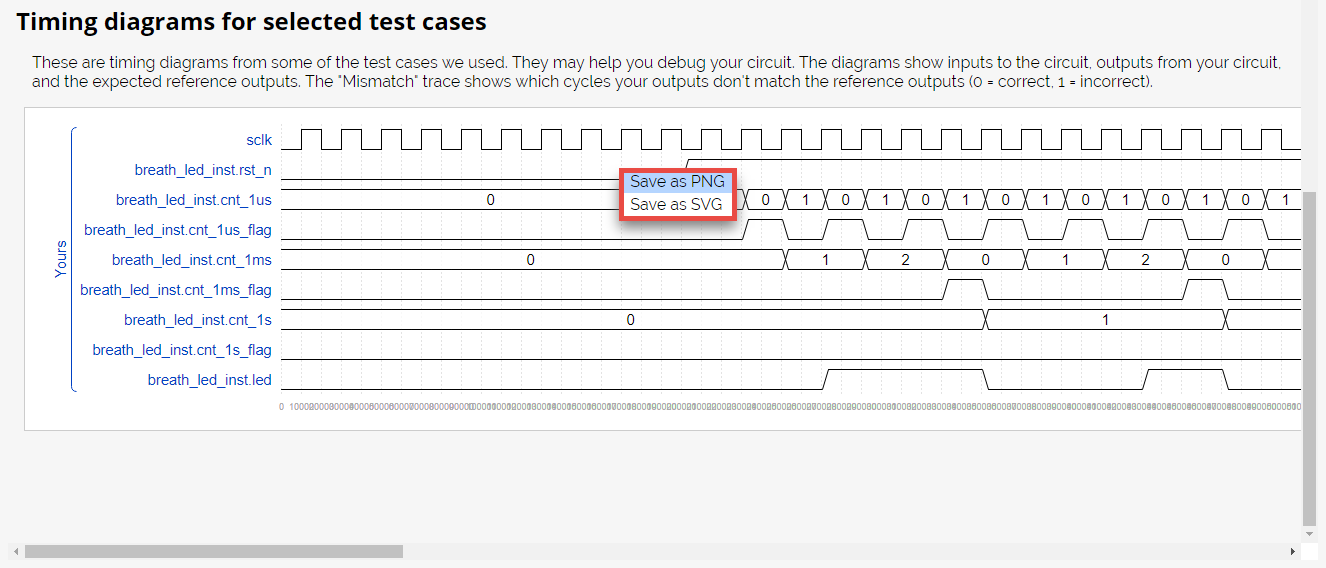

8、在波形显示框中右击鼠标可以选择保存为PNG格式或SVG格式,将完整的波形信息保存下来。

9、保存为SVG格式后的完整波形图如下所示。

10、如果我们在第58行处代码设置一个错误后,再点击执行仿真,此时在仿真窗口中不会显示波形,而是提示错误的内容,将错误修改后再执行仿真即可。

11、该网页还有其他更多有趣的功能,如组合逻辑代码编写训练、时序逻辑代码编写训练、单片机嵌入式仿真等等,有兴趣的朋友可以自己探索,这里不再一一演示。

欢迎加入FPGA技术学习交流群,本群致力于为广大FPGAer提供良好的学习交流环境,不定期提供各种本行业相关资料!

QQ交流群号:450843130

学会使用Hdlbits网页版Verilog代码仿真验证平台的更多相关文章

- verilog代码 想法验证---与寄存器输出有关

verilog代码 想法验证---与寄存器输出有关 1. module test_mind( input wire clk, input wire reset, input wire i, outpu ...

- verilog 代码分析与仿真

verilog 代码分析与仿真 注意:使用vivado 自带的仿真工具, reg和wire等信号需要赋予初始值 边沿检测 module signal_test( input wire cmos_pcl ...

- 基于jQuery仿QQ音乐播放器网页版代码

基于jQuery仿QQ音乐播放器网页版代码是一款黑色样式风格的网页QQ音乐播放器样式代码.效果图如下: 在线预览 源码下载 实现的代码. html代码: <div class="m ...

- jQuery实践-别踩白块儿网页版

▓▓▓▓▓▓ 大致介绍 终于结束了考试,放假回家了.这次的别踩白块儿网页版要比之前做的 jQuery实践-网页版2048小游戏 要简单一点,基本的思路都差不多. 预览:别踩白块网页版 这篇博客并不是详 ...

- jQuery实践-网页版2048小游戏

▓▓▓▓▓▓ 大致介绍 看了一个实现网页版2048小游戏的视频,觉得能做出自己以前喜欢玩的小游戏很有意思便自己动手试了试,真正的验证了这句话-不要以为你以为的就是你以为的,看视频时觉得看懂了,会写了, ...

- 原生js写的贪吃蛇网页版游戏特效

<meta http-equiv="Content-Type" content="text/html; charset=utf-8"> <bo ...

- 分享:计算机图形学期末作业!!利用WebGL的第三方库three.js写一个简单的网页版“我的世界小游戏”

这几天一直在忙着期末考试,所以一直没有更新我的博客,今天刚把我的期末作业完成了,心情澎湃,所以晚上不管怎么样,我也要写一篇博客纪念一下我上课都没有听,还是通过强大的度娘完成了我的作业的经历.(当然作业 ...

- 网页版电子表格控件tmlxSpreadsheet免费下载地址

tmlxSpreadsheet 是一个由JavaScript 和 PHP 写成的电子表格控件(包含WP插件, Joomla插件等等).. 程序员可以容易的添加一个类似Excel功能的,可编辑的表格功能 ...

- 基于HTML5的捕鱼达人游戏网页版

之前给大家分享了html5实现的水果忍者,愤怒的小鸟,中国象棋游戏.今天给大家分享一款捕鱼达人(fishjoy)网页版游戏的源码.可以在线玩也可以下载到本地.它使用html5技术和javascript ...

随机推荐

- ajax无刷新上传和下载

关于ajax无刷新上传和下载 这是一个没什么含量但是又用的比较多又不得不说的问题,其实真的不想说,因为没什么好说的. 关于上传 1.使用Flash,ActiveX 上传 ,略... 2.自己写XMLH ...

- 数学--数论--HDU 5382 GCD?LCM?(详细推导,不懂打我)

Describtion First we define: (1) lcm(a,b), the least common multiple of two integers a and b, is the ...

- 一个简单的wed服务器SHTTPD(6)———— SHTTPD错误处理的实现

//start from the very beginning,and to create greatness //@author: Chuangwei Lin //@E-mail:979951191 ...

- 【学习笔记:Python-网络编程】Socket 之初见

Socket 是任何一种计算机网络通讯中最基础的内容.当你在浏览器地址栏中输入一个地址时,你会打开一个套接字,可以说任何网络通讯都是通过 Socket 来完成的. Socket 的 python 官方 ...

- 《Docker从入门到跑路》之简介

什么是Docker Docker,中文翻译是"码头工人".根据官方的定义,Docker是以Docker容器为资源分割和调度的基本单元,封装了整个软件运行的环境,为开发者和系统管理员 ...

- dp D. Caesar's Legions

https://codeforces.com/problemset/problem/118/D 这个题目有点思路,转移方程写错了. 这个题目看到数据范围之后发现很好dp, dp[i][j][k1][k ...

- numpy数组的分割与合并

合并 np.newaxis import numpy as np a=np.array([1,2,3])[:,np.newaxis]#变成列向量 b=np.array([4,5,6])[:,np.ne ...

- 【Kafka】消息队列相关知识

目录 概述 常用消息队列 常用消息队列对比 应用场景 消息队列的两种模式 概述 消息(Message) 是指在应用系统之间传递的数据.消息可以非常简单,比如只包含文本字符串,也可以更复杂,可能包含嵌入 ...

- go实现SnowFlake

package main import ( "errors" "fmt" "strconv" "sync" " ...

- Git使用教程之SSH连接方式配置(二)

什么是GitHub?这个网站就是提供Git仓库托管服务的. 什么是SSH Key?你的本地Git仓库和GitHub仓库之间的传输是通过SSH加密的,大白话理解就是这两个仓库如果要进行远程同步,则我们需 ...