静态时序分析(static timing analysis) --- 时序路径

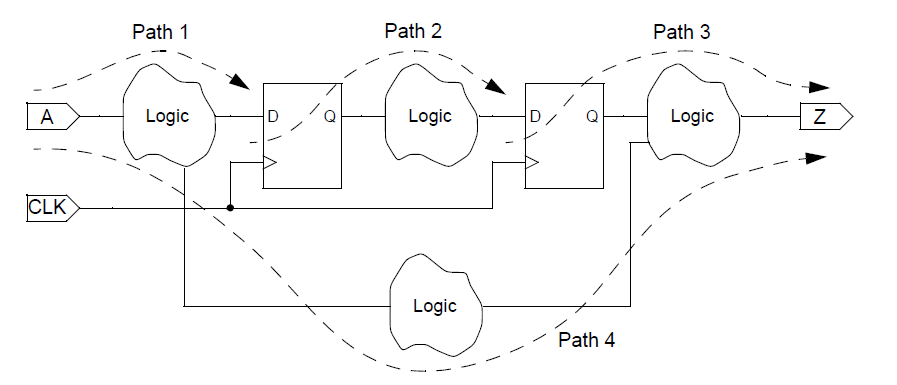

时序分析工具会找到且分析设计中的所有路径。每一个路径有一个起点(startpoint)和一个终点(endpoint)。起点是设计中数据被时钟沿载入的那个时间点,而终点则是数据通过了组合逻辑被另一个时间沿载入的时间点。

路径中的起点是一个时序元件的时钟pin或者设计的input port。input port可以作为起点是因为数据可以由外部源(external source)进入设计。

终点则是时序元件的数据输入pin或者设计的output port。同理output port可以作为终点是因为数据可以被外部源捕捉到。

上图显示一个时序路径的例子。

path1 开始于一个input port 且结束于时序元件的数据输入端

path2 开始于时序元件的时钟pin且结束于时序元件的数据输入端

path3 开始于时序元件的时钟pin且结束在一个output port

path4 开始于input port 且结束于 output port

每一个path都有专属的slack,slack值可以是正,0或者负。某一个path拥有最坏的slack的话则称之为 critical path

critical path拥有最大的负slack值。若是所有的path都没有时序违规,则slack都是正数,此时最小的那个slack则是critical path。

复数critical paths意味着某一组的path都是critical path。

路径可以被分组(group)来得到各自的时序分析,时序报告和优化。

在IC compliler中输入report_timimg可以得到时序报告,如下所示。

Startpoint: I_RISC_CORE/I_INSTRN_LAT/Instrn_1_reg_27_

(rising edge-triggered flip-flop clocked by SYS_2x_CLK)

Endpoint: I_RISC_CORE/I_ALU/Zro_Flag_reg

(rising edge-triggered flip-flop clocked by SYS_2x_CLK)

Path Group: SYS_2x_CLK

Path Type: max

Point Incr Path

----------------------------------------------------------------------------------

clock SYS_2x_CLK (rise edge) 0.00 0.00

clock network delay (propagated) 0.51 0.51

I_RISC_CORE/I_INSTRN_LAT/Instrn_1_reg_27_/CP (senrq1) 0.00 0.51 r

I_RISC_CORE/I_INSTRN_LAT/Instrn_1_reg_27_/Q (senrq1) 0.62 1.13 f

I_RISC_CORE/I_INSTRN_LAT/Instrn_1[] (INSTRN_LAT) 0.00 1.13 f

I_RISC_CORE/I_ALU/ALU_OP[] (ALU) 0.00 1.13 f

I_RISC_CORE/I_ALU/U288/ZN (nr03d0) 0.36 * 1.49 r

I_RISC_CORE/I_ALU/U261/ZN (nd03d0) 0.94 * 2.43 f

I_RISC_CORE/I_ALU/U307/ZN (invbd2) 0.35 * 2.78 r

I_RISC_CORE/I_ALU/U343/Z (an02d1) 0.16 * 2.93 r

I_RISC_CORE/I_ALU/U344/ZN (nr02d0) 0.11 * 3.04 f

I_RISC_CORE/I_ALU/U348/ZN (nd03d0) 0.28 * 3.32 r

I_RISC_CORE/I_ALU/U355/ZN (nr03d0) 0.29 * 3.60 f

I_RISC_CORE/I_ALU/U38/Z (an02d1) 0.15 * 3.75 f

I_RISC_CORE/I_ALU/U40/Z (an02d1) 0.12 * 3.87 f

I_RISC_CORE/I_ALU/U48/ZN (nd02d1) 0.06 * 3.93 r

I_RISC_CORE/I_ALU/U27/ZN (nd02d1) 0.06 * 3.99 f

I_RISC_CORE/I_ALU/Zro_Flag_reg/D (secrq4) 0.00 * 3.99 f

data arrival time 3.99 clock SYS_2x_CLK (rise edge) 4.00 4.00

clock network delay (propagated) 0.47 4.47

clock uncertainty -0.10 4.37

I_RISC_CORE/I_ALU/Zro_Flag_reg/CP (secrq4) 0.00 4.37 r

library setup time -0.37 4.00

data required time 4.00

--------------------------------------------------------------------------------

data required time 4.00

data arrival time -3.99

-------------------------------------------------------------------------------

slack (MET) 0.01

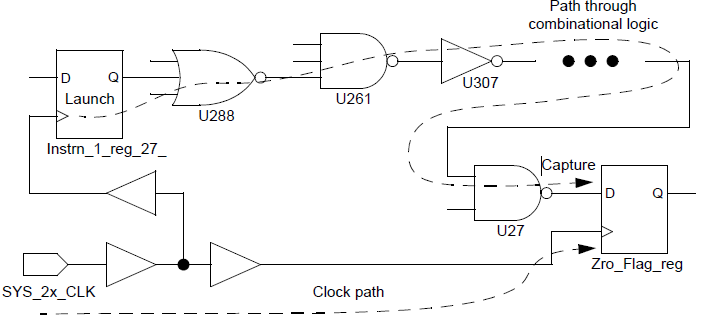

此例子的图如下:

报告开始显示了路径的起点,路径终点,路径组名和路径检测的类型。此例中,路径检测类型为max,意味着最大的延时或者setup check,若是min则是最小的延时或者hold check

下面一个大表显示了从起点到终点之间的一个个点的延时值。纵列有三个标识, Point, Incr和 Path,分别表示了路径中的各个点,此点所需要的延时和从起点一直累积到此点的延时值。

星号(*)表示了使用了SDF文件中的延时值,r和f表示 上升或者下降沿。

之前说过路径由数据载入的时钟沿开始,到device的数据输入端结束。表中的data arrival time表示了从载入时钟沿到终点数据到达所经历的时间。

再用required time减去arrival time 则得到了slack值。

例子中显示的slack非常小,意味着时序约束很勉强的达到要求。若是负数则需要改变设计来修复此violation,例如使用更大的drive strenth的driver来减少net delay。

反过来说,若是slack值相当大,则说明了此路径还有很多优化的机会。例如换成更小更慢的driver来减少面积,或者更高阈值的driver来减少leakage power。

静态时序分析(static timing analysis) --- 时序路径的更多相关文章

- 静态时序分析(static timing analysis)

静态时序分析(static timing analysis,STA)会检测所有可能的路径来查找设计中是否存在时序违规(timing violation).但STA只会去分析合适的时序,而不去管逻辑操作 ...

- static timing analysis 基础

此博文依据 特权同学在电子发烧友上的讲座PPT进行整理而成. static timing analysis 静态时序分析基础 过约束:有不必要的约束,或者是约束不能再某一情况下满足.——约束过头了 ...

- FPGA STA(静态时序分析)

1 FPGA设计过程中所遇到的路径有输入到触发器,触发器到触发器,触发器到输出,例如以下图所看到的: 这些路径与输入延时输出延时,建立和保持时序有关. 2. 应用背景 静态时序分析简称STA,它是一种 ...

- FPGA静态时序分析基础

FPGA静态时序分析基础 基本概念 Skew: 时钟偏移 Skew表示时钟到达不同触发器的延时差别,Tskew = 时钟到达2号触发器的时刻 - 时钟到达1号触发器的时刻. Jitter: 时钟抖动 ...

- Django基础,Day7 - 添加静态文件 static files

添加css样式文件 1.首先在app目录下创建static文件夹,如polls/static.django会自动找到放在这里的静态文件. AppDirectoriesFinder which look ...

- TimeQuest 静态时序分析 基本概论

静态时序分析 基本概念 [转载] 1. 背景 静态时序分析的前提就是设计者先提出要求,然后时序分析工具才会根据特定的时序模型进行分析,给出正确是时序报告. 进行静态时序分析,主要目的就是为了提高 ...

- 创建静态库Static Library(Framework库原理相似)

在项目开发的过程中,经常使用静态库文件.例如两个公司之间业务交流,不可能把源代码都发送给另一个公司,这时候将私密内容打包成静态库,别人只能调用接口,而不能知道其中实现的细节. 简介: 库是一些没有ma ...

- iOS 元件组件-创建静态库static library

概述 在项目开发的过程中,经常使用静态库文件.例如两个公司之间业务交流,不可能把源代码都发送给另一个公司,这时候将私密内容打包成静态库,别人只能调用接口,而不能知道其中实现的细节. 库是一些没有mai ...

- 静态时序分析基础STA

静态时序分析SAT 1. 背景 静态时序分析的前提就是设计者先提出要求,然后时序分析工具才会根据特定的时序模型进行分析,给出正确是时序报告. 进行静态时序分析,主要目的就是为了提高系统工作主频 ...

随机推荐

- Quartz 2d绘图

今天看了一下Quartz 2D绘图,我只想说:不要把绘图和动画那些东西当做一个很复杂的东西,其实只要你认真看还是可以理解的.他们并不难.啰嗦了几句,现在直接进入正题: 前提是我们必须新建一个singl ...

- iOS 利用长按手势移动 Table View Cells

本文译自:Cookbook: Moving Table View Cells with a Long Press Gesture 目录: 你需要什么? 如何做? 如何将其利用至UICollection ...

- iOS:自己写的一个星级评价的小Demo

重新整理了下自己星级评价的Demo,可以展示星级评价,可以动态修改星级. github的地址:https://github.com/hunterCold/HYBStarEvaluationView a ...

- 斯坦福iOS7公开课11笔记及演示Demo&访问HTTPS链接下载数据

这一节主要介绍UITableView以及iPad,Demo为从Flicker下载图片并显示,但是实际过程中发现需要FQ并使用HTTPS连接,所以这次用了两个Demo,一个是课程中的Demo,另一个是简 ...

- 朝花夕拾-android 获取当前手机的内存卡状态和网络连接状态

序言: 人的一生是一个选择的过程. 如果脚下只有一条路,只要一往无前即可,不用担心走错.即使是错也别无它法.然而人是不安分的,况且安于独木桥的行走,其目的地由于没有蜿蜒曲折去遮挡行路人的视线,一往无前 ...

- UVa 109 - SCUD Busters(凸包计算)

题目来源:https://uva.onlinejudge.org/index.php?option=com_onlinejudge&Itemid=8&category=3&pa ...

- URL、表单数据、IP等处理类

<?php class ev { public $cookie; public $post; public $get; public $file; public $url; public $G; ...

- TFS配置过程中的错误

有些人在配置TFS的过程中会报出[以前的更新或安装需要重新启动操作系统.……]的错误,但会发现无论重启多次操作系统,再配置的时候依然会报这个错误,很是让人苦恼哦. 这个错误在安装SharePoint的 ...

- 史上最全的MSSQL复习笔记 (转连接)

http://www.cnblogs.com/gameworld/p/4790881.html

- DataGridView单元格内容自动匹配下拉显示

页面显示数据使用的控件是ComponentFactory.Krypton.Toolkit中的KryptonDataGridView控件.在指定“商品”单元格中需要根据用户输入内容自动匹配数据库中商品信 ...