静态时序分析(static timing analysis) --- 时序路径

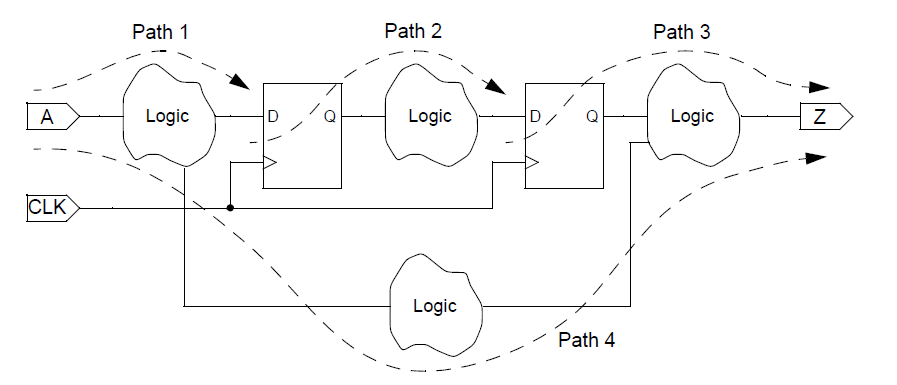

时序分析工具会找到且分析设计中的所有路径。每一个路径有一个起点(startpoint)和一个终点(endpoint)。起点是设计中数据被时钟沿载入的那个时间点,而终点则是数据通过了组合逻辑被另一个时间沿载入的时间点。

路径中的起点是一个时序元件的时钟pin或者设计的input port。input port可以作为起点是因为数据可以由外部源(external source)进入设计。

终点则是时序元件的数据输入pin或者设计的output port。同理output port可以作为终点是因为数据可以被外部源捕捉到。

上图显示一个时序路径的例子。

path1 开始于一个input port 且结束于时序元件的数据输入端

path2 开始于时序元件的时钟pin且结束于时序元件的数据输入端

path3 开始于时序元件的时钟pin且结束在一个output port

path4 开始于input port 且结束于 output port

每一个path都有专属的slack,slack值可以是正,0或者负。某一个path拥有最坏的slack的话则称之为 critical path

critical path拥有最大的负slack值。若是所有的path都没有时序违规,则slack都是正数,此时最小的那个slack则是critical path。

复数critical paths意味着某一组的path都是critical path。

路径可以被分组(group)来得到各自的时序分析,时序报告和优化。

在IC compliler中输入report_timimg可以得到时序报告,如下所示。

Startpoint: I_RISC_CORE/I_INSTRN_LAT/Instrn_1_reg_27_

(rising edge-triggered flip-flop clocked by SYS_2x_CLK)

Endpoint: I_RISC_CORE/I_ALU/Zro_Flag_reg

(rising edge-triggered flip-flop clocked by SYS_2x_CLK)

Path Group: SYS_2x_CLK

Path Type: max

Point Incr Path

----------------------------------------------------------------------------------

clock SYS_2x_CLK (rise edge) 0.00 0.00

clock network delay (propagated) 0.51 0.51

I_RISC_CORE/I_INSTRN_LAT/Instrn_1_reg_27_/CP (senrq1) 0.00 0.51 r

I_RISC_CORE/I_INSTRN_LAT/Instrn_1_reg_27_/Q (senrq1) 0.62 1.13 f

I_RISC_CORE/I_INSTRN_LAT/Instrn_1[] (INSTRN_LAT) 0.00 1.13 f

I_RISC_CORE/I_ALU/ALU_OP[] (ALU) 0.00 1.13 f

I_RISC_CORE/I_ALU/U288/ZN (nr03d0) 0.36 * 1.49 r

I_RISC_CORE/I_ALU/U261/ZN (nd03d0) 0.94 * 2.43 f

I_RISC_CORE/I_ALU/U307/ZN (invbd2) 0.35 * 2.78 r

I_RISC_CORE/I_ALU/U343/Z (an02d1) 0.16 * 2.93 r

I_RISC_CORE/I_ALU/U344/ZN (nr02d0) 0.11 * 3.04 f

I_RISC_CORE/I_ALU/U348/ZN (nd03d0) 0.28 * 3.32 r

I_RISC_CORE/I_ALU/U355/ZN (nr03d0) 0.29 * 3.60 f

I_RISC_CORE/I_ALU/U38/Z (an02d1) 0.15 * 3.75 f

I_RISC_CORE/I_ALU/U40/Z (an02d1) 0.12 * 3.87 f

I_RISC_CORE/I_ALU/U48/ZN (nd02d1) 0.06 * 3.93 r

I_RISC_CORE/I_ALU/U27/ZN (nd02d1) 0.06 * 3.99 f

I_RISC_CORE/I_ALU/Zro_Flag_reg/D (secrq4) 0.00 * 3.99 f

data arrival time 3.99 clock SYS_2x_CLK (rise edge) 4.00 4.00

clock network delay (propagated) 0.47 4.47

clock uncertainty -0.10 4.37

I_RISC_CORE/I_ALU/Zro_Flag_reg/CP (secrq4) 0.00 4.37 r

library setup time -0.37 4.00

data required time 4.00

--------------------------------------------------------------------------------

data required time 4.00

data arrival time -3.99

-------------------------------------------------------------------------------

slack (MET) 0.01

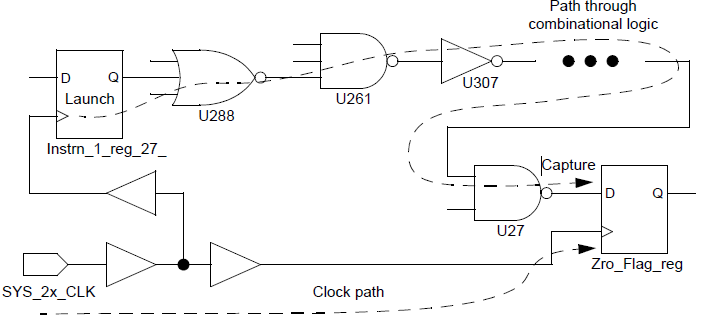

此例子的图如下:

报告开始显示了路径的起点,路径终点,路径组名和路径检测的类型。此例中,路径检测类型为max,意味着最大的延时或者setup check,若是min则是最小的延时或者hold check

下面一个大表显示了从起点到终点之间的一个个点的延时值。纵列有三个标识, Point, Incr和 Path,分别表示了路径中的各个点,此点所需要的延时和从起点一直累积到此点的延时值。

星号(*)表示了使用了SDF文件中的延时值,r和f表示 上升或者下降沿。

之前说过路径由数据载入的时钟沿开始,到device的数据输入端结束。表中的data arrival time表示了从载入时钟沿到终点数据到达所经历的时间。

再用required time减去arrival time 则得到了slack值。

例子中显示的slack非常小,意味着时序约束很勉强的达到要求。若是负数则需要改变设计来修复此violation,例如使用更大的drive strenth的driver来减少net delay。

反过来说,若是slack值相当大,则说明了此路径还有很多优化的机会。例如换成更小更慢的driver来减少面积,或者更高阈值的driver来减少leakage power。

静态时序分析(static timing analysis) --- 时序路径的更多相关文章

- 静态时序分析(static timing analysis)

静态时序分析(static timing analysis,STA)会检测所有可能的路径来查找设计中是否存在时序违规(timing violation).但STA只会去分析合适的时序,而不去管逻辑操作 ...

- static timing analysis 基础

此博文依据 特权同学在电子发烧友上的讲座PPT进行整理而成. static timing analysis 静态时序分析基础 过约束:有不必要的约束,或者是约束不能再某一情况下满足.——约束过头了 ...

- FPGA STA(静态时序分析)

1 FPGA设计过程中所遇到的路径有输入到触发器,触发器到触发器,触发器到输出,例如以下图所看到的: 这些路径与输入延时输出延时,建立和保持时序有关. 2. 应用背景 静态时序分析简称STA,它是一种 ...

- FPGA静态时序分析基础

FPGA静态时序分析基础 基本概念 Skew: 时钟偏移 Skew表示时钟到达不同触发器的延时差别,Tskew = 时钟到达2号触发器的时刻 - 时钟到达1号触发器的时刻. Jitter: 时钟抖动 ...

- Django基础,Day7 - 添加静态文件 static files

添加css样式文件 1.首先在app目录下创建static文件夹,如polls/static.django会自动找到放在这里的静态文件. AppDirectoriesFinder which look ...

- TimeQuest 静态时序分析 基本概论

静态时序分析 基本概念 [转载] 1. 背景 静态时序分析的前提就是设计者先提出要求,然后时序分析工具才会根据特定的时序模型进行分析,给出正确是时序报告. 进行静态时序分析,主要目的就是为了提高 ...

- 创建静态库Static Library(Framework库原理相似)

在项目开发的过程中,经常使用静态库文件.例如两个公司之间业务交流,不可能把源代码都发送给另一个公司,这时候将私密内容打包成静态库,别人只能调用接口,而不能知道其中实现的细节. 简介: 库是一些没有ma ...

- iOS 元件组件-创建静态库static library

概述 在项目开发的过程中,经常使用静态库文件.例如两个公司之间业务交流,不可能把源代码都发送给另一个公司,这时候将私密内容打包成静态库,别人只能调用接口,而不能知道其中实现的细节. 库是一些没有mai ...

- 静态时序分析基础STA

静态时序分析SAT 1. 背景 静态时序分析的前提就是设计者先提出要求,然后时序分析工具才会根据特定的时序模型进行分析,给出正确是时序报告. 进行静态时序分析,主要目的就是为了提高系统工作主频 ...

随机推荐

- javamail 发送邮件demo

package com.suntray.test; import javax.mail.BodyPart; import javax.mail.Message; import javax.mail.M ...

- 基础学习day03---程序结构与控制、函数与数组入门

一.程序结构 1.顺序结构 2.选择结构 3.循环结构 二.顺序结构 程序至上而下逐行执行,一条语句执行完之后继续执行下一条语句,一直到程序的末尾 三.条件选择结构 选择结构是根据条件的成立与否, ...

- db2操作 连接、备份、恢复db2

先deactivate后再start standby再primary报错不能启动hadr standby的时候,先restore,但是别rollback,直接start hadr as standby ...

- JavaScript Patterns 4.5 Immediate Functions

The immediate function pattern is a syntax that enables you to execute a function as soon as it is d ...

- cocos2d-x之value

bool HelloWorld::init() { if ( !Layer::init() ) { return false; } Size visibleSize = Director::getIn ...

- 在IT的路上,我在成长

在IT的路上,我在成长.很荣幸地加入了博客园这个大家庭. 岁月的航船在不断航行,在成长的脚印我要深深留下,回首已往经历,发现自己成长的路上,将来也会有很多美好的回忆,以及丰硕的果实.

- Spring @Transactional ——事务回滚

工作原理运行配置@Transactional注解的测试类的时候,具体会发生如下步骤1)事务开始时,通过AOP机制,生成一个代理connection对象,并将其放入DataSource实例的某个与Dat ...

- openssl c_rehash

一.简介 c_rehash 为文件创建一个符号连接,并将此符号连接的名称设为文件的hash值,作用是让openssl在证书目录中能够找到证书. 二.语法 c_rehash [-old] [-h] [- ...

- POJ 2299 Ultra-QuickSort(线段树入门)

Ultra-QuickSort Time Limit: 7000MS Memory Limit: 65536K Description In this problem, you have to ana ...

- Swift 学习笔记 enum 枚举类型

异端,异端啊,我感觉这是map吧? enum ATMStatus { case Success(Int) case Error(String) } func withdraw(amount: Int) ...