怎样使用Debussy+ModelSim快速查看前仿真波形

引子:ModelSim是HDL仿真软件,Debussy是波形查看软件;搭配使用,相当爽。此处所谓快速查看前仿真波形仅为抛砖引玉,大家不要拘泥于此。两款软件的功能都很强大,请自行研究。

注:本篇博文的软件环境为:Debussy 5.3v9 + Modelsim SE 6.5

配置篇

1 安装、和谐软件。略。

2 拷贝文件..\Novas\Debussy\share\PLI\modelsim_pli\WINNT\novas.dll至文件夹..\modeltech_6.5\win32。

3 取消文件..\modeltech_6.5\modelsim.ini的只读属性后,打开。

找到

|

1

|

; Veriuser = veriuser.sl |

替换为

|

1

|

Veriuser = novas.dll |

保存;关闭;设为只读。

配置完,以后就一劳永逸了。

实战篇

此处以一简单分频器为例。文件地图如下:

|

1

2

3

4

5

6

7

8

|

│ rtl.f│ run.bat│ sim.do│ └─rtl clk_rst.v divider.v divider_tb.v |

1 编写欲仿真的HDL文件:RTL级代码+Testbench代码。保存在文件夹rtl中。

(1)divider.v // RTL级代码模块

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

|

`timescale 1ns/10psmodule divider( input i_clk, input i_rst_n, output o_clk); parameter U_DLY = 1;// log2(5) = 2.3219 <= 3 reg [2:0] cnt_p; // 上升沿计数子 // 5位上升沿计数器: 0 ~ 4// 4 = 5 - 1always @ (posedge i_clk, negedge i_rst_n)begin if (!i_rst_n) cnt_p <= 0; else begin if (cnt_p == 4) cnt_p <= 0; else cnt_p <= #U_DLY cnt_p + 1'b1; endend// log2(5) = 2.3219 <= 3 reg [2:0] cnt_n; // 下降沿计数子// 5位下降沿计数器: 0 ~ 4// 4 = 5 - 1always @ (negedge i_clk, negedge i_rst_n)begin if (!i_rst_n) cnt_n <= 0; else begin if (cnt_n == 4) cnt_n <= 0; else cnt_n <= #U_DLY cnt_n + 1'b1; endend reg o_clk_p; // 上升沿时钟输出寄存器// 输出上升沿时钟// 0 ~ 2 ↑-> 1// (2+1) ~ 4 ↑-> 0// 2 = 5>>1// 4 = 5 - 1always @ (posedge i_clk, negedge i_rst_n)begin if (!i_rst_n) o_clk_p <= 0; else begin if (cnt_p <= 2) // 2 = 5>>1 o_clk_p <= 1; else o_clk_p <= 0; endend reg o_clk_n; // 下降沿时钟输出寄存器// 输出下降沿时钟// 0 ~ 2 ↓-> 1// (2+1) ~ 4 ↓-> 0// 2 = 5>>1// 4 = 5 - 1always @ (negedge i_clk, negedge i_rst_n)begin if (!i_rst_n) o_clk_n <= 0; else begin if (cnt_n <= 2) // 2 = 5>>1 o_clk_n <= 1; else o_clk_n <= 0; endendassign o_clk = o_clk_n & o_clk_p; // 按位与(作用:掩码) endmodule |

(2)clk_rst.v // Testbench的时钟及复位模块

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

|

`timescale 1ns/10psmodule clk_rst( output reg i_clk, output reg i_rst_n);parameter CLK_PERIOD = 20;parameter MULT_RATIO = 10;parameter RESET_TIME = MULT_RATIO * CLK_PERIOD + 1;initialbegin i_rst_n <= 1'b0; #RESET_TIME i_rst_n <= 1'b1;endinitialbegin i_clk <= 1'b0; forever #(CLK_PERIOD / 2) i_clk <= ~i_clk;endendmodule |

把时钟及复位单独剥出来,便于移植到其他平台。

(3)divider_tb.v // Testbench顶层例化模块

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

|

`timescale 1ns/10psmodule divider_tb();wire i_clk;wire i_rst_n;wire o_clk;// genrate clockclk_rst clk_rst_inst( .i_clk(i_clk), .i_rst_n(i_rst_n));// user logicdivider divider_inst( .i_clk(i_clk), .i_rst_n(i_rst_n), .o_clk(o_clk));// dump fsdb file for debussyinitialbegin $fsdbDumpfile("wave.fsdb"); $fsdbDumpvars;endendmodule |

注意第22行到第27行

|

1

2

3

4

5

6

|

// dump fsdb file for debussyinitialbegin $fsdbDumpfile("wave.fsdb"); $fsdbDumpvars;end |

这段语句的意思,就是调用ModelSim生成波形文件,并保存为wave.fsdb,供Debussy查看。

2 编写HDL文件列表文件,供ModelSim和Debussy使用。

rtl.f

|

1

2

3

|

rtl/divider.vrtl/clk_rst.vrtl/divider_tb.v |

3 编写ModelSim命令行脚本文件。

sim.do

|

1

2

3

4

5

|

vlib workvlog -f rtl.fvsim work.divider_tbrun 10usq |

4 编写批处理脚步文件,调用命令行ModelSim生成波形文件,再调用Debusyy查看。

run.bat

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

|

::关闭回显@ECHO OFF::设置软件路径SET debussy=C:\Novas\Debussy\bin\Debussy.exeSET vsim=C:\modeltech_6.5\win32\vsim.exe::ModelSim Command%vsim% -c -do sim.do::删除ModelSim生成的相关文件RD work /s /qDEL transcript vsim.wlf /q::Debussy Command%debussy% -f rtl.f -ssf wave.fsdb -2001::删除波形文件DEL wave.fsdb /q::删除Debussy生成的相关文件RD Debussy.exeLog /s /qDEL debussy.rc /q::退出命令行EXIT |

注意:请适当修改相关路径,本处仅以我个人的配置为例。

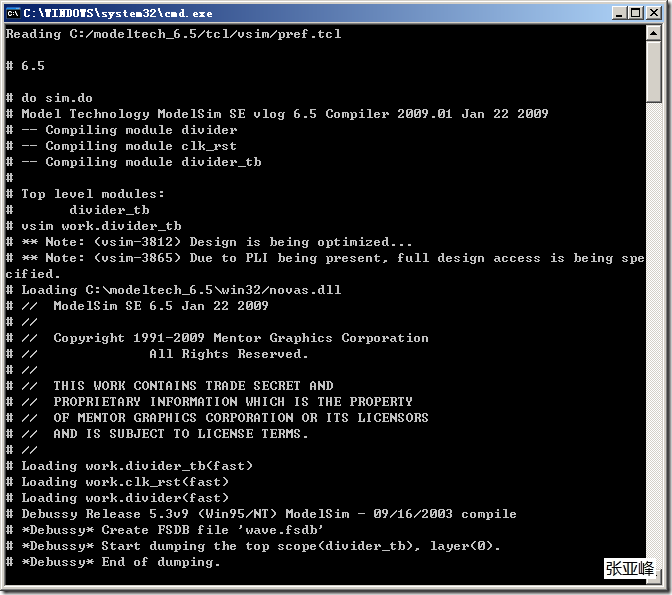

5 双击运行run.bat

显示命令行画面

图1 运行run.bat画面

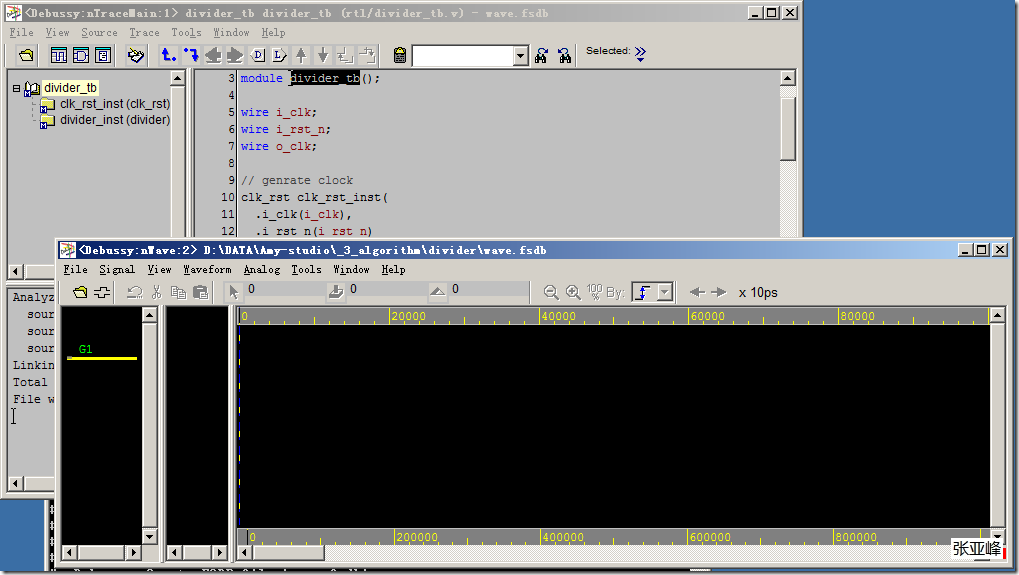

弹出Debussy及Debussy波形查看组件。

图2 Debussy及Debussy波形查看组件

我CALL,波形在哪里。小样竟敢唬我。

呵呵,别着急,慢慢来。

(6)添加欲观察信号。

单击 或Signal-Get Signals…添加信号;或者偷懒一点,单击Signal-Get All Signals。此处我就一懒到底,就添加全部信号吧。

或Signal-Get Signals…添加信号;或者偷懒一点,单击Signal-Get All Signals。此处我就一懒到底,就添加全部信号吧。

弹出警告,告知我们添加所有信号需要花费一段时间,是否要确认。确认OK。

图3 警告

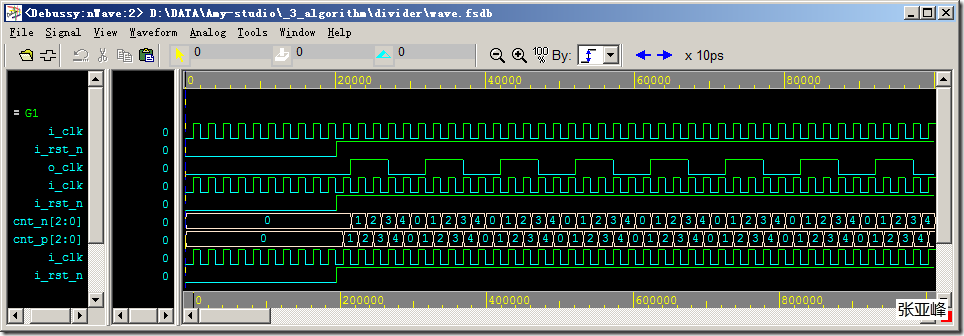

看,波形出来了。

图4 devider前仿真波形

结语

正如引子所言,ModelSim的功能太强大了,于是就有点繁琐。和Debussy协同仿真,我们就省却了许多不必要,何乐而不为呢。当然,还有许多的功能,由于水平有限,就写到这里吧。

参考

1 袁秋春.用modelsim和debussy协同仿真VHDL Verilog的流程

2 cmf3887299.debussy+modelsim的仿真流程

转载自:http://www.cnblogs.com/yuphone/archive/2010/05/31/1747871.html

怎样使用Debussy+ModelSim快速查看前仿真波形的更多相关文章

- 使用Debussy+ModelSim快速查看前仿真波形

sim.do文件 quit -sim set PATH1 D:/Program/modelsim/vivado_lib set PATH2 D:/Program/Vivado/Vivado/2014. ...

- EBS R12.2快速安装前没有配置Global Inventory报错

EBS R12.2快速安装前没有配置Global Inventory,导致验证时"file systems"这一项没有通过,被标记了"X": (本图其它两个验证 ...

- FPGA前仿真后仿真

前仿真 后仿真 时序(综合后)仿真 时序仿真将时延考虑进去,包括综合后产生的(与.或.非)门时延,还有布局布线产生的时延. 综合(Synthesize),就是将HDL语言设计输入翻译成由与.或.非门和 ...

- sp_help 快速查看表结构、视图信息

sp_helptext: 是MS SQL Server的一个系统存储过程,可以通过它来查看存储过程或者视图.函数源码 示例:sp_helptext viewName (viewName 即要查询的存 ...

- MSSql使用SQL语句快速查看表对的就说明,及表字段描述及字段类型

--表描述 SELECT tbs.name 表名,ds.value 描述 FROM sys.extended_properties ds LEFT JOIN sysobjects tbs ON ds. ...

- 推荐一款非常棒的谷歌插件---快速查看HTML页面元素的CSS样式

一.下载地址 http://chromecj.com/web-development/2015-05/456/download.html 二.简介 CssViewer是一款快速查看当前页面元素的CSS ...

- 快速查看SQL Server 中各表的数据量以及占用空间大小

快速查看SQL Server 中各表的数据量以及占用空间大小. CREATE TABLE #T (NAME nvarchar(100),ROWS char(20),reserved varchar(1 ...

- QuartusII 中使用Modelsim对子程序进行仿真

QuartusII 中使用Modelsim对子程序进行仿真 如果采用RTL级仿真那么就没有任何问题,但是如果对子程序采用门级仿真就会出错 解决办法:在Project Navigator中右键需要进行门 ...

- Mac小技巧:快速查看指定应用程序的所有窗口

我们知道在Mac中快速在系统所有程序中切换得快捷键为: cmd + tab 不过有时我们需要快速查看某一个程序的所有窗口,那又该如何呢? 以下方法在MacOS 10.12中测试成功! Mac默认该功能 ...

随机推荐

- devfs、sysfs、udev介绍

转:http://www.360doc.com/content/11/1203/09/7378000_169310928.shtml 一.devfs linux下有专门的文件系统用来对设备进行管理,d ...

- Sysfs文件系统与Linux设备模型

转:http://www.360doc.com/content/11/1218/16/1299815_173168170.shtml sysfs把连接在系统上的设备和总线组织成为一个分级的目录及文件, ...

- 微服务:spring-cloud-archaius 起步

原文:http://blog.csdn.net/qq_18675693/article/details/53337941 微服务:spring-cloud-archaius 起步 原创 2016年11 ...

- google的开源项目总结

转自http://www.feng5166.com/blog/424.html google的开源项目值得我们一用的,这些项目很有意义,甚至可以直接用在我们自己的工作上!学习编程的的一个比较好的方式就 ...

- sql语句 -- 倒序 升序

- Cookie个数压缩存存储实践

提到cookie,大家都不会陌生的,几乎涉及到交互或统计的WEB系统都会使用到cookie,关于cookie的基础知识网上也有很多,这里推荐两篇文章: 聂微东的: http://www.cnblogs ...

- Koch 分形,海岸线,雪花

此算法用于生成Koch分形(海岸线,雪花).速度高速,效果绚丽 //支持的初始直线水平角度为60 的倍数. 交换起点与终点坐标可改变生成方向 void Koch(CDC *pDC, int x1, i ...

- php+wamp环境部署本地Web应用

1.创建新的项目(project),创建完成之后单击工具栏的应用运行/调试(Select Run/Debug Configuration)的下拉菜单弹出 Edit Cofigurations选项,单击 ...

- DBA数据库信息查询常用SQL

常用DBA脚本1.查看表空间的名称及大小 select t.tablespace_name, round(sum(bytes/(1024*1024)),0) ts_size from dba_tabl ...

- django admin后台接入tinymce并且支持图片上传

首先:下载tinymce 地址是https://www.tinymce.com/ 点击download 下载社区版本即可 接着:把压缩包内tinymce目录内的所有文件和文件夹复制到Django项目中 ...