FPGA驱动LCD显示红绿蓝彩条

实验目的:先简单熟悉LCD灯的驱动和时序图的代码实现。设计功能是让LCD显示红绿蓝三种颜色,即三个彩带。本次实验比较容易实现,主要是对LCD驱动时序图的理解和时序参数的配置。

实验条件:1.LCD原理图2020-12-17-HXH_ESP32_E1。

2.所用开发板用户手册:GW1NSR-LV4CQN48PC7I6_V1.1开发板用户手册

3.LCD的数据手册:SC7283(确定LCD驱动设计的引脚和时序控制)

注释:第一项和第二项结合是为了,分配LCD和FPGA的引脚。一般用PDF软件Adobe Acrobat DC进行查找引脚编号,再粘贴复制找到引脚的位置,在用一个EXCEL表格记下引脚名字,引脚的位置或编号,引脚的电压类型(LVCMOS33或LVCMOS18等)

实验原理:

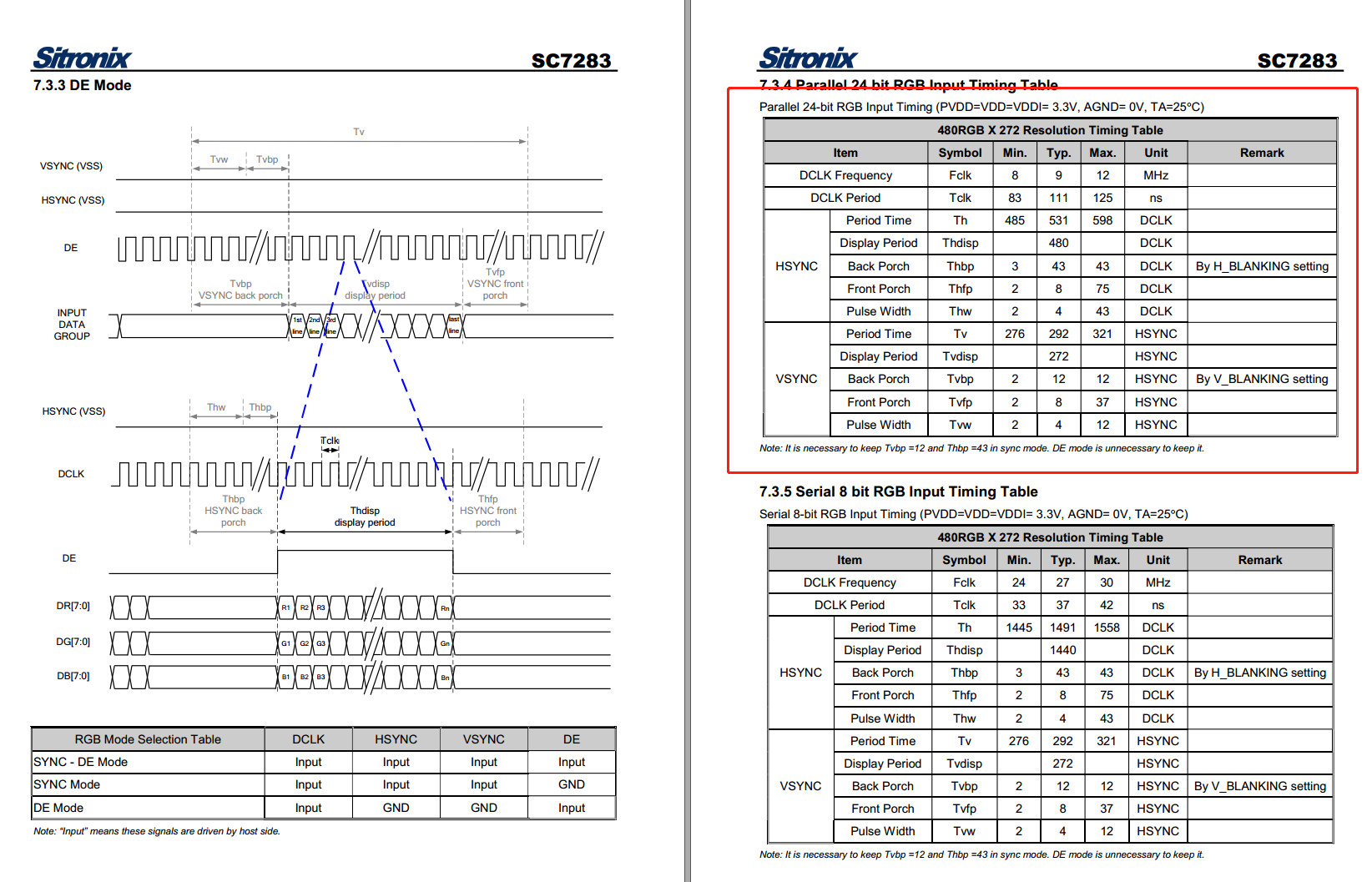

LCD的分辨率为480RGB * 272 ,理解为有480列和272行,分别对应行同步计数器h_cnt 和场同步计数器v_cnt ,LCD有三种模式,SYNC, SYNC-DE and DE mode,本次选用的是第二种,和VGA的驱动很相似,先是行同步信号HSYNC,然后是场同步信号VSYNC(行同步信号(一个像素点)可以理解为把一行的所有列扫描完则就是场同步信号,即场同步信号比行同步信号大。)再是有效区域DE。由于对于行同步信号或者场同步信号的时许控制来讲,都是由行同步信号或场同步信号周期,前沿,有效区域,后沿等四个部分参数组成

时许图如下:

下图红框的是LCD分辨率为480RGB * 272时,对应时序图中的配置参数。

三 代码设计:

本设计代码分成两部分,一是顶层模块,二是LCD驱动控制模块。

1.LCD顶层模块:

|

module lcd_top# //////// RGB /////////////////// ////////////// 延时复位 /////////// wire FPGA_RST_N; LCD_CTRL # ,.lcd_A_vs(fv) ,.lcd_A_clk(pixclk) endmodule |

2.LCD驱动模块

|

module LCD_CTRL # ,parameter H_FRONT_PORCH = 8 ,parameter H_ACTIVE = 480 ,output lcd_A_vs always @ (posedge clk_9m or negedge rst_n) begin //------------------------VSYNC的时间计数 begin always @ (posedge clk_9m or negedge rst_n) begin //------------------------生成VSYNC信号 begin //------------------------生成HSYNC信号 begin //------------------------生成DE信号 begin //------------------------把控制信号和FIFO读取的数据进行同步 begin always @ (posedge clk_9m or negedge rst_n) begin //------------------------将同步后的RGB数据按照协议进行映射输出 begin always @ (posedge clk_9m or negedge rst_n) begin //显示彩条红绿蓝 assign lcd_A_rgb = lcd_rgb1_d;//16'hf0;// assign lcd_A_vs = vsync_r; endmodule |

四实验中的问题:

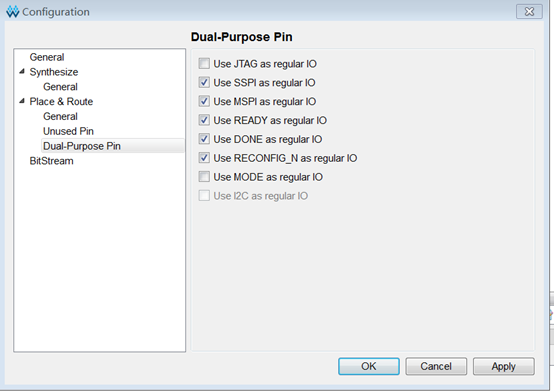

注意1:今天出现了FPGA设计软件布局布线时提示引脚错误,说这几个引脚已经有专用引脚了。其实,是同一个引脚复用,即LCD_PIXCLK,PIXDATA[16], PIXDATA[23],DE,LV引脚提示和MSPI引脚冲突,最后通过钩选引脚复用解决,如下所示:

注意2:实验现象即开发板只亮了一半,开发板分辨率:480*272,马上想到是行或列的参数错误。

parameter ROW_NUM = 480

,parameter COL_NUM = 272(H_ACTIVE),即列对应行同步信号。列应该是480=COL_NUM ,行是对应着场同步信号,即行是272=ROW_NUM

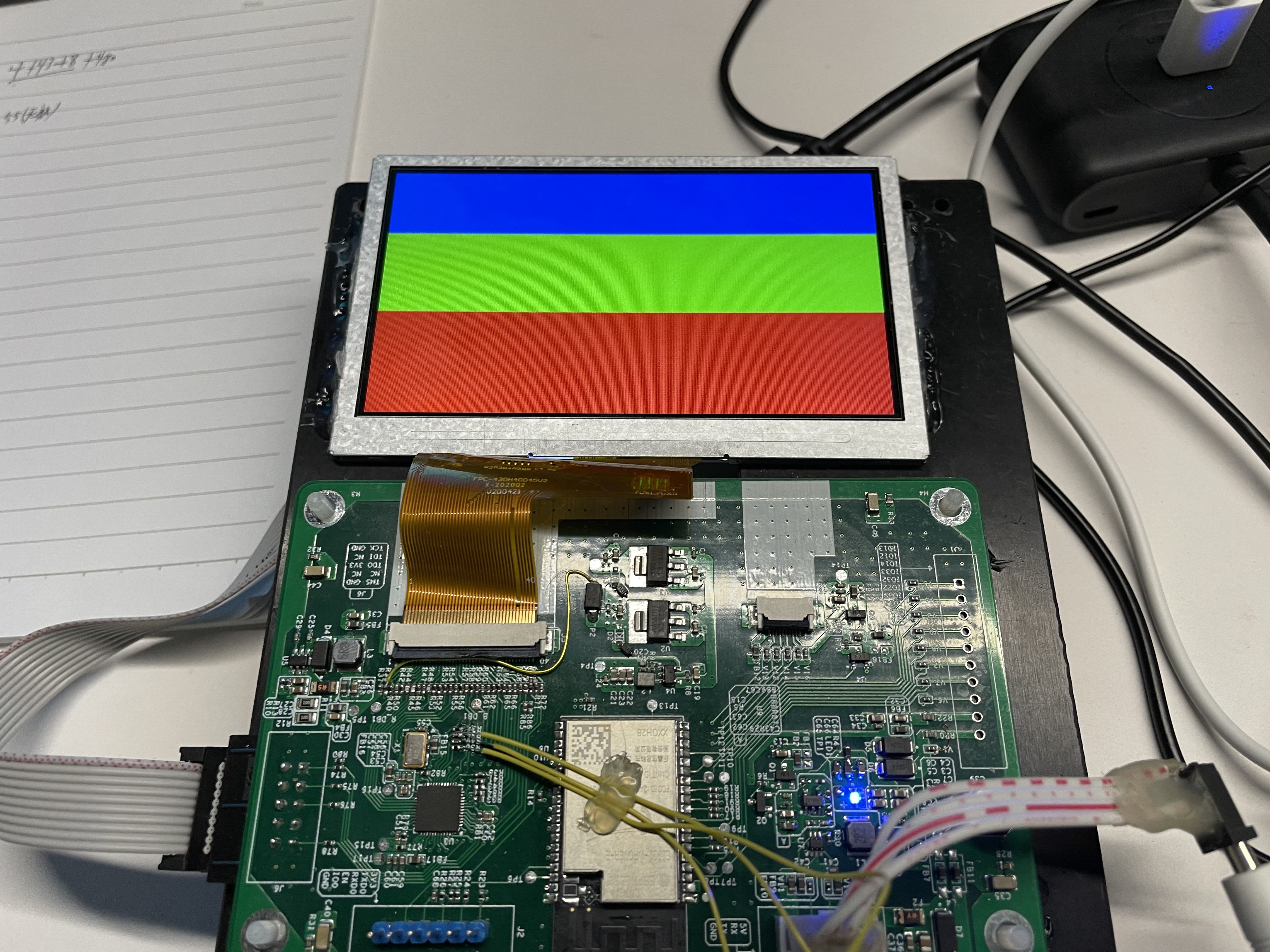

五下板实验效果

FPGA驱动LCD显示红绿蓝彩条的更多相关文章

- 阶段小项目1:循环间隔1秒lcd显示红绿蓝

#include<stdlib.h>#include<stdio.h>#include<string.h>#include<error.h>#inclu ...

- FPGA驱动VGA显示静态图片

一 .前言 本文设计思想采用明德扬至简设计法.VGA是最常见的视频显示接口,时序也较为简单.本文从利用显示屏通过VGA方式显示测试图案及静态图片着手带大家接触图像显示应用,算是为后续VGA显示摄像头采 ...

- 基于FPGA驱动VGA显示图片的小问题

学习VGA显示图片的过程中,遇到了一个小问题,我在显示屏上开了一个60x60的框,放了一张图片进去显示,但是最终的结果如下图所示. 出现了一个竖黑边,看了看代码,分析了一下逻辑没问题,然而看这个显示那 ...

- Hierarchical clustering:利用层次聚类算法来把100张图片自动分成红绿蓝三种色调—Jaosn niu

#!/usr/bin/python # coding:utf-8 from PIL import Image, ImageDraw from HierarchicalClustering import ...

- [LeetCode] Similar RGB Color 相似的红绿蓝颜色

In the following, every capital letter represents some hexadecimal digit from 0 to f. The red-green- ...

- [LeetCode] 800. Similar RGB Color 相似的红绿蓝颜色

In the following, every capital letter represents some hexadecimal digit from 0 to f. The red-green- ...

- 痞子衡嵌入式:记录i.MXRT1060驱动LCD屏显示横向渐变色有亮点问题解决全过程(提问篇)

大家好,我是痞子衡,是正经搞技术的痞子.今天痞子衡给大家分享的是i.MXRT1060上LCD横向渐变色显示出亮点问题的分析解决经验. 痞子衡前段时间在支持一个i.MXRT1060客户项目时遇到了LCD ...

- MSP430常见问题之LCD 显示驱动类

Q1:晶体一般都是接32768,然后使用液晶很正常.我打算将晶体接6M的替换32768,那么液晶还能正常显示吗A1:看你所用的LCM 模块时序极限是多少HZ,然后看6M情况下,MSP430去驱动LCM ...

- linux驱动开发:用户空间操作LCD显示简单的图片【转】

转自:http://blog.csdn.net/changliang7731/article/details/53074616 上一章我们简单介绍了LCD的一些基本原理.当然更深奥的还有,比如gamm ...

随机推荐

- 37、python并发编程之协程

目录: 一 引子 二 协程介绍 三 Greenlet 四 Gevent介绍 五 Gevent之同步与异步 六 Gevent之应用举例一 七 Gevent之应用举例二 一 引子 本节的主题是基于单线程来 ...

- 前端提交数据到node的N种方式

写在前面 本篇介绍了前端提交数据给node的几种处理方式,从最基本的get和post请求,到图片上传,再到分块上传,由浅入深. GET请求 经典的get提交数据,参数通过URL传递给node,node ...

- 关于oracle中(+)的运用

一.基础 1.1 SQL查询的基本原理 第一.单表查询:根据WHERE条件过滤表中的记录,形成中间表(这个中间表对用户是不可见的):然后根据SELECT的选择列选择相应的列进行返回最终结果.第二.两表 ...

- ensp上防火墙的实现

使用ensp模拟器中的防火墙(USG6000V)配置NAT(网页版)一.NAT介绍NAT(Network Address Translation,网络地址转换):简单来说就是将内部私有地址转换成公网地 ...

- [转自Matrix67] 趣题:顶点数为多少的图有可能和自己互补

若干个顶点以及某些顶点和顶点之间的连线,就构成了一个"图".如果对某个图进行变换,使得原来任意两个有连线的顶点之间都不再有连线,原来任意两个没有连线的顶点之间现在都有连线了,那么所 ...

- 你别告诉我你还在用Excel做数据透视分析吧,太low了!

来到大数据分析的时代,大量的大数据分析软件涌现,尽管如此,如果今天有人问起最常用的数据透视分析工具是什么的时候,我猜想Excel应该是大家的不二之选. 但是其实我想说,用现在的手机来打比方,Excel ...

- Windows原理深入学习系列-访问控制列表

这是[信安成长计划]的第 19 篇文章 0x00 目录 0x01 介绍 0x02 DACL 0x03 创建DACL 0x04 文件读取测试 0x05 进程注入测试 0x06 原理分析 Win10_x6 ...

- Chrome:开发者模式下复制Element下的代码

Element模块下的代码只能一行一行复制,想要复制一个代码块,可以把该代码块先收起来,再对这个收起来的代码块进行复制就OK了

- Python post中session和auth 的三种方法

1.方式一,获取session后.存储起来.下次调用时候,传递一个session植即可 #/bin/python # -*- coding: utf-8 -*- import requests fro ...

- gdb调试快速入门

编译指令 gcc test.c -o test -g -g是加入调试信息,加入源码信息 启动gdb调试 gdb test 进入gdb中 设置参数 set args 10 20 显示参数show age ...