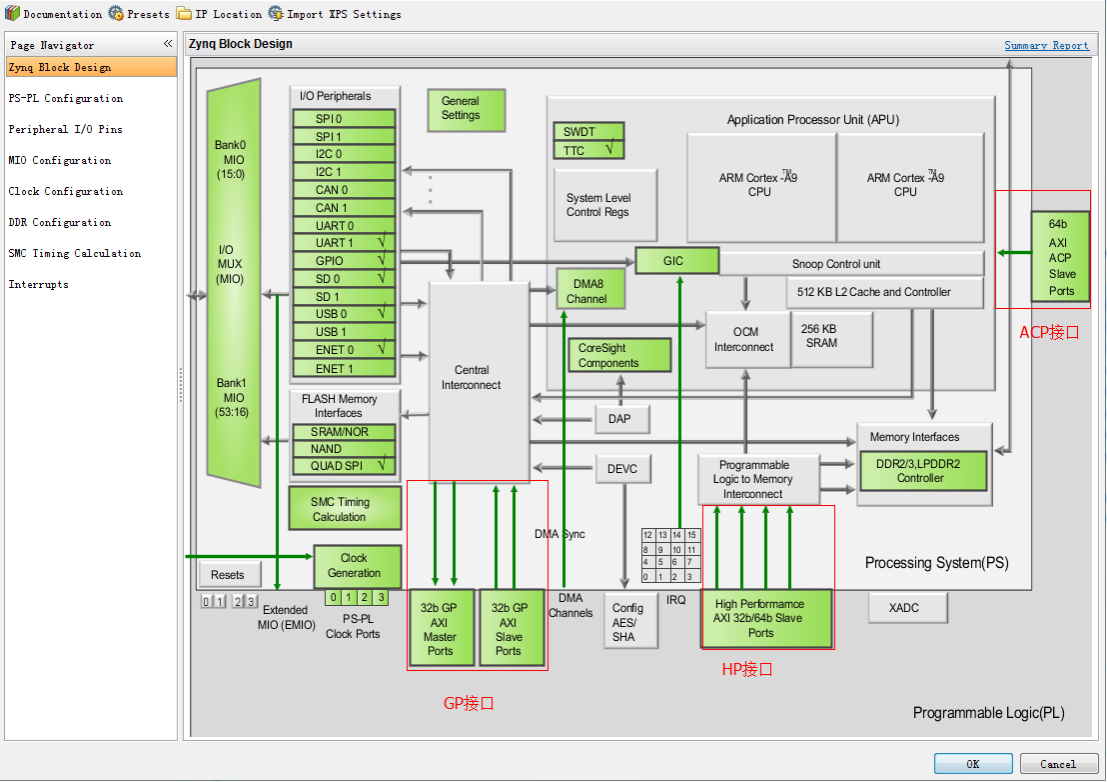

【转】AXI_Lite 总线详解

input wire s00_axi_aclk,

input wire s00_axi_aresetn,

input wire [C_S00_AXI_ADDR_WIDTH- : ] s00_axi_awaddr,

input wire [ : ] s00_axi_awprot,

input wire s00_axi_awvalid,

output wire s00_axi_awready,

input wire [C_S00_AXI_DATA_WIDTH- : ] s00_axi_wdata,

input wire [(C_S00_AXI_DATA_WIDTH/)- : ] s00_axi_wstrb,

input wire s00_axi_wvalid,

output wire s00_axi_wready,

output wire [ : ] s00_axi_bresp,

output wire s00_axi_bvalid,

input wire s00_axi_bready,

input wire [C_S00_AXI_ADDR_WIDTH- : ] s00_axi_araddr,

input wire [ : ] s00_axi_arprot,

input wire s00_axi_arvalid,

output wire s00_axi_arready,

output wire [C_S00_AXI_DATA_WIDTH- : ] s00_axi_rdata,

output wire [ : ] s00_axi_rresp,

output wire s00_axi_rvalid,

input wire s00_axi_rready

没错笔者曾在《AXI总线概述》这节中提到了他们,这次通过源码分析再次隆重介绍它们。

always @( posedge S_AXI_ACLK )

begin

if ( S_AXI_ARESETN == 'b0 )

begin

slv_reg0 <= ;

slv_reg1 <= ;

slv_reg2 <= ;

slv_reg3 <= ;

end

else begin

if (slv_reg_wren)

begin

case ( axi_awaddr[ADDR_LSB+OPT_MEM_ADDR_BITS:ADDR_LSB] )

'h0:

for ( byte_index = ; byte_index <= (C_S_AXI_DATA_WIDTH/)-; byte_index = byte_index+ )

if ( S_AXI_WSTRB[byte_index] == ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 0

slv_reg0[(byte_index*) +: ] <= S_AXI_WDATA[(byte_index*) +: ];

end

'h1:

for ( byte_index = ; byte_index <= (C_S_AXI_DATA_WIDTH/)-; byte_index = byte_index+ )

if ( S_AXI_WSTRB[byte_index] == ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 1

slv_reg1[(byte_index*) +: ] <= S_AXI_WDATA[(byte_index*) +: ];

end

'h2:

for ( byte_index = ; byte_index <= (C_S_AXI_DATA_WIDTH/)-; byte_index = byte_index+ )

if ( S_AXI_WSTRB[byte_index] == ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 2

slv_reg2[(byte_index*) +: ] <= S_AXI_WDATA[(byte_index*) +: ];

end

'h3:

for ( byte_index = ; byte_index <= (C_S_AXI_DATA_WIDTH/)-; byte_index = byte_index+ )

if ( S_AXI_WSTRB[byte_index] == ) begin

// Respective byte enables are asserted as per write strobes

// Slave register 3

slv_reg3[(byte_index*) +: ] <= S_AXI_WDATA[(byte_index*) +: ];

end

default : begin

slv_reg0 <= slv_reg0;

slv_reg1 <= slv_reg1;

slv_reg2 <= slv_reg2;

slv_reg3 <= slv_reg3;

end

endcase

end

end

end

for ( byte_index = ; byte_index <= (C_S_AXI_DATA_WIDTH/)-; byte_index = byte_index+ )

if ( S_AXI_WSTRB[byte_index] == ) begin

slv_reg0[(byte_index*) +: ] <= S_AXI_WDATA[(byte_index*) +: ];

end

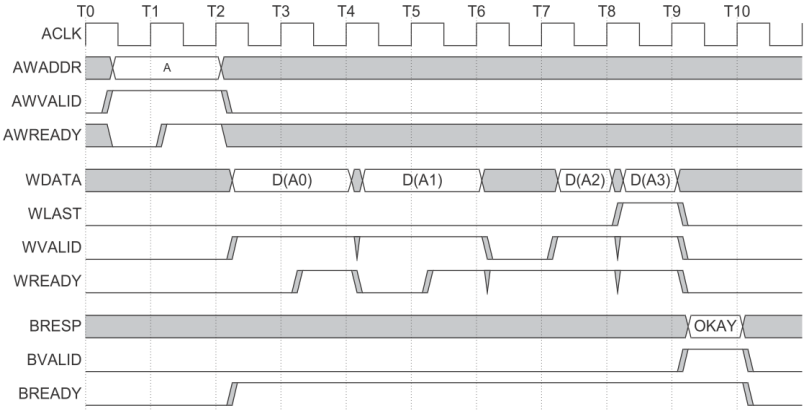

其中,C_S_AXI_DATA_WIDTH的宏定义的值为32,也就是数据位宽,S_AXI_WSTRB就是写选通信号,S_AXI_WDATA就是写数据信号。

存在于for循环中的最关键的一句:

slv_reg0[(byte_index*8) +: 8] <= S_AXI_WDATA[(byte_index*8) +: 8];

当byte_index = 0的时候这句话就等价于:

slv_reg0[7:0] <= S_AXI_WDATA[7:0];

当byte_index = 1的时候这句话就等价于:

slv_reg0[15:8] <= S_AXI_WDATA[15:8];

当byte_index = 2的时候这句话就等价于:

slv_reg0[23:16] <= S_AXI_WDATA[23:16];

当byte_index = 3的时候这句话就等价于:

slv_reg0[31:24] <= S_AXI_WDATA[31:24];

也就是说,只有当写选通信号为1时,它所对应S_AXI_WDATA的字节才会被读取。

读懂了这段话之后,我们就知道了,如果我们想得到PS写到总线上的数据,我们只需要读取slv_reg0的值即可。

那如果,我们想写数据到总线让PS读取该数据,我们该怎么做呢?我们继续来看有关RADTA读数据代码:

// Output register or memory read data

always @( posedge S_AXI_ACLK )

begin

if ( S_AXI_ARESETN == 'b0 )

begin

axi_rdata <= ;

end

else

begin

// When there is a valid read address (S_AXI_ARVALID) with

// acceptance of read address by the slave (axi_arready),

// output the read dada

if (slv_reg_rden)

begin

axi_rdata <= reg_data_out; // register read data

end

end

end

观察可知,当PS读取数据时,程序会把reg_data_out复制给axi_rdata(RADTA读数据)。我们继续追踪reg_data_out:

always @(*)

begin

// Address decoding for reading registers

case ( axi_araddr[ADDR_LSB+OPT_MEM_ADDR_BITS:ADDR_LSB] )

'h0 : reg_data_out <= slv_reg0;

'h1 : reg_data_out <= slv_reg1;

'h2 : reg_data_out <= slv_reg2;

'h3 : reg_data_out <= slv_reg3;

default : reg_data_out <= ;

endcase

end

和前面分析的一样此时通过判断axi_awaddr[3:2]的值来判断将那个值给reg_data_out上,同样当PS调用读取函数时,这里axi_awaddr[3:2]默认是0,所以我们只需要把slv_reg0替换成我们自己数据,就可以让PS通过总线读到我们提供的数据。

这里可能有的读者会问了,slv_reg0不是总线写过来的数据吗?因为笔者说过这个程序是Vivado为我们提供的例子,它这么做无非是想验证我写出去的值和我读进入的值相等。但是他怎么写确实会对初看代码的人造成困扰。

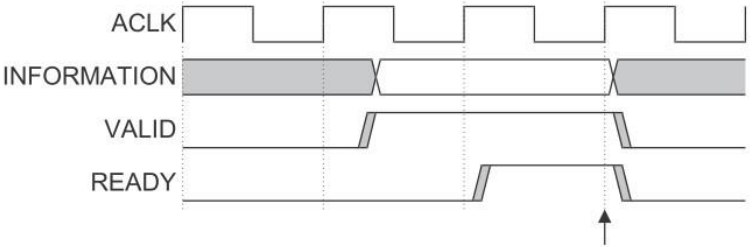

最后笔者提出一个问题,为什么写通道要比读通道多了一列应答通道,这是为什么呢?

首先,你要知道这个应答信号是干什么用的?

写应答,主要是回复主机你这个写过程是没有问题的,那读为什么不需要这个过程呢?

这时因为主机在读取数据时,从机可以直接通过读数据通道给主机反馈信息,因此就没有必要再来开辟一个单独的应答通道了。

小结:

如果我们想读AXI4_Lite总线上的数据时,只需关注slv_reg的数据,我们可自行添加一段代码,如:

reg [:]rlcd_rgb;

always @( posedge S_AXI_ACLK )

begin

if ( S_AXI_ARESETN == 'b0 )

begin

rlcd_rgb <= 'd0;

end

else

begin

rlcd_rgb <= slv_reg0[:];

end

end

assign lcd_rgb = rlcd_rgb;

如果我们想对AXI4_Lite信号写数据时,我们只需修改对reg_data_out的赋值,如:

//写总线测试修改!!!!!!!!!

wire[:]wlcd_xy;// = {10'd0,lcd_xy};

assign wlcd_xy = {'d0,lcd_xy};

assign slv_reg_rden = axi_arready & S_AXI_ARVALID & ~axi_rvalid;

always @(*)

begin

// Address decoding for reading registers

case ( axi_araddr[ADDR_LSB+OPT_MEM_ADDR_BITS:ADDR_LSB] )

'h0 : reg_data_out <= wlcd_xy;//slv_reg0;

'h1 : reg_data_out <= slv_reg1;

'h2 : reg_data_out <= slv_reg2;

'h3 : reg_data_out <= slv_reg3;

default : reg_data_out <= ;

endcase

end

最后强调下如果我们自定义的IP的地址被映射为0x43C00000,那么我们Xil_Out32(0x43C00000,Value)写的就是slv_reg0的值。如果地址偏移4位,如Xil_Out32(0x43C00000 + 4,Value) 写的就是slv_reg1的值,依次类推。

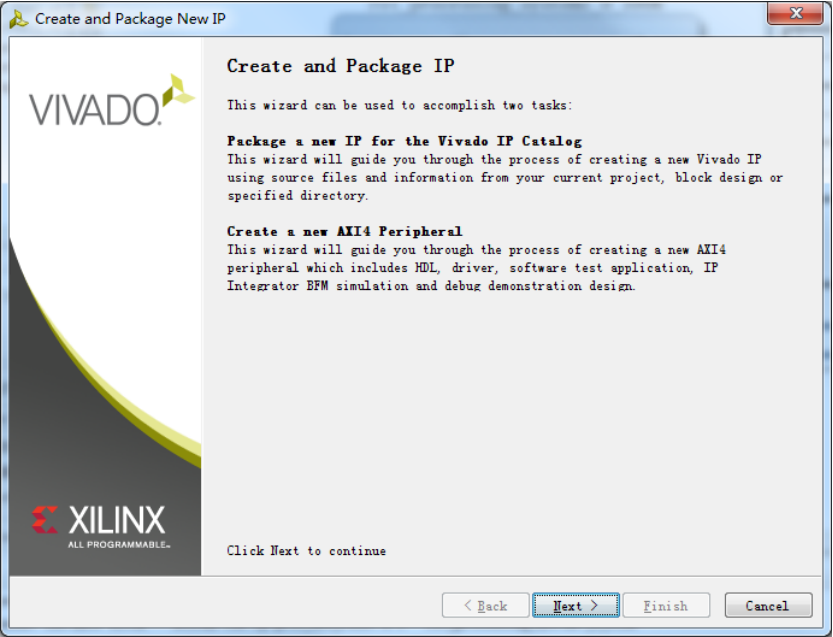

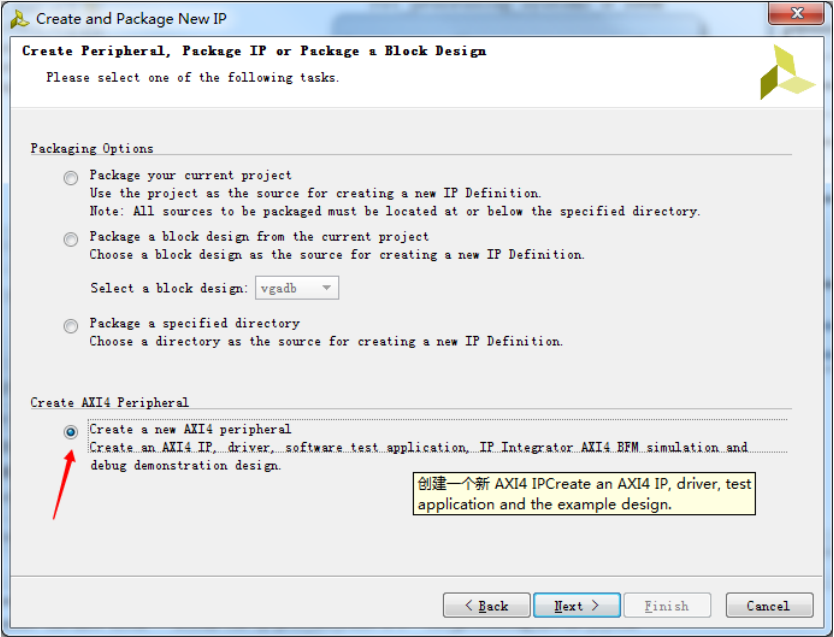

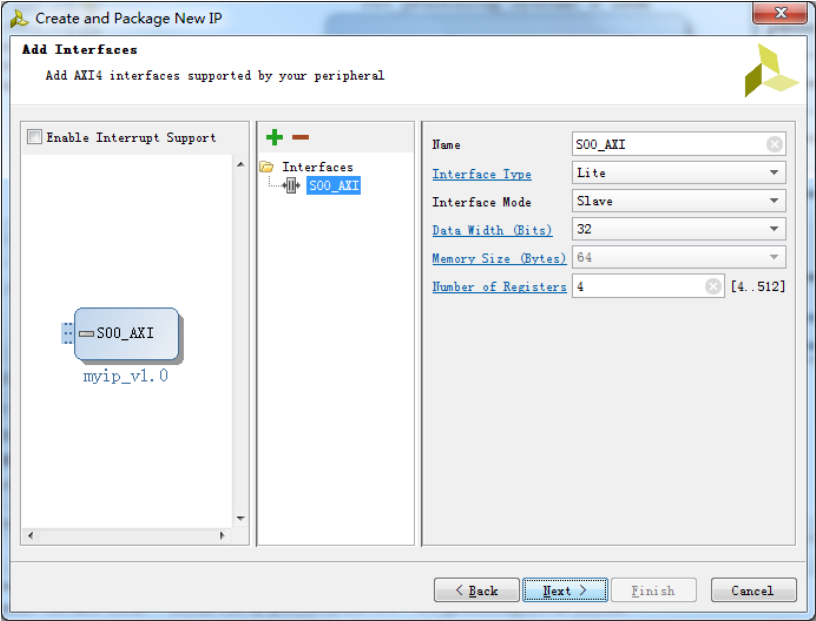

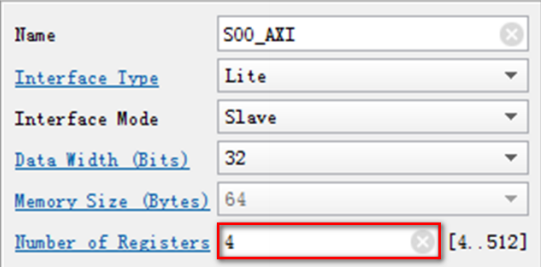

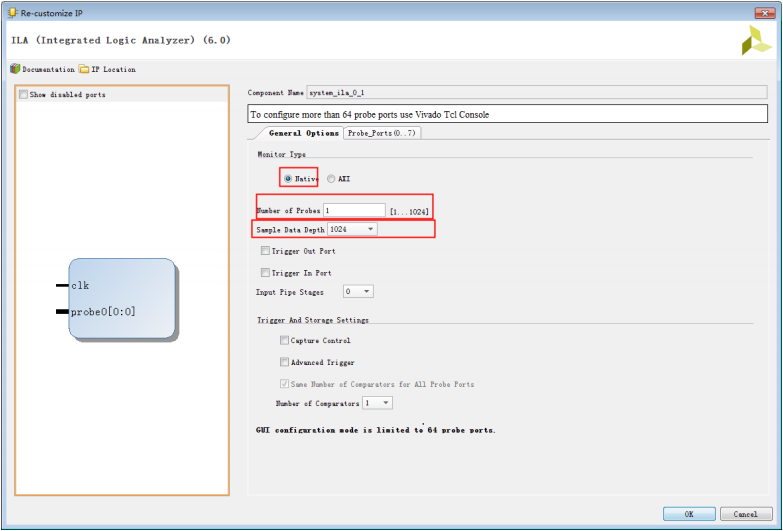

目前这里只有4个寄存器,那是因为之前选择的是4个,其实我们可以定义的更多:

#define XPAR_ MYIPFREQUENCY_ 0_ S00_ AXI_ BASEADDR 0x43C00000

#define XPAR_ MYIPFREQUENCY_ 0_ S00_ AXI_ HIGHADDR 0x43C0FFFF

理论上只要基地址 + 偏移量不要超过HIGHADDR即可。

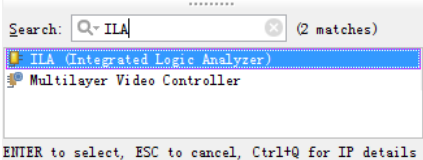

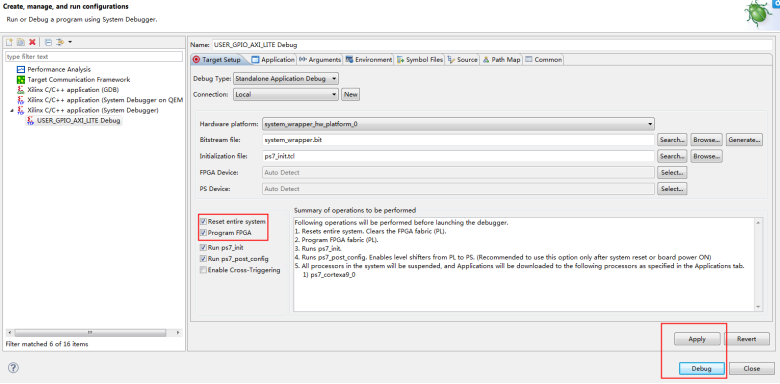

添加 ila CORE

添加 ila CORE

Step9:接下来依然是,右键单击Block文件,文件选择Generate the Output Products。

Step10:继续右键单击Block文件,选择Create a HDL wrapper,根据Block文件内容产生一个HDL 的顶层文件,并选择让vivado自动完成。

Setp11:单击Run Synthesis,如果有 Save 对话框弹出选择保存。

Setp12:综合结束后选择Synthesized Design option单击 OK。

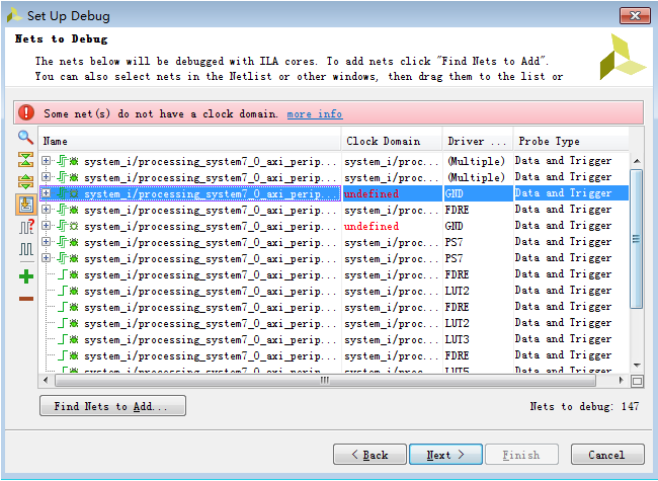

Step13:在如下对话框中找到Unassigned debug nets(如果对话框没有出现选择 菜单->Window > Debug)

Step14:右击 Unassigned Debug Nets 选择Set up Debug… 之后单击 Next

Step15:删除红色错误的信号然后单击Next 到结束

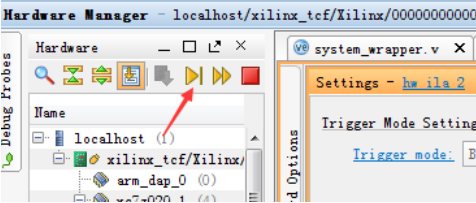

后 VIVADO HW_ILA2 窗口采集到波形输出,可以看到 AXI总线的工作时序。

后 VIVADO HW_ILA2 窗口采集到波形输出,可以看到 AXI总线的工作时序。

【转】AXI_Lite 总线详解的更多相关文章

- S02_CH12_ AXI_Lite 总线详解

S02_CH12_ AXI_Lite 总线详解 12.1前言 ZYNQ拥有ARM+FPGA这个神奇的架构,那么ARM和FPGA究竟是如何进行通信的呢?本章通过剖析AXI总线源码,来一探其中的秘密. 1 ...

- Linux设备驱动模型之platform(平台)总线详解

/********************************************************/ 内核版本:2.6.35.7 运行平台:三星s5pv210 /*********** ...

- [CAN].CAN总线详解

转自:https://blog.csdn.net/cheatscat/article/details/82886889 CAN(Controller Area Network)总线协议是由 BOSCH ...

- [LIN].LIN总线详解

转自:https://www.2cto.com/kf/201806/754227.html 参考:https://wenku.baidu.com/view/a9b08d786bd97f192379e9 ...

- [SDIO].SDIO总线详解

转自:https://blog.csdn.net/liuhan33025/article/details/51131848 SDIO接口是在SD内存卡接口的基础上发展起来的接口,SDIO接口兼容以前的 ...

- [I2C].I2C总线详解

转自:https://www.cnblogs.com/BitArt/archive/2013/05/27/3101037.html 一. 基本信息 1. 概述 I²C 是Inter-Integrate ...

- SPI总线协议及SPI时序图详解

SPI,是英语Serial Peripheral Interface的缩写,顾名思义就是串行外围设备接口.SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚 ...

- 迅为4412开发板Linux驱动教程——总线_设备_驱动注册流程详解

本文转自:http://www.topeetboard.com 视频下载地址: 驱动注册:http://pan.baidu.com/s/1i34HcDB 设备注册:http://pan.baidu.c ...

- SPI总线协议及SPI时序图详解【转】

转自:https://www.cnblogs.com/adylee/p/5399742.html SPI,是英语Serial Peripheral Interface的缩写,顾名思义就是串行外围设备接 ...

随机推荐

- flink batch wordcount

1.POJO方式 public class WordCountPojo { public static class Word{ private String word; private int fre ...

- 个人项目-WC (java实现)

一.Github地址:https://github.com/734635746/WC 二.PSP表格 PSP2.1 Personal Software Process Stages 预估耗时(分钟) ...

- 使用脚本安装elasticsearch7.3的记录

使用脚本安装elasticsearch7.3的记录 #!/bin/sh # https://www.elastic.co/guide/en/elasticsearch/reference/curren ...

- 面试官:讲讲redis的过期策略如何实现?

时隔多日,小菜鸡终于接到阿里的面试通知,屁颠屁颠的从上海赶到了杭州. 经过半个小时的厮杀: 自我介绍 hashMap和ConcurrentHashMap区别 jdk中锁的实现原理 volatile的使 ...

- Centos7 samba配置

目录 免密码只读 加密码可读写 Samba配置了很多次,总是忘,现在写在博客里. 免密码只读 最主要的是免密配置,主要用到了两个配置,要写在[global]里: map to guest = Bad ...

- oracle 导入导出表

imp username/pwd@orcl file=c:\temp\exp.dmp tables=(table1, table2)#imp username/pwd@ip:1521/orcl ful ...

- 2. 代理模式(C++)

1.介绍 代理模式:为其他对象提供一种代理以控制对这个对象的访问.这样实现了业务和核心功能分离. 在代理模式中,我们创建具有现有对象的对象,以便向外界提供功能接口.在某些情况下,一个对象不适合或者不能 ...

- react小项目

本章要讲述一个评价栏的制作. 首先先简单写一个ract组件来试试. index.html <!DOCTYPE html> <html> <head> <tit ...

- UiPath: Studio 快捷键

以下是 UiPath Studio 键盘快捷键的完整列表: 文件管理 Ctrl + Shift + N - 创建一个新的项目 Ctrl + O - 打开此前创建的工作流文件.仅仅支持扩展名为 .xam ...

- JLOI 2009 二叉树问题

洛谷 P3884 [JLOI2009]二叉树问题 洛谷传送门 JDOJ 2024: [JLOI2009]二叉树问题 JDOJ传送门 Description 如下图所示的一棵二叉树的深度.宽度及结点间距 ...