微机基础与x86架构

微型计算机的组成

微型计算机是电子计算机的一个分支,以微

处理器(cpu)为核心

微型计算机的整体组成由下图表示:

我们本节着重了解主机系统,即:CPU,存储器,输入输出接口,总线四部分。

- CPU是计算机的核心,包括三部分,运算器,控制器,寄存器组

- 存储器是计算机中的记忆装置 ,用于存放计算机工作过程中需要操作的,数据和程序。存储器有内存储器和外存储器之分。内存储器就是主机内部原有的存储,外存储器就是外接的存储。(U盘等),内存储器的存取速度较快, 容量相对较小。按照工作方式可分为RAM和ROM

- 接口是CPU与外部设备间的桥梁,实现信号电平或类型的转换,协调高速CPU和低速外设之间的信息交换

- 总线是一组导线和相关的控制、驱动电路的集合,是计算机系统各部件之间传输地址 、 数据和控制信息的通道。可以分为地址总线(AB),数据总线(DB),控制总线(CB)

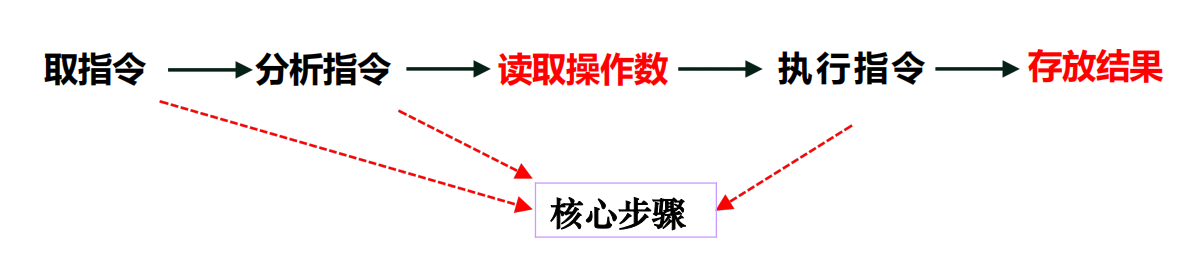

微机的一般工作过程

计算机的工作就是按照一定的顺序 ,一条条地执行指令。

。

。

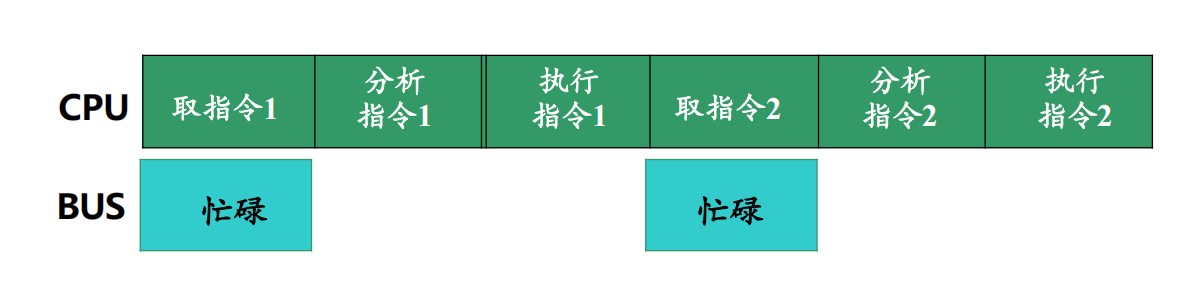

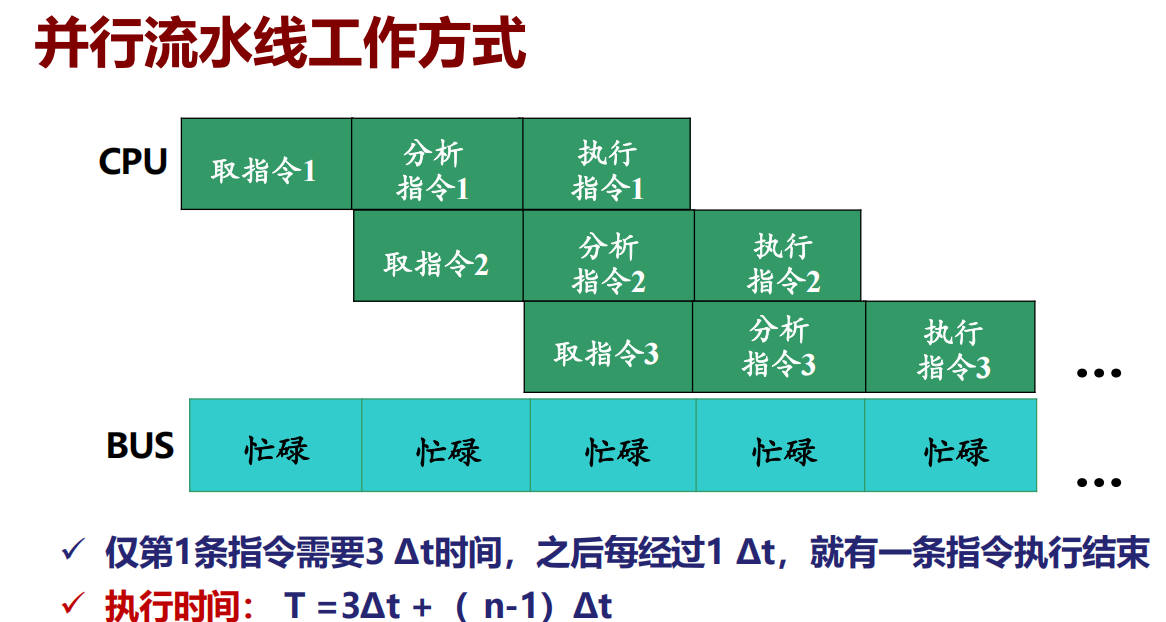

cpu的处理方式由串行向并行发展

数制与码制

十进制用D表示,二进制用B表示,16进制用H表示,在汇编语言程序中,十进制的标识符D可以缺省(默认为十进制数);但二进制、十六进制的标识符不能省略。

- 位(bit)只能填0或1

- 字节:(Byte) 1Byte=8bit 一字节=8位=十六进制:XXH xxxxxxxxB

- 字(word),其具体大小因设备而异,指的是cpu一次能处理的二进制数据长度 8086CPU字长16位(2Byte,XXXXH),现代x86cpu字长64位(8Byte) 二字节等=一字=16位=十六进制:XXXXH

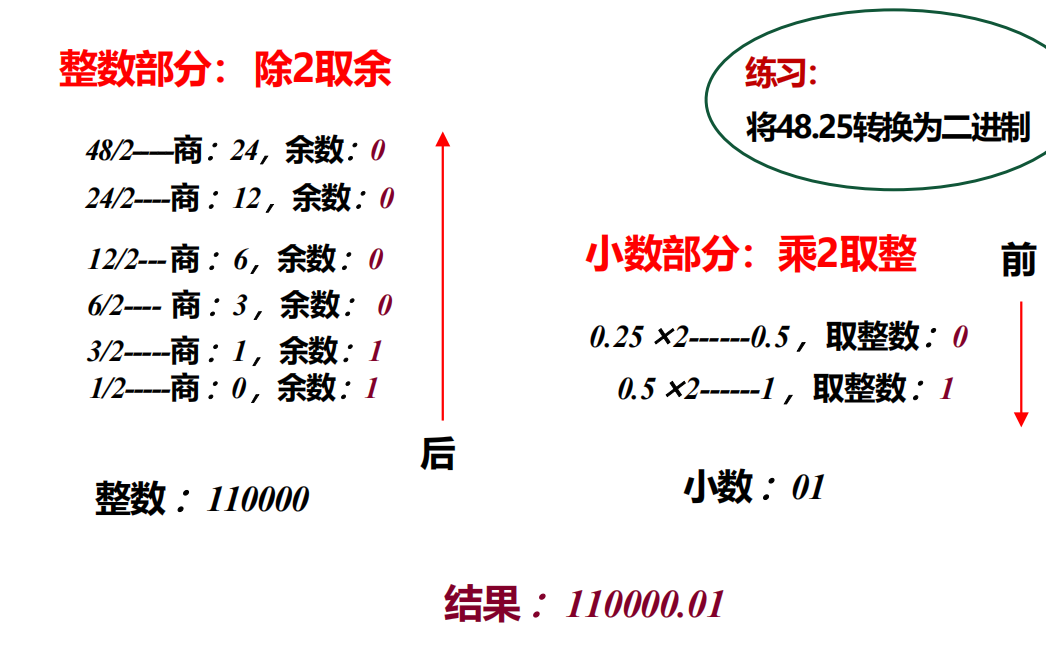

数制之间的转化

- 10to2:整数部分除以2,余数倒序排列;小数部分乘以2,整数部分取出,直到小数部分为0或达到精度要求

- 10to16:整数部分除以16,余数倒序排列;小数部分乘以16,整数部分取出,直到小数部分为0或达到精度要求

关于编码,计算机只能理解码而不能理解人类语言,对于数值的编码,使用BCD码(一般使用8421BCD码),二进制码等,对于英文字母的编码使用ASCII码。

BCD

用4位二进制码表示1位十进制数,每4位之间有一个空格

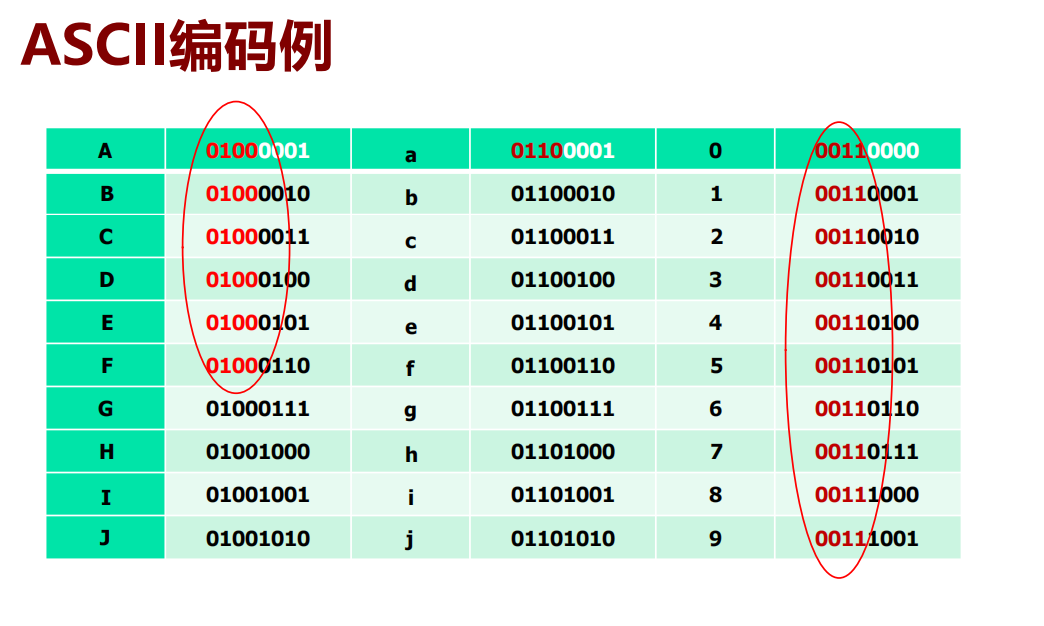

ASCII

将每个字母、数字、标点、控制符用1Byte二进制码(8位)表示,其中:标准ASCII的有效位:7bit,最高位默认为0。

ASCII 码是基于拉丁字母的一套电脑编码系统,用 7 位二进制数来表示 128 个不同的字符。在进行数据传输或存储时,为了增加数据的可靠性,会在这 7 位数据的基础上增加一位校验位,形成 8 位编码。奇偶校验就是通过检测这 8 位编码中 “1” 的个数的奇偶性来判断数据是否可能出现错误。

校验类型

- 奇校验:在奇校验中,要保证包括校验位在内的 8 位编码中 “1” 的个数为奇数。例如,对于 ASCII 码字符 “A”,其 7 位编码为 “1000001”,其中有 2 个 “1”,为了满足奇校验,校验位会被设置为 “1”,最终传输的 8 位编码就是 “11000001”。

- 偶校验:与奇校验相反,偶校验要求包括校验位在内的 8 位编码中 “1” 的个数为偶数。还是以字符 “A” 为例,其 7 位编码 “1000001” 有 2 个 “1”,按照偶校验规则,校验位应设置为 “0”,传输的 8 位编码就是 “01000001”。

例子:A的ASCII码是41H(1000001B),以奇校验传送则为 C1H(11000001B)

为了做题,记住常见的ASCII码:A是41H,a是61H,0是30H。

为了做题,记住常见的ASCII码:A是41H,a是61H,0是30H。

为了做题,记住常见的ASCII码:A是41H,a是61H,0是30H。

有符号数的表示

有符号数:用最高位表示符号,其余是数值,有符号数的表示方法:原码 反码 补码

原/反/补码

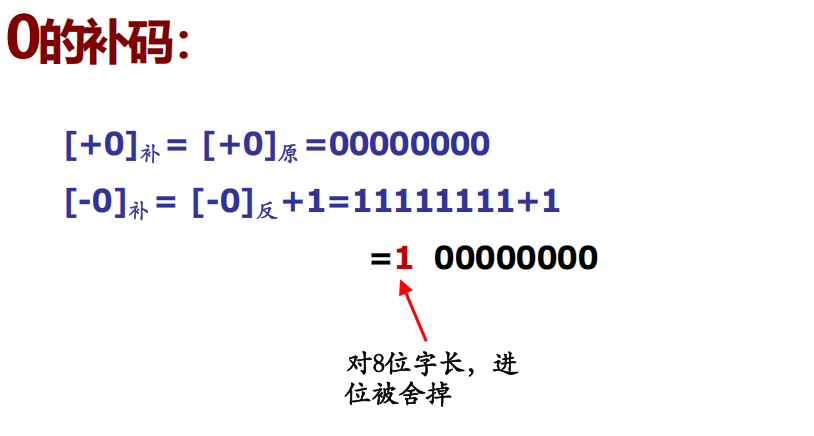

原码:就是直接用二进制表示的数值,符号位为0表示正数,为1表示负数。但是注意到+0原码为0000 0000B,-0原码为1000 0000B,数0的原码不为1,计算机用原码表示数不是件好事

反码:符号位不变,其余位求反,容易发现0的反码也不是唯一的

补码:正数的补码等于其原码;负数的补码等于其反码加1,并忽略进位产生的新最高位。补码的优势在于:零的表示唯一,且加减运算可以统一处理,无需区分符号。

特殊数10000000

- 对无符号数:

(10000000)B=128 - 在原码中定义为:

(10000000)B=-0 - 在反码中定义为:

(10000000)B= -127 - 在补码中定义为:

(10000000)B= -128(这句话的意思是,如果一个数的补码是10000000B,那这个数是-128)

- 加法性质:

[X + Y]补 = [X]补 + [Y]补。- 例:计算

[+33 + (+11)]补,直接对[33]补与[11]补执行二进制加法。

- 例:计算

- 减法性质:

[X - Y]补 = [X]补 - [Y]补;[X - Y]补 = [X]补 + [-Y]补(通过求[-Y]补简化运算,[-Y]补为对[Y]补包括符号位的所有位取反加一)。

- 补码与原码转换:

[X]原 = [[X]补]补,即对补码符号位不变,其余位取反加一,得到原码。

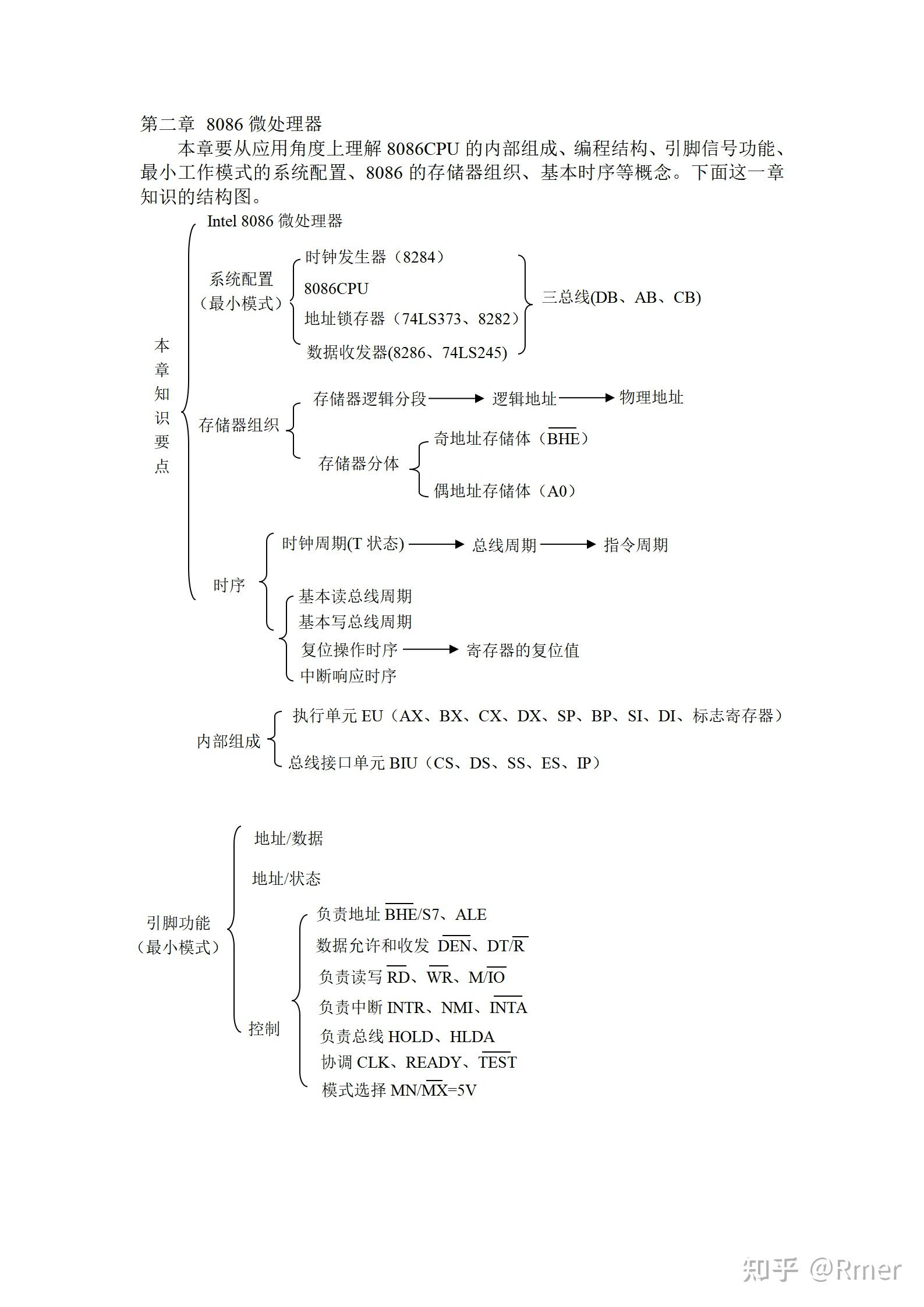

8086/8088微处理器简介

8086/8088是intel第三代处理器。

采用并行流水线工作方式

对内存空间实行分段管理,并且支持协处理器。

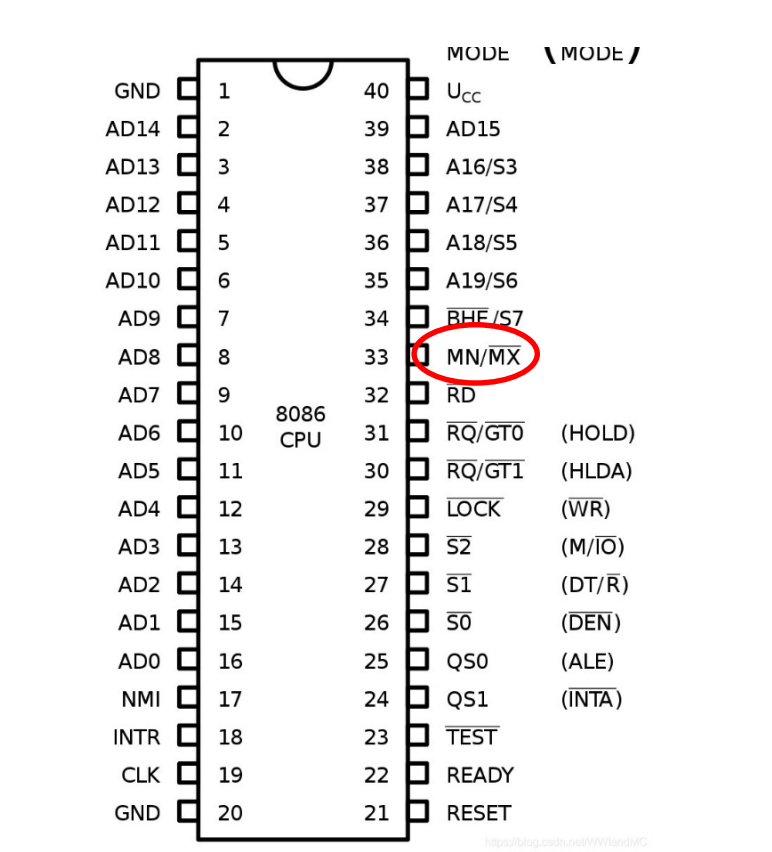

8088/8086可工作于两种模式下,

- 最小模式为单处理器模式, 所有控制信号由微处理器产生

- 最大模式为多处理器模式, 部分控制信号由外部总线控制器产

生,用于包含协处理器的情况下

8086是工作在最小还是最大模式由MN/MX引线的状态决定

- \(MN\)/\(\overline{MX}\)=0——工作于最大模式

- \(MN\)/\(\overline{MX}\)=1——工作于最小模式

8086引脚与结构

引脚

地址和数据引脚:

AD0—AD15:地址和数据信号(分时复用 )

在传送地址信号时为单向,传送数据信号时为双向

A16/S3--A19/S6-: 高4位地址信号,与状态信号分时复用

主要控制引脚

WR (Write): 写信号,低电平有效时表示CPU正在执行写操作;

RD (Read): 读信号,低电平有效时表示CPU正在执行读操作;

IO/M (Input-Output/Memory): 输入输出/存储器选择,为"0"表示访问接口设备,为"1"表示访问内存;

DEN (Data ENable): 数据使能信号,低电平有效时,允许进行读/写操作;

- DT/#R (Data Transmit/Receive): 数据发送/接收控制,控制数据收发器的传送方向;

- ALE (Address Latch Enable): 地址锁存使能信号,用于地址和数据分时复用的控制;

- RESET (System Reset): 系统复位信号,用于初始化CPU;

- READY (System Ready): 系统就绪信号,表示外设是否准备好传送数据,用于同步CPU与慢速设备。

例子:当#WR=1,#RD=0,#IO/M=1时

表示CPU当前正在进行读存储器操作

中断请求和响应引脚

- INTR:可屏蔽中断请求输入端

- NMI: 非屏蔽中断请求输入端

INTA: 中断响应输出端

总线保持引脚

- HOLD:总线保持请求信号输入端,当CPU以外的其他设备要求

占用总线时,通过该引脚向CPU发出请求 - HLDA:总线保持响应信号输出端,CPU对HOLD信号的响应信

号。

8088的外部总线宽度是8位,8086为16位,且访问存储器和输入输出控制信号含义不同

8088——IO/#M=0表示访问内存,8086——#IO/M=1表示访问内存

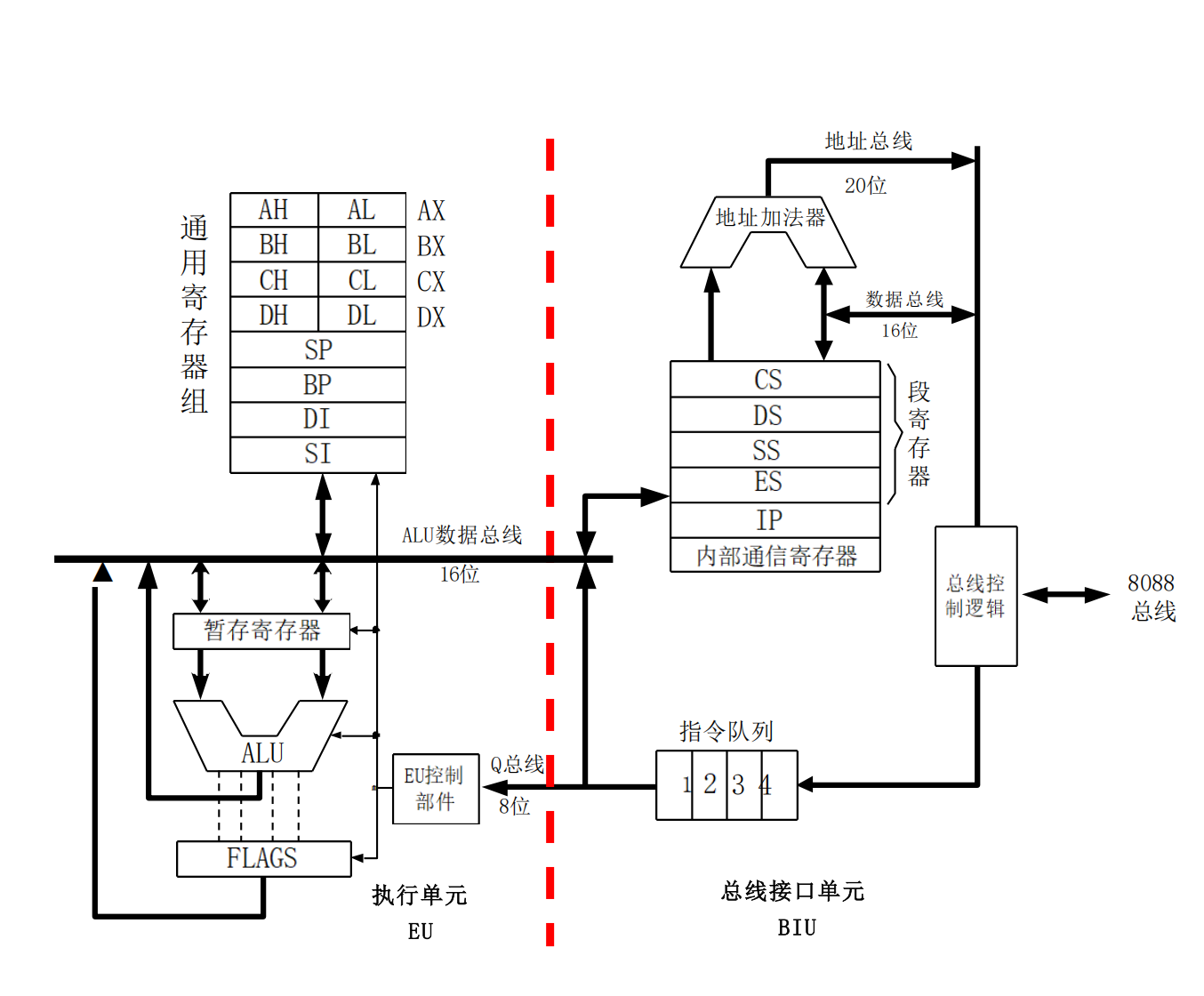

内部结构

8086内部结构大致分为总线接口单元(BIU)和执行单元(EIU),二者内部寄存器都是16位的,填空题:指令预取队列的存在使EU和BIU两个部分可同时进行工作。

EU:执行单元

大致有三个部分组成

- 八个通用寄存器

- 算术逻辑单元(ALU),负责加减乘除等运算,其中标志寄存器(FLAGS):记录运算状态(如 ZF 零标志、CF 进位标志、OF 溢出标志),供后续指令判断。

- EU 控制单元从 BIU 的指令队列取指令,解码后控制 ALU 和寄存器执行,支持指令流水线(取指与执行重叠)。

BIU

功能

- 从内存中取指令到指令预取队列

- 指令预取队列是并行流水线工作的基础

- 负责与内存或输入/输出接口之间的数据传送

寄存器

一、通用寄存器(8个)

1. 数据寄存器(4个)

| 寄存器 | 功能描述 | 特殊用途 |

|---|---|---|

| AX | 累加器,可拆分AH(高8位)/AL(低8位) | 算术运算、I/O操作默认寄存器 |

| BX | 基址寄存器,可拆分BH/BL | 间接寻址默认与DS关联 |

| CX | 计数寄存器,可拆分CH/CL | 循环/移位指令的默认计数器 |

| DX | 数据寄存器,可拆分DH/DL | 双字运算时存放高位字,I/O端口地址间接寻址 |

2. 地址指针与变址寄存器(4个)

| 寄存器 | 功能描述 | 典型应用场景 |

|---|---|---|

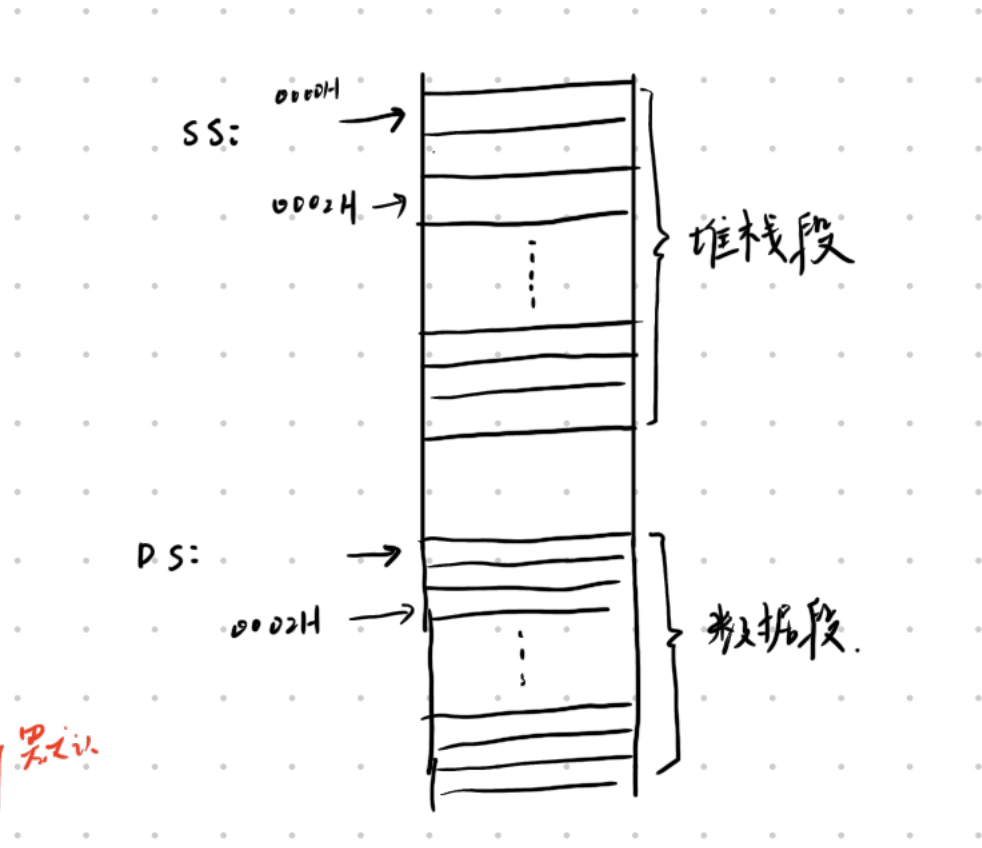

| SP | 堆栈指针寄存器 | 指向堆栈栈顶,配合SS段寄存器使用,默认栈顶地址(SP)小于栈底地址,在图中堆栈向上生长 |

| BP | 基址指针寄存器 | 访问堆栈中的参数或局部变量(默认与堆栈段SS关联) |

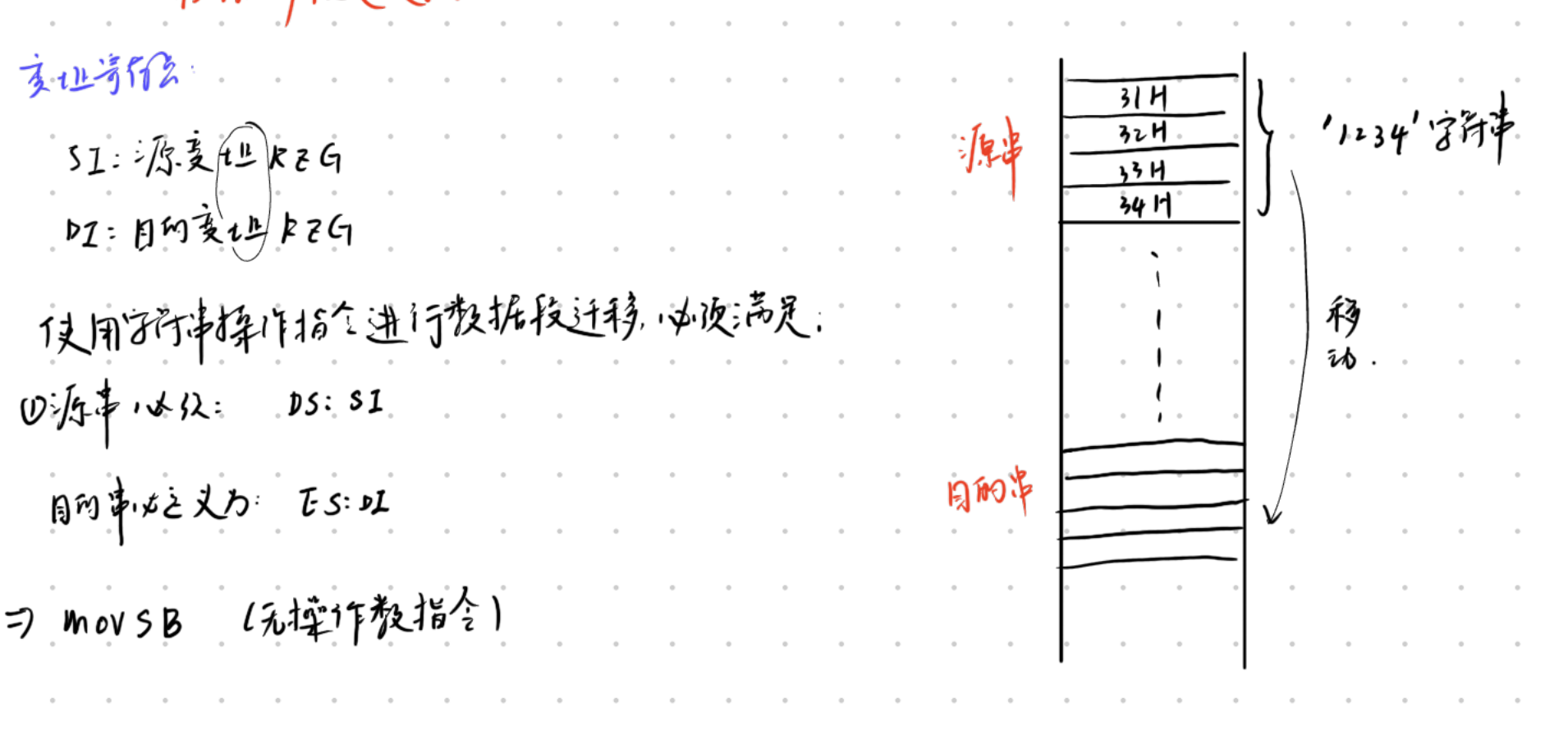

| SI | 源变址寄存器 | 字符串操作的源操作数地址指针(默认与数据段DS段关联) |

| DI | 目的变址寄存器 | 字符串操作的目的操作数地址指针(默认与ES段关联) |

SI和DI看起来很抽象,主要是服务于数据的快速迁移,举个例子:

二、段寄存器(4个)

| 寄存器 | 功能描述 | 关联默认操作 |

|---|---|---|

| CS | 代码段寄存器 | 存放当前执行代码的段基址 |

| DS | 数据段寄存器 | 存放静态数据和局部变量的段基址(默认与BX/SI/DI等关联) |

| SS | 堆栈段寄存器 | 存放堆栈段的段基址(默认与SP/BP关联) |

| ES | 附加段寄存器 | 用于字符串操作的目的段或扩展数据段 |

举个寻址的例子

mov BX, 0002H

mov BP, 0002H

mov AL, 34H ;00110100B

mov [BX],AL ;AL内容写入偏移地址为BX的数据段

mov [BP],AL ;AL内容写入偏移地址为BP的堆栈段

mov AL,56H

mov DS:[BP] 0003H ;添加段超越前缀来强制改段

三、控制寄存器(2个)

1. IP(指令指针寄存器)

- 功能:指向下一条执行指令的偏移地址,与代码段CS相关联

2. FLAGS(标志寄存器)

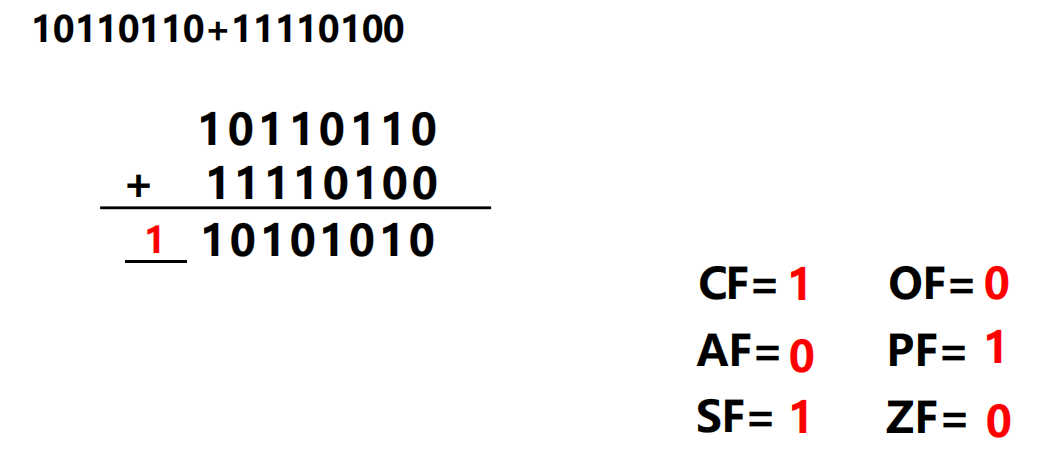

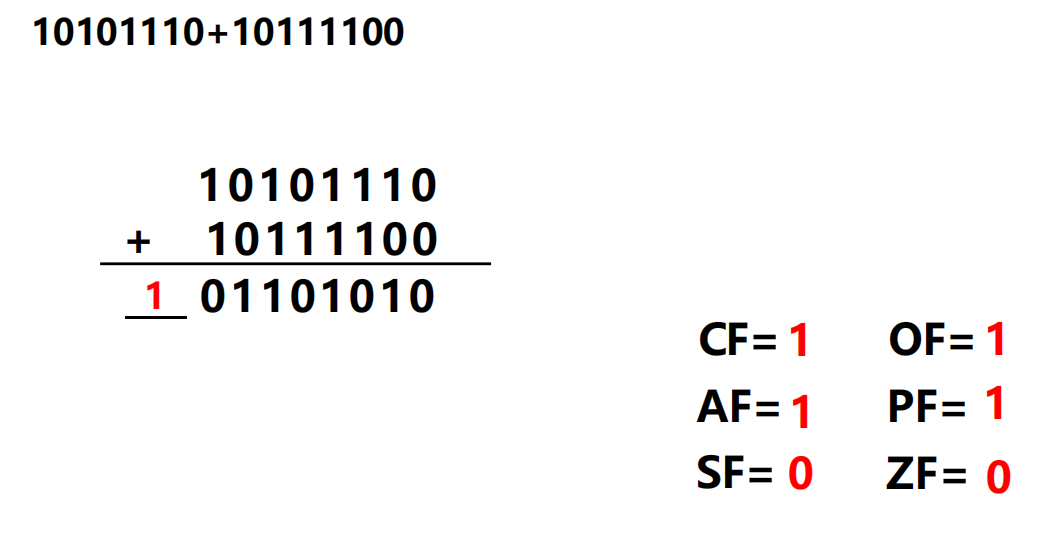

- 结构:16位寄存器,存放运算结果的特征,其中有6个状态标志位(CF,SF,AF,PF,OF,ZF)3个控制标志位(IF,TF,DF),一般而言无符号数关注CF,有符号数关注OF和SF,FLAGS寄存器会对绝大多数算术和逻辑运算指令的执行结果做出响应

- 状态标志:

标志 含义 触发条件 CF(Carry Flag) 进位标志 无符号数运算最高位是否产生进位/借位,进位值保存到CF中去 PF(Parity Flag) 奇偶标志 指令执行后,其运算结果的所有位中1的个数是否为偶数 AF(Auxiliary Flag) 辅助进位标志 低四位向高四位进位/借位 ZF(Zero Flag) 零标志 结果为0 SF(Sign Flag) 符号标志 结果最高位为1 OF(Overflow Flag) 溢出标志(-129,+128) 有符号数运算结果超出范围 - 控制标志:

标志 含义 作用 DF 方向标志 控制字符串操作方向(0=递增,1=递减) IF 中断允许标志 允许(1)或禁止(0)可屏蔽中断 TF 陷阱标志 单步执行模式(调试用)

1111 1111 (255) | 1111 1111

+ 0000 0001 (1) | + 0000 0001

---------- | -------------

1 0000 0000 (256) | 0000 0000

↑ |

最高位向后进位 → CF=1 CF=0

两个例题

1.溢出的判断:最高位进位状态XOR次高位进位状态=1,结果溢出,即,最高位进位状态与次高位进位状态不同时,结果溢出

2.手写FLAGS在运算后的变化

存储器寻址

- 硬件限制:8086 内部寄存器、数据总线均为 16 位,但地址总线为 20 位,需寻址 1MB 空间。

- 解决方案:通过分段技术,将内存划分为多个逻辑段(每个段最大 64KB),用 16 位段基址 + 16 位偏移地址组合出 20 位物理地址。

物理地址计算规则

\]

- 段基址:存储于段寄存器(CS/DS/SS/ES),左移 4 位后得到段起始地址。

- 偏移地址:由通用寄存器(BX/BP/SI/DI/IP 等)提供,指向段内具体单元。

- 段首偏移地址为0

- 一个存储单元除具有一个唯一的物理地址外,还具有多个逻辑地址

- 段首地址+FFFFH=段尾地址(例题有一个画图题,参考)

- 逻辑段可以有多个,但只有4种类型 。在一个程序模块中,每种类型的逻辑段最多只能有一个

PPT56-59可以多看,是很好的总结

8086总线周期与时序

- 时钟频率 :CPU内数字脉冲信号每秒钟的震荡次数,也称主频

- 时钟周期是CPU处理动作的最小时间单位

- 总线周期:CPU通过总线对存储器(I/O接口)进行一次读(写)操作所需的时间

- 8086/8088处理器中,1个基本总线周期一般由4个时钟周期组成,T1 T2 T3 T4分别是,发出地址 准备传输 存取数据 周期结束

微机基础与x86架构的更多相关文章

- x86架构手机跑安卓好吗?(脑补)

华硕低价位手机ZenFone一推出就掀起市场话题,许多人也对ZenFone所采用的Intel Atom处理器有所意见,深怕其相容性问题无法正确执行应用程式App,这究竟是怎么回事呢? Intel近几年 ...

- X86架构CPU常识(主频,外频,FSB,cpu位和字长,倍频系数,缓存,CPU扩展指令集,CPU内核和I/O工作电压,制造工艺,指令集,超流水线与超标量)

1.主频 主频也叫时钟频率,单位是MHz,用来表示CPU的运算速度. CPU的主频=外频×倍频系数.很多人认为主频就决定着CPU的运行速度,这不仅是个片面的,而且对于服务器来讲,这个认识也出现了偏差. ...

- x86架构的android手机兼容性问题

x86架构的android手机兼容性问题 http://www.cnblogs.com/guoxiaoqian/p/3984934.html 自从CES2012上Intel发布了针对移动市场的Medf ...

- X86 架构和 ARM 架构

1.关于x86架构 X86是一个intel通用计算机系列的标准编号缩写,也标识一套通用的计算机指令集合,X86是由Intel推出的一种复杂指令集,用于控制芯片的运行的程序,现在X86已经广泛运用到了家 ...

- 基于x86架构的内核Demo的详细开发文档

http://hurlex.0xffffff.org/ 这里是hurlex这个基于x86架构的内核Demo的详细开发文档, 包含PDF文档和生成PDF的XeLaTex源码和文档每章节的阶段代码. 你可 ...

- ARM架构和X86架构对比

转载地址 我们就ARM架构的系统与X86架构系统的特性进行一个系统分析,方便用户在选择系统时进行理性.合理的比价分析. 一.性能: X86结构的电脑无论如何都比ARM结构的系统在性能方面要快得多.强得 ...

- X86架构

在接触BIOS的时候,都需要对PC架构有一定的认知.目前的PC架构绝大多数都是Intel的X86架构,貌似也是因为INTEL的这个X86架构早就了目前INTEL如日中天的地位. 废话不多说,X86架构 ...

- kernel生成针对x86架构的tags和cscope数据库

最近下载了kernel的最新源码4.15版,但下载后的linux内核不仅包含了x86架构的函数还包含了如:arm.powerPC等等其他架构的函数,如果直接生成tags文件,将来查找时,多种架构的同名 ...

- ARM和X86架构

重温下CPU是什么 中央处理单元(CPU)主要由运算器.控制器.寄存器三部分组成.运算器起着运算的作用,控制器负责发出CPU每条指令所需要的信息,寄存器保存运算或者指令的一些临时文件以保证更高的速度. ...

- ARM与X86架构的对决[整编]

CISC(复杂指令集计算机)和RISC(精简指令集计算机)是当前CPU的两种架构.它们的区别在于不同的CPU设计理念和方法.早期的CPU全部是CISC架构,它的设计目的是 CISC要用最少的机器语言 ...

随机推荐

- [abc302f] Merge Set

F - Merge Set 显然要建图 首先,我们有一个粗略的想法,对于同一集合\(S_i\)内的元素,\(S_{i,j}\)与\(S_{i,j+1}\)间连一条无向的标号为\(i\)的边 那么题目显 ...

- Golang基础笔记七之指针,值类型和引用类型

本文首发于公众号:Hunter后端 原文链接:Golang基础笔记七之指针,值类型和引用类型 本篇笔记介绍 Golang 里的指针,值类型与引用类型相关的概念,以下是本篇笔记目录: 指针 值类型与引用 ...

- C# 选择文件保存路径

public static string SetSaveFilePath(string filterType= "所有文件|*.*",string fileName="我 ...

- C# 调用 WebServices Api接口 WSDL 通过WebResponse 请求

https://www.cnblogs.com/Sheldon180621/p/14498646.html 方法一.引用*.wsdl文件 WebService服务端会提供wsdl文件,客户端通过该文件 ...

- openWrt安装三方插件

前言 openWrt是一款开源的路由器系统,其最大的优点就是 支持第三方扩展插件. 新增的插件基本都会在左侧的服务菜单中展现,通过此入口就可以使用插件功能. 大部分openWrt固件都帮你装好了ope ...

- Restcloud ETL开箱即用-永久免费

2022年4月18日,国内领先的数据集成企业RestCloud发布了全新的ETL社区版本. RestCloud ETL社区版是一款完全国产化自主研发创新的全WEB化.开箱即用.永久免费的数据集成工具, ...

- MacOS-“System Information”这个App用做USB设备的检测与设备文件的确定

"System Information"这个Apple自带的GUI小App是检测USB硬件的; 如图所示: 而Linux上是 lsusb 与 lspci 这类command lin ...

- Gson如何自定义Calendar序列化/反序列化

直接开干吧,假设有这么一个类: @Data @AllArgsConstructor class BeanSample { public Calendar birthday; @Override pub ...

- Behavior designer 行为树插件 笔记

插件下载:https://files-cdn.cnblogs.com/files/sanyejun/BehaviorDesigner1.6.4.7z 参考资料:https://blog.csdn.ne ...

- luoguP1163-二分

银行贷款 题目链接:https://www.luogu.com.cn/problem/P1163 本题思路: orz公式 数学公式给出n,m,k,求贷款者向银行支付的利率 p,使得: $ \sum_{ ...