DC-DC converter Control techniques

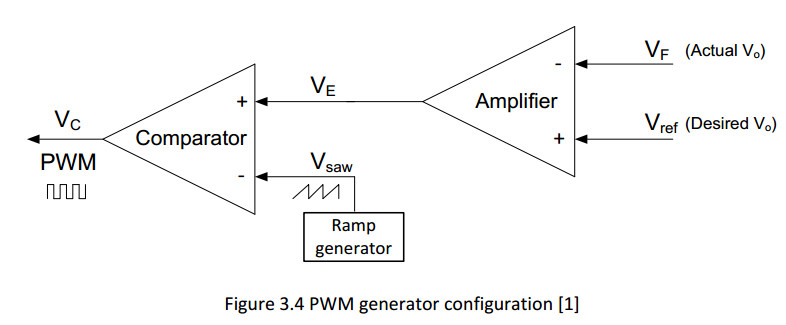

As shown in figure 3.4, PWM controller contains two main parts;

voltage error-amplifier and voltage comparator.

The error-amplifier compares the feedback voltage VF (applied to inverting input)

to reference voltage VREF (applied to non-inverting input)

then their difference which is called voltage error signal VE

after amplification is applied to noninverting input of voltage comparator.

Comparator compares this error voltage to sawtooth ramp VSAM that is generated by ramp generator,

if voltage VE is higher than VSAW output voltage of comparator goes high but

when VE is lower than VSAW the output of comparator goes low

to adjust the switching duty cycle.

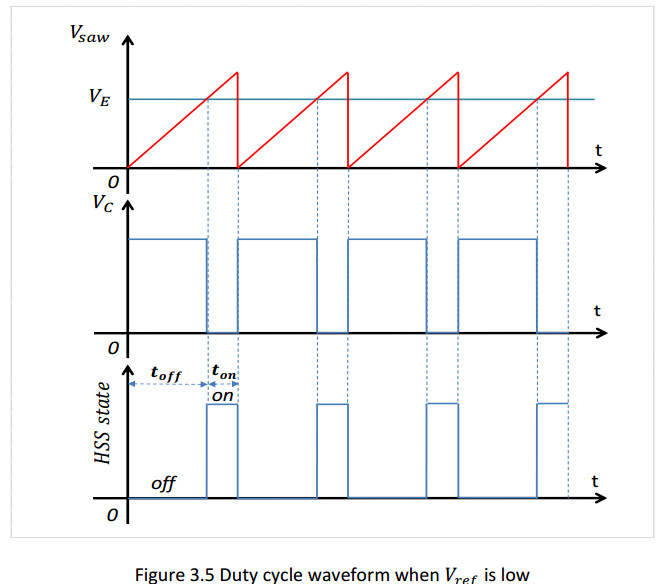

error voltage VE is inversely proportional to voltage reference VREF,

for example when VREF is low, error voltage VE is increased by error amplifier to adjust the switching duty cycle.

As can be seen in figure 3.5 when the error voltage is high the pulse width of PWM wave

at the output of voltage comparator (VC ) is increased to keep off High side switch (PMOS) for

the most time of the each cycle in order to reduce duty cycle to regulate output voltage.

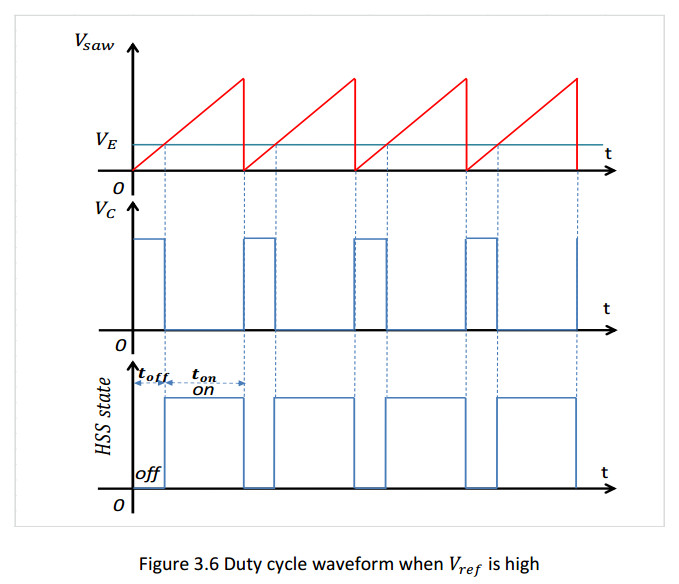

Vice versa as shown in figure 3.6 when VREF is high error amplifier reduces VE to keep on

the HSS for a most time of each period in order to adjust output voltage [14].

http://www.chinabaike.com/2011/0120/201049.html

From the derivations for the boost, buck, and inverter (flyback), it can be seen that changing the duty cycle controls the steady-state output with respect to the input voltage. This is a key concept governing all inductor-based switching circuits.

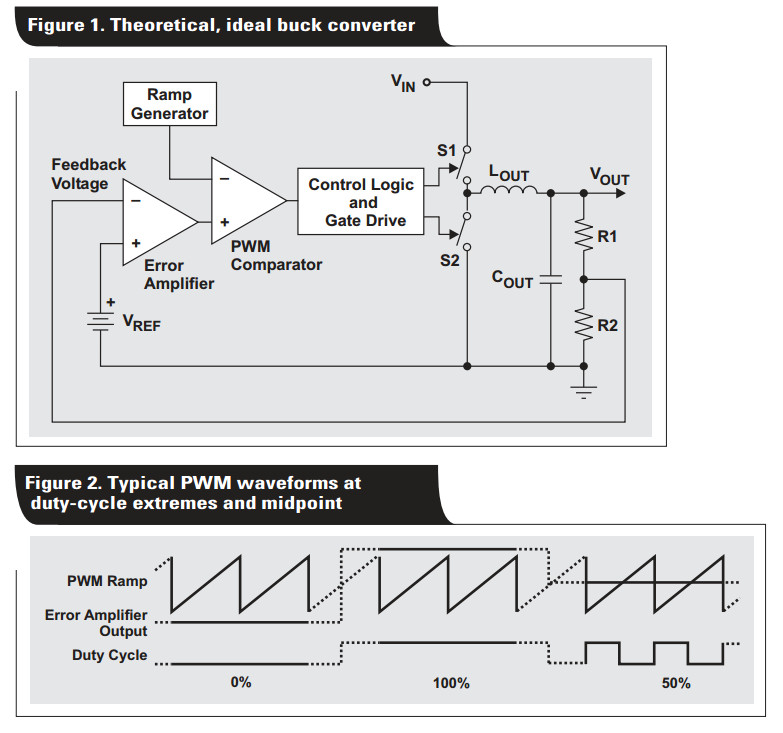

The most common control method, shown in Figure 7, is pulse-width modulation (PWM). This method takes a sample of the output voltage and subtracts this from a reference voltage to establish a small error signal (VERROR). This error signal is compared to an oscillator ramp signal. The comparator outputs a digital output (PWM) that operates the power switch. When the circuit output voltage changes, VERROR also changes and thus causes the comparator threshold to change. Consequently, the output pulse width (PWM) also changes. This duty cycle change then moves the output voltage to reduce to error signal to zero, thus completing the control loop.

Figure 8 shows a practical circuit using the boost topology formed with the MAX1932.

This IC is an integrated controller with an onboard programmable digital-to-analog converter (DAC).

The DAC sets the output voltage digitally through a serial link.

R5 and R8 form a divider that meters the output voltage.

R6 is effectively out of circuit when the DAC voltage is the same as the reference voltage (1.25V).

This is because there is zero volts across R6 and so zero current.

When the DAC output is zero (ground), R6 is effectively in parallel with R8.

These two conditions correspond to the minimum and maximum output adjustment range of 40V and 90V, respectively.

Next, the divider signal is subtracted from the internal 1.25V reference and then amplified.

This error signal is then output on pin 8 as a current source.

This, in conjunction with the differential input pair, forms a transconductance amplifier.

This arrangement is used because the output at the error amp is high impedance (current source),

allowing the circuit's gain to be adjusted by changing R7 and C4.

This arrangement also provides the ability to trim the loop gain for acceptable stability margins.

The error signal on pin 8 is then forwarded to the comparator and output to drive the power switch.

R1 is a current-sense resistor that meters the output current.

When the current is unacceptably high, the PWM circuit shuts down, thereby protecting the circuit.

The type of switching (topology) in Figures 7 and 8 is classified as a voltage-mode controller (VMC)

because the feedback regulates the output voltage.

For analysis we can assume that if the loop gain is infinite, the output impedance for an ideal voltage source is zero.

Another commonly used type of control is current-mode control (CMC).

This method regulates the output current and, with infinite loop gain, the output is a high-impedance source.

In CMC, the current loop is nested with a slower voltage loop, as shown in Figure 9;

a ramp is generated by the slope of the inductor current and compared with the error signal.

So, when the output voltage sags, the CMC supplies more current to the load.

The advantage of CMC is its ability to manage the inductor current.

In VMC the inductor current is not metered. This becomes a problem because the inductor,

in conjunction with the output filter capacitor, forms a resonant tank that can ring and even cause oscillations.

Current mode control senses the inductor current to correct for inconsistencies.

Although difficult to accomplish, carefully selected compensation components can effectively cancel out this resonance in VCM.

The circuit in Figure 10 uses CMC with the MAX668 controller.

This boost circuit is similar to Figures 7 and 8 except that R1 senses the inductor current for CMC.

R1 and some internal comparators provide a current limit.

R5 in conjunction with C9 filters the switching noise on the sense resistor to prevent false triggering of the current limit.

The MAX668's internal current-limit threshold is fixed; changing the resistor, R1, adjusts the current-limit setting.

The resistor, R2, sets the operating frequency.

The MAX668 is a versatile integrated circuit that can provide a wide range of DC-DC conversions.

The external components of the MAX668 can have high-voltage ratings that provide greater flexibility for high-power applications.

For portable applications that require less power, the MAX1760 and MAX8627 are recommended.

These latter devices use internal FETs, and sense the current by using the FETs' resistance to measure inductor current (no sense resistor required).

DC-DC converter Control techniques的更多相关文章

- PID DC/DC Converter Controller Using a PICmicro Microcontroller

http://www.microchip.com/stellent/idcplg?IdcService=SS_GET_PAGE&nodeId=1824&appnote=en011794 ...

- Practice safe dc/dc converter

Short-circuit protection is an obvious requirement for a power supply, especially when its load conn ...

- LT1946A-- Transformerless dc/dc converter produces bipolar outputs

Dual-polarity supply provides ±12V from one IC VC (Pin 1): Error Amplifier Output Pin. Tie external ...

- Simple dc/dc converter increases available power in dual-voltage system

The schematic in Figure 1 shows a way to increase the power available from a current-limited 5V supp ...

- Add margining capability to a dc/dc converter

You can easily add margining capability—that is, the ability to digitally adjust the output voltage— ...

- [专业名词·硬件] 2、DC\DC、LDO电源稳压基本常识(包含基本原理、高效率模块设计、常见问题、基于nRF51822电源管理模块分析等)·长文

综述先看这里 第一节的1.1简单介绍了DC/DC是什么: 第二节是关于DC/DC的常见的疑问答疑,非常实用: 第三节是针对nRF51822这款芯片电源管理部分的DC/DC.LDO.1.8的详细分析,对 ...

- DC/DC与LDO的差别

转自:http://bbs.eetop.cn/thread-459121-1-1.html 在平时的学习中,我们都有接触LDO和DC/DC这一类的电源产品,但作为学生的我们队这些东西可能了解不够深刻, ...

- DC DC降壓變換器ic 工作原理

目前DC/DC轉化器大致可分為:升壓型dc dc變化器.降壓型dc dc變化器及可升壓又可降壓dc dc變換器.我們今天主要提一下降壓型dc dc變換器的原理: 見下圖降壓變換器原理圖如圖1所示, 當 ...

- DC DC電路電感的選擇

注:只有充分理解電感在DC/DC電路中發揮的作用,才能更優的設計DC/DC電路.本文還包括對同步DC/DC及異步DC/DC概念的解釋. DCDC電路電感的選擇 簡介 在開關電源的設計中電感的設計為 ...

随机推荐

- javascript你不知道的This

<你不知道的javascript>这本书读了有好几遍了,似乎每一次读都有新发现,有些内容并不是一下子可以弄懂的,每次读似乎都能明白一些概念.再重读一下this关键字.这个概念非常灵活,也非 ...

- H5移动端视频问题(苹果全屏播放问题等)

iphone上,手动.自动.窗口化等问题 iphone窗口化 解决方案: 通过canvas + video标签结合处理 原理: 获取video的原图帧,通过canavs绘制到页面. 我们一般在苹果上在 ...

- MyBatis3-与Spring MVC 4集成

继前一篇的例子http://www.cnblogs.com/EasonJim/p/7052388.html,已经集成了Spring框架,现在将改造成Spring MVC的项目,并实现如下功能: 1.不 ...

- 洛谷 P2077 红绿灯 题解

题目传送门 这道题一秒一秒的扫描一定会超时,所以就用一种O(N)的算法. #include<bits/stdc++.h> using namespace std; ],b[],c[],x= ...

- PHP 文件夹操作「复制、删除、查看大小、重命名」递归实现

PHP虽然提供了 filesize.copy.unlink 等文件操作的函数,但是没有提供 dirsize.copydir.rmdirs 等文件夹操作的函数(rmdir也只能删除空目录).所以只能手动 ...

- 06 java 基础:java 循环 递归

1 递归实现 1 + 2 +3 +4 +5 + .... +100 public static int addSum(int num){ if(num == 1) return 1; return n ...

- 错误:Could not create the Android package. See the Output (Build) window for more details

错误:Could not create the Android package. See the Output (Build) window for more details. Mono For An ...

- LoadRunner配置方案

1.配置方案运行时设置 选择“Tools”>“Options”.在“Options”对话框有“Run-Time Settings”(运行时设置).“Timeout”(超时).“Run-Time ...

- eclipse maven 配置

http://www.cnblogs.com/little-YTMM/p/5970878.html

- 洛谷P3857 [TJOI2008]彩灯 [线性基]

题目传送门 彩灯 题目描述 Peter女朋友的生日快到了,他亲自设计了一组彩灯,想给女朋友一个惊喜.已知一组彩灯是由一排N个独立的灯泡构成的,并且有M个开关控制它们.从数学的角度看,这一排彩灯的任何一 ...