Metastability 亚稳态问题

亚稳态问题

各种跨时钟域的问题都会归结于亚稳态的问题,IP设计时钟域不超过两个,对于CDC设计要求不高;对于SoC设计来说,CDC处理十分重要

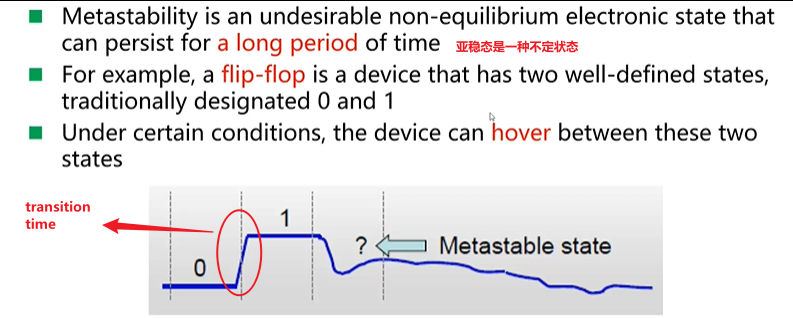

1.什么是亚稳态?

- transition time 是可以计算出来的值,与output load(输出负载),输出负载越大transition time 越大

- transition time 还与自身的驱动能力有关

- 不管怎样,transition time是电平能够正常进行0和1之间跳变的值,亚稳态则不相同,如果经过某些因素,输出状态会在0和1之间的状态震荡,并且经过很长一段时间之后,才能稳定到0和1之间的一个状态;并且这个状态可以作为门电路的输出,可能会驱动其他的门电路,会有较大的概率形成亚稳态

- 在一个节点形成亚稳态之后,会很快的进行扩散

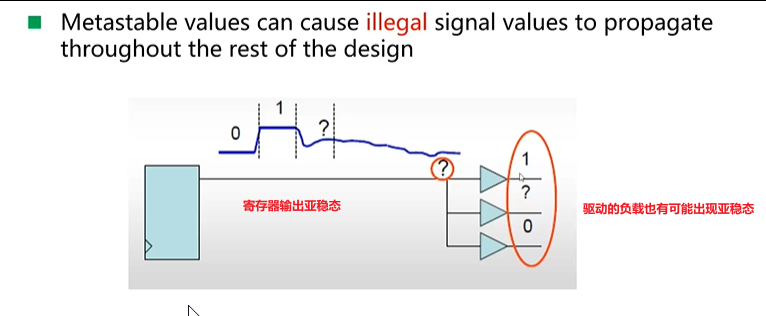

2.亚稳态的危害

- 亚稳态出现后进行传播

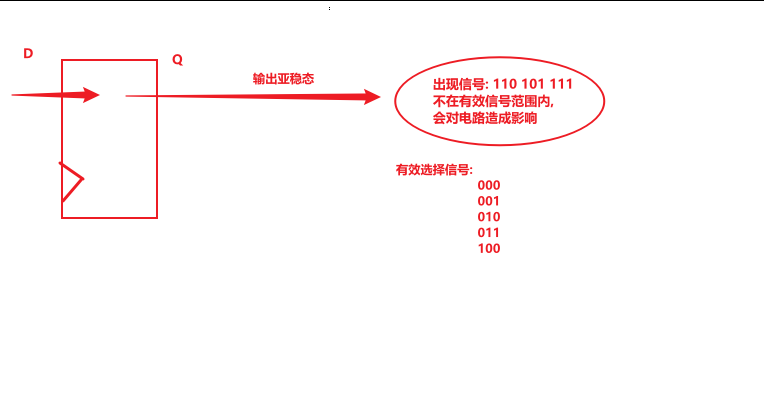

- 亚稳态出现,稳定在一个值,这个0-1之间值,导致后续电路出现范围之外的值(无关项),会给电路带来未知的影响

2.1 亚稳态传播

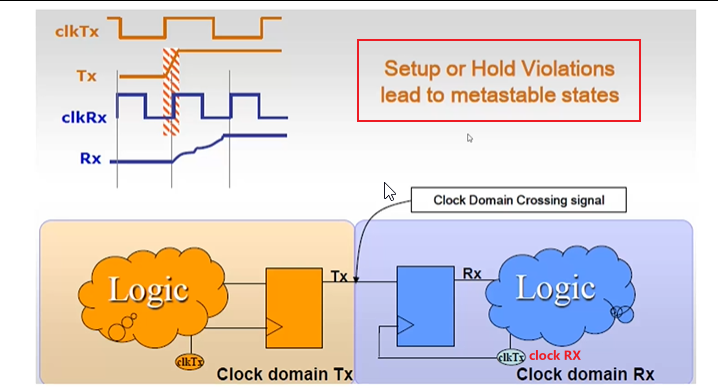

对于寄存器来讲,时钟有效沿来临的时候,会采样D端值,将D端的值同步到Q端;时钟的有效沿来临之前一段时间,要保持信号稳定,称为setup time,在时钟有效沿来临之后的一段时间,信号依然要保持稳定,称为hold time,在setup time和hold time之间,输入发生了变化,中间的变化会形成不定态的传播,在采样的时候D端数据发生变化,就会形成亚稳态

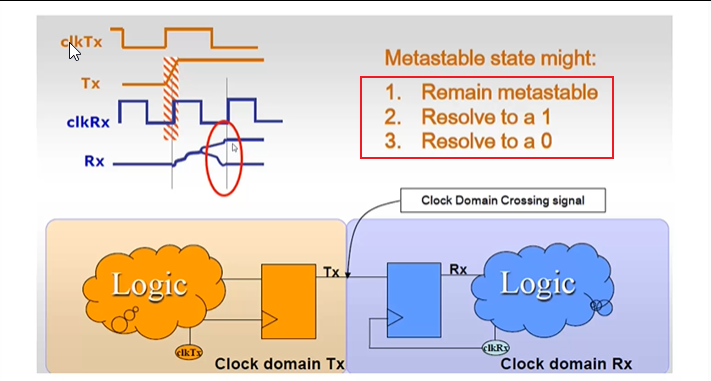

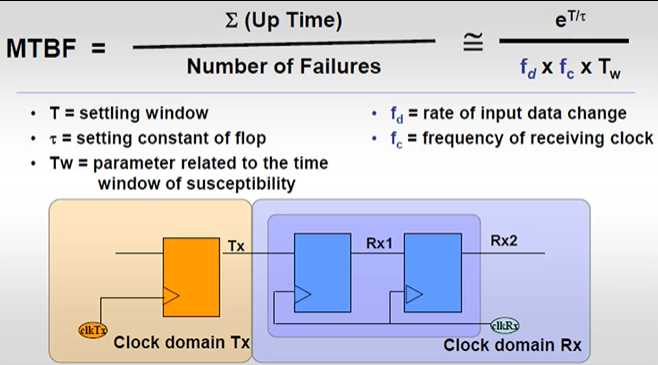

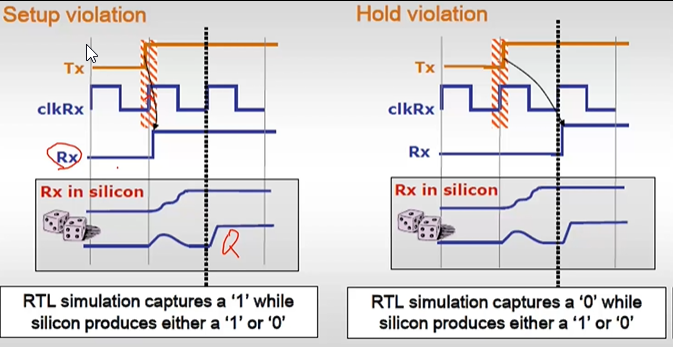

- 上图有两个时钟域,Tx输出的信号跳变的范围,遇到Rx时钟有效沿的变化,形成亚稳态

- 异步电路就是两个电路的时钟源是没有相位关系的,异步电路不能通过STA技术进行保证,需要进行跨时钟域的同步

3.亚稳态的状态

形成亚稳态之后,经过一定的震荡时间之后,亚稳态会回到0,1或一直震荡

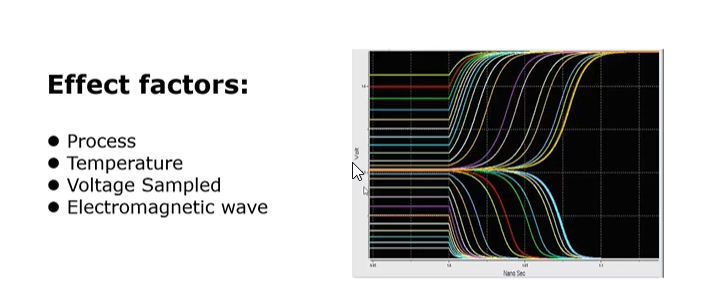

震荡时间与什么有关?

- Process - 制造工艺

- Temperature - 温度

- Voltage Samle - 电压

- Electromagnetic wave - 电磁波

- PVTE -- 延迟,布局布线.....都需要考虑的影响,主要是后端设计进行考虑

4.如何解决亚稳态

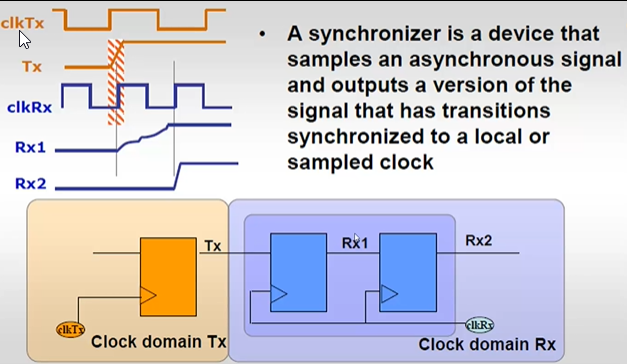

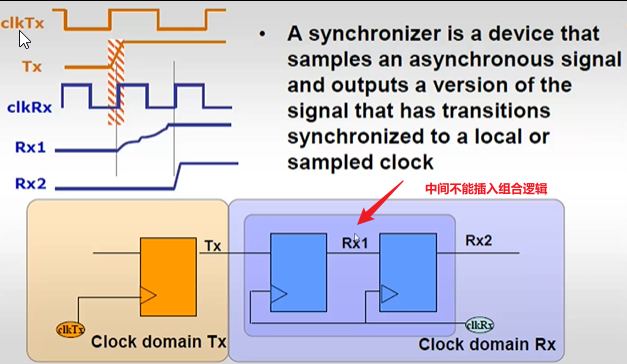

4.1 同步一位信号(同步器)

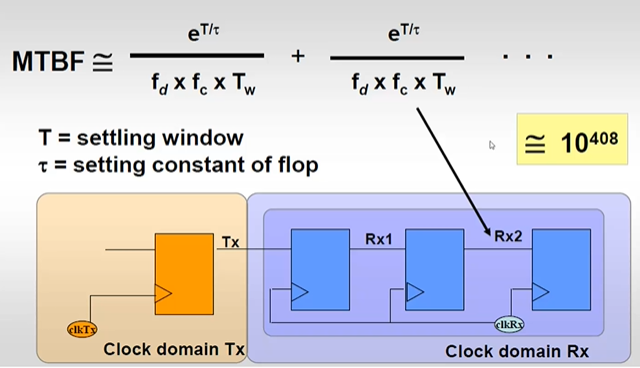

- 多打一拍 -- 使用两个寄存器

- Rx1没有发生亚稳态,Rx2也不会发生亚稳态;Rx1发生了亚稳态,那么在这个时钟周期之内有很大的可能性稳定到某一个值,那么再用一个寄存器Rx2多打一拍,则Rx2就是一个稳定的值

- 如果Rx1的震荡周期如果非常长,那么Rx2也有可能产生亚稳态,但是这种概率很小

- 1bit信号,使用两个寄存器打两拍的方式,可以解决亚稳态的问题,但是两个寄存器之间不能有任何的组合逻辑

- 一般公司中都会有这种跨时钟域处理方式的库文件,只要进行调用就行了,方便和后端进行同步,提高效率

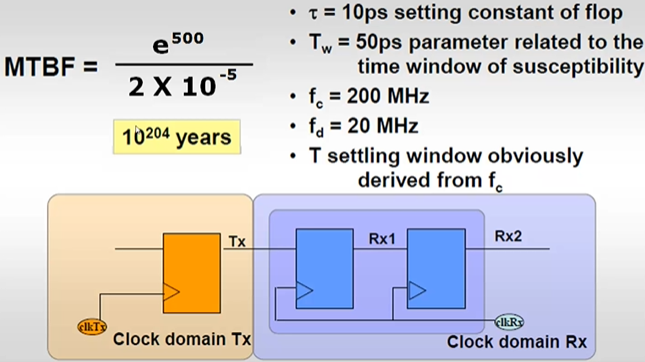

4.2 MTBS-Mean Time Between Failure

- 电路中出现两次亚稳态之间的时间间隔

- fd - 输入端数据变化的频率,信号输入的频率

- fc - 采样频率,有效沿来临的频率

- 输入信号频率越高,引起亚稳态失效的时间越短,亚稳态失效的频率越高

- 采样频率越快,采到在setup time和hold time之间信号的可能性越高,平均失效时间越短,在某个时间内亚稳态频率越快

- MTBF - 数值非常大,说明两次亚稳态之间的时间非常长,认为不发生亚稳态

使用三个寄存器处理1bit信号

- 时钟信号高的时候,可以使用三个寄存器(同步器)处理

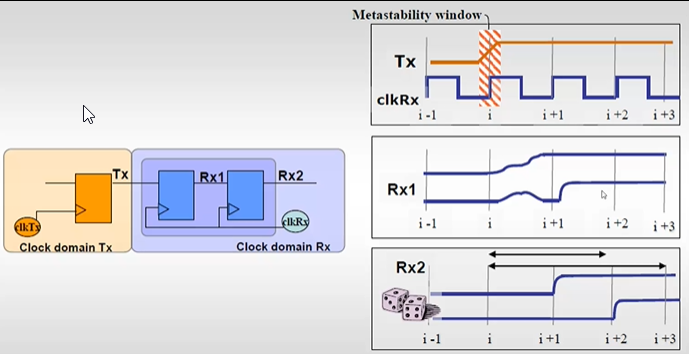

4.3 Synchronizer effect - latency uncertainty

- Tx输入信号传递到Rx2的时间是不确定的,Rx1产生亚稳态,寄存器1,从clkRx上升沿开始采样,采集到的信号是亚稳态信号并传递给Rx1,Rx1在一个周期内,回归到1或0状态;当Rx1回归到1状态的时候,Rx2可以在i+1上升沿的时候采样到Rx1的信号;如果Rx1稳定到0状态,在i+1上升沿,Rx1会跳变为1,Rx2仍然为0,当i+2的上升沿的时候,Rx1保持为1,Rx2采样Rx1的信号变为1

- 由于亚稳态的存在,Tx信号传递到Rx2端的时间,可能是一个周期,也可能是两个周期,是不确定的

RTL simulation does not model silicon behavior accurately

- 仿真工具是不会仿真出来亚稳态问题的,仿真器是非黑即白的

- 检测亚稳态问题的时候,通过后仿真的形式很难发现

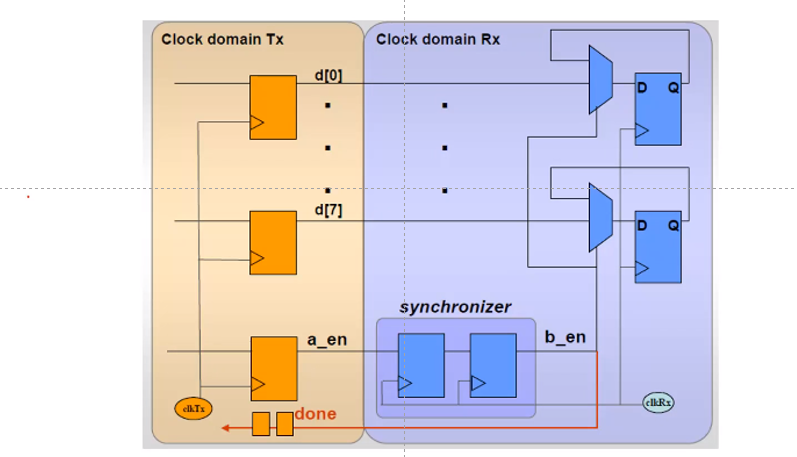

4.4 同步多位信号

假设同步8bit信号经过时钟域

- 给每一位信号用二级同步器,是不可以的,因为亚稳态会导致latency uncertainty,不同位数据接收信号是不同步的

- 首先将enable信号进行同步,enable信号表示,8位信号都是ready的,a_en信号拉高,经过1-2个周期之后b_en得到a_en信号,b_en拉高,表示8位信号都是稳定的,可以进行采样,将8位信号采集到寄存器中

- 在信号同步完成之后需要给输入端一个信号,done信号,表示信号同步完成,可以进行下一组信号的传递,done信号也要经过两级同步器

- 使用异步FIFO处理多比特数据跨时钟域问题

- 使用握手机制处理跨时钟域问题

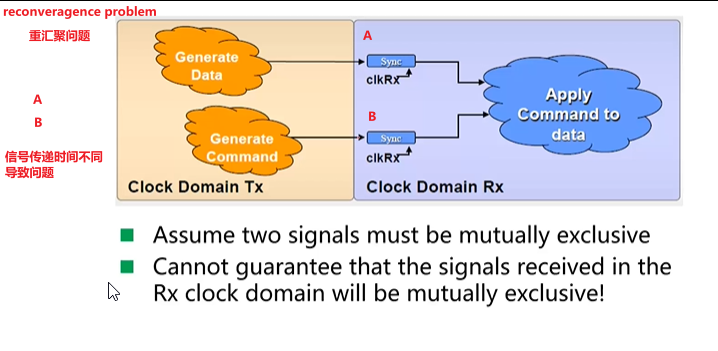

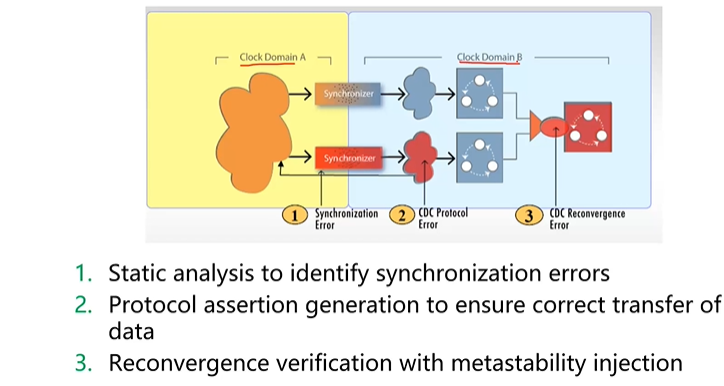

5.reconveragence problem - 重汇聚问题

- 时钟域之间传递信号越少越好

- 时钟域同步机制越简单越好

Metastability 亚稳态问题的更多相关文章

- 组合逻辑的Glitch与时序逻辑的亚稳态

竞争(Race):一个门的输入有两个及以上的变量发生变化时,由于各个输入的组合路径的延时不同,使得在门级输入的状态改变非同时. 冒险或险象(Hazard):竞争的结果,如毛刺Glitch. 相邻信号间 ...

- FPGA中亚稳态相关问题及跨时钟域处理

前言 触发器输入端口的数据在时间窗口内发生变化,会导致时序违例.触发器的输出在一段时间内徘徊在一个中间电平,既不是0也不是1.这段时间称为决断时间(resolution time).经过resolut ...

- 异步FIFO跨时钟域亚稳态如何解决?

跨时钟域的问题:前一篇已经提到要通过比较读写指针来判断产生读空和写满信号,但是读指针是属于读时钟域的,写指针是属于写时钟域的,而异步FIFO的读写时钟域不同,是异步的,要是将读时钟域的读指针与写时钟域 ...

- CDC之Metastability

1 CDC A clock domain crossing occurs whenever data is transferred from a flop driven by one clock t ...

- FPGA中亚稳态——让你无处可逃

1. 应用背景 1.1 亚稳态发生原因 在FPGA系统中,如果数据传输中不满足触发器的Tsu和Th不满足,或者复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery ti ...

- CDC(跨时钟域)和亚稳态

- FPGA异步时钟设计中的同步策略

1 引言 基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统.但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免. ...

- 锁存器 Latch v.s. 触发器 Flip-Flop

转载 http://guqian110.github.io/pages/2014/09/23/latch_versus_flip_flop.html 根据 Wiki: Flip-flop (elec ...

- set_multicycle_path语法说明【转载】

(转载) (其实多看手册就知道原因了) Q:多周期路径中的检查保持时间时刻,为什么默认是在建立时间检查的前一个cycle?请大家谈谈自己的理解. 如:Set_multicycle_path -setu ...

- 嵌入式开发—C语言面试题

嵌入式开发—C语言面试题 源地址:http://blog.csdn.net/xdx2ct1314/article/details/7358929 1. 用预处理指令#define 声明一个常数,用 ...

随机推荐

- Python——第二章:字符的编码encode和解码decode

相关阅读:字符集(Character Set)和编码(Encoding)的历史演化 字符集和编码的总结: 1. ASCII编码: 8bit, 1byte => 256(最大可表示)2. GBK编 ...

- springsecurity 使用浅谈(一)

1. 背景 springsecurity框架主要用于Web应用的认证和授权.所谓认证就是验证当前访问系统的是不是本系统的用户,并且要确认具体是哪个用户.而授权就是经过认证后判断当前用户是否有权 限进行 ...

- DVWA File Upload(文件上传)全等级

File Upload(文件上传) 目录: File Upload(文件上传) 一句话木马的构成 1. Low 1.上传一句话木马1.php 2.中国蚁剑 2.Medium 3. High 4.Imp ...

- 火爆全网的Log4j 漏洞复现GetShell

目录: 一.搭建环境 1. 首先拉一个docker镜像 2. 然后启动环境 二.获取shell 首先,试验一下DNSLog 1. 准备JNDI注入工具 下载 进入目录打包成jar包 2. 利用 生成p ...

- 如何找到 niche 出海细分市场的 IDEA

先说结论就是:看榜单 Why:为什么看榜单? 大家会问为什么?原因很简单: 熟读唐诗三百首,不会作诗也会吟 不天天看榜单上相关的优秀同行,你想干啥 心法就是下苦功夫坚持,量变引起质变,排行榜天天看 竞 ...

- zabbix 默认消息

故障事件: {TRIGGER.NAME}监控状态: {TRIGGER.STATUS}报警严重性: {TRIGGER.SEVERITY}触发结果: {TRIGGER.URL}告警时间:{EVENT.DA ...

- 通用 Mapper 的批量插入实现

具体的 SQL 模板实现如下所示: import org.apache.ibatis.mapping.MappedStatement; import tk.mybatis.mapper.MapperE ...

- 高颜值开源数据可视化工具——Superset 2.0正式发布!

Superset终于迎来了又一个重大的版本更新.使用superset已经近三年的时间了,其为我们提供了数据可视化的解决方案.也成为了最好的商用BI的替代方案. 在Github上本次更新已经发布 ...

- A/B 实验避坑指南:为什么不建议开 AABB 实验

更多技术交流.求职机会,欢迎关注字节跳动数据平台微信公众号,回复[1]进入官方交流群 本文将针对日常开设 A/B 实验过程中一个不太合理的使用方法--AABB 实验进行详细的解释,告诉大家为什么不建议 ...

- Linux 查找进程所在目录

查找进程所在目录位置 # 打出进程ID [root@iZuf64tp28136djioi3ki8Z /]# ps -ef|grep redis root 3451 1 0 Jun10 ? 07:02: ...