一篇文章让你明白CPU缓存一致性协议MESI

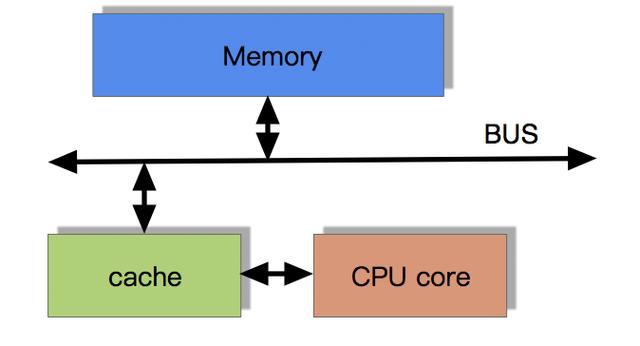

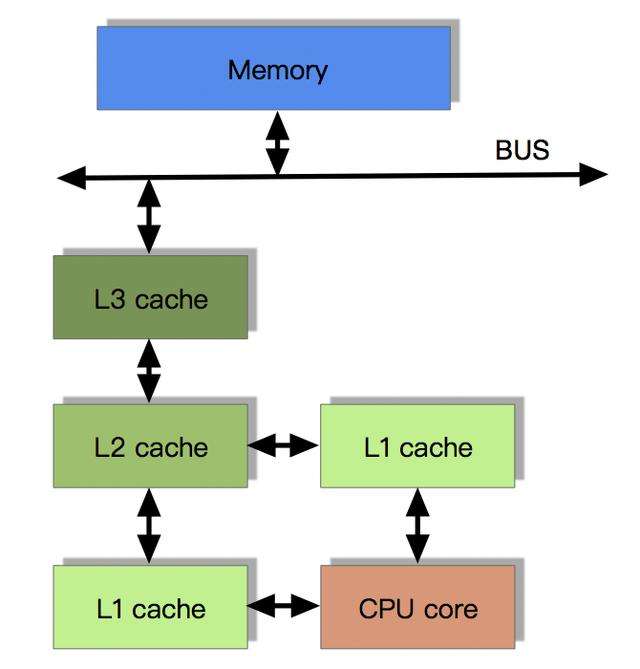

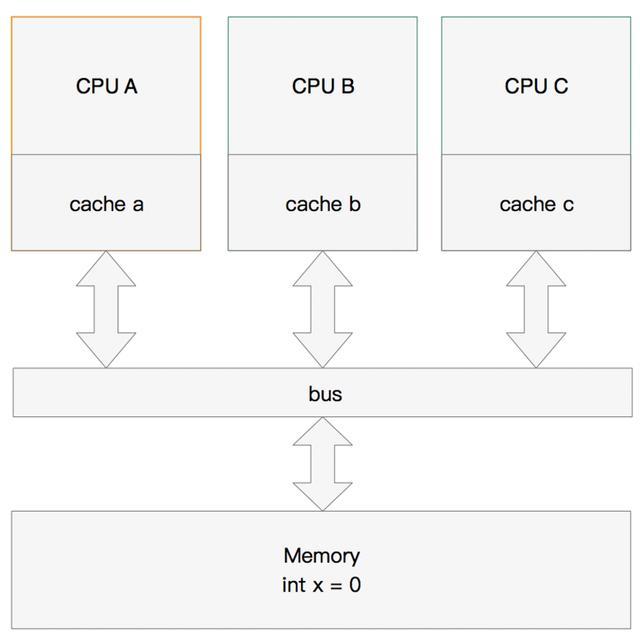

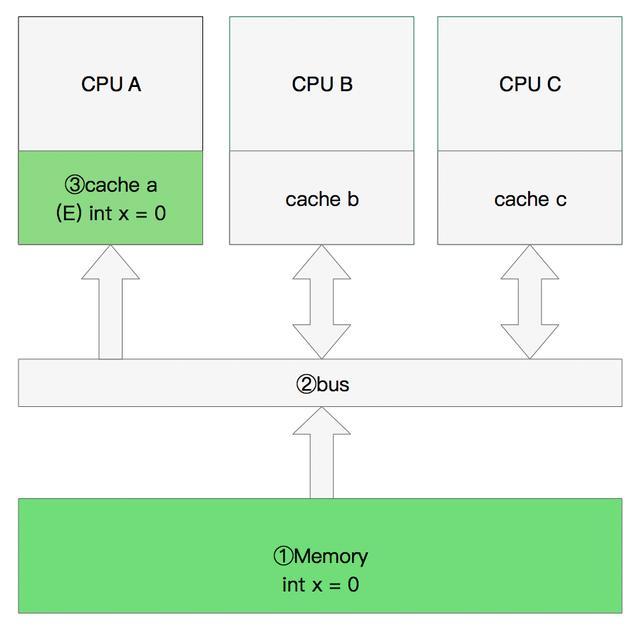

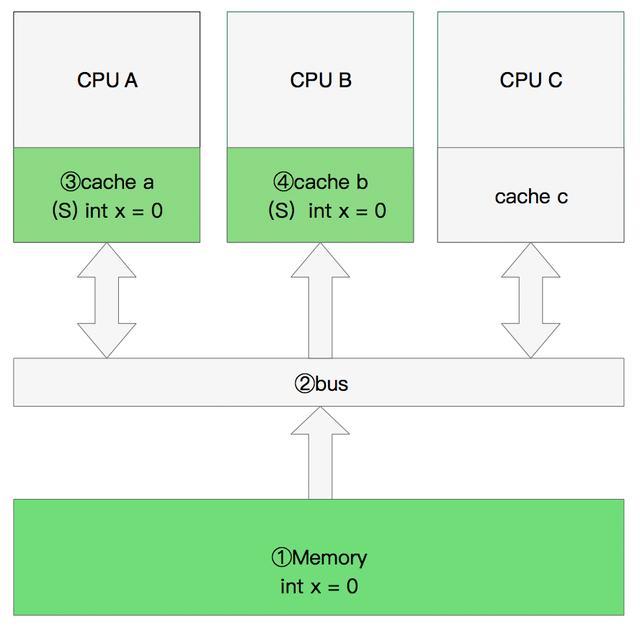

- 程序以及数据被加载到主内存

- 指令和数据被加载到CPU的高速缓存

- CPU执行指令,把结果写到高速缓存

- 高速缓存中的数据写回主内存

void exeToCPUA(){

value = 10;

isFinsh = true;

}

void exeToCPUB(){

if(isFinsh){

/

F{0XCAB)LKNIT0K@G.gif) alue一定等于10?!

alue一定等于10?!assert value == 10;

}

}

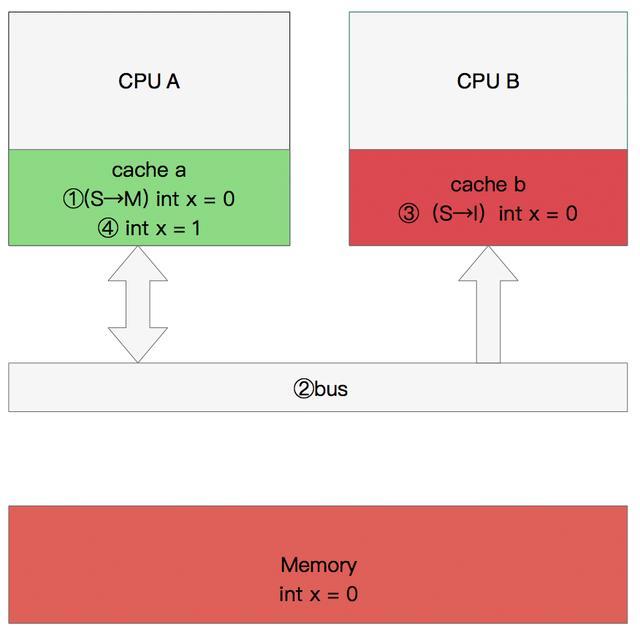

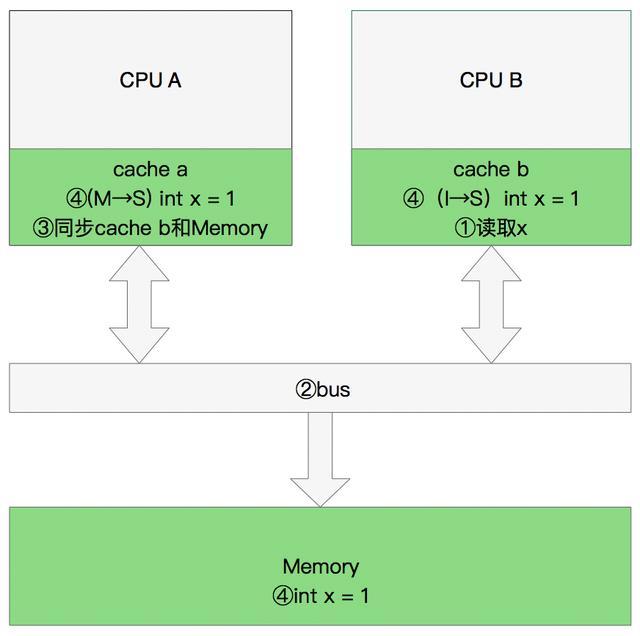

- 对于所有的收到的Invalidate请求,Invalidate Acknowlege消息必须立刻发送

- Invalidate并不真正执行,而是被放在一个特殊的队列中,在方便的时候才会去执行。

- 处理器不会发送任何消息给所处理的缓存条目,直到它处理Invalidate。

void executedOnCpu0() {

value = 10;

//在更新数据之前必须将所有存储缓存(store buffer)中的指令执行完毕。

storeMemoryBarrier();

finished = true;

}

void executedOnCpu1() {

while(!finished);

//在读取之前将所有失效队列中关于该数据的指令执行完毕。

loadMemoryBarrier();

assert value == 10;

}

一篇文章让你明白CPU缓存一致性协议MESI的更多相关文章

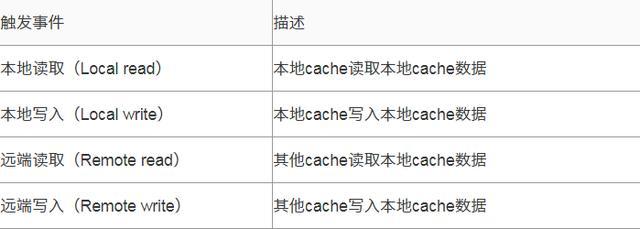

- 并发研究之CPU缓存一致性协议(MESI)

CPU缓存一致性协议MESI CPU高速缓存(Cache Memory) CPU为何要有高速缓存 CPU在摩尔定律的指导下以每18个月翻一番的速度在发展,然而内存和硬盘的发展速度远远不及CPU.这就造 ...

- C和C++中的volatile、内存屏障和CPU缓存一致性协议MESI

目录 1. 前言2 2. 结论2 3. volatile应用场景3 4. 内存屏障(Memory Barrier)4 5. setjmp和longjmp4 1) 结果1(非优化编译:g++ -g -o ...

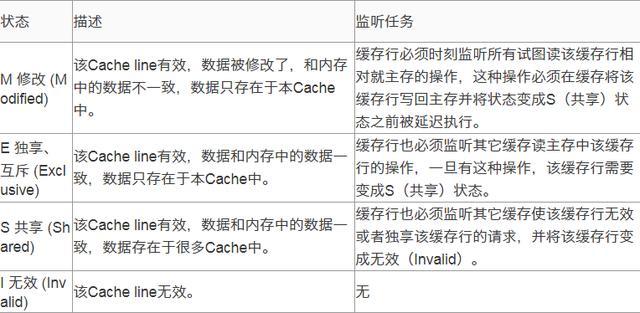

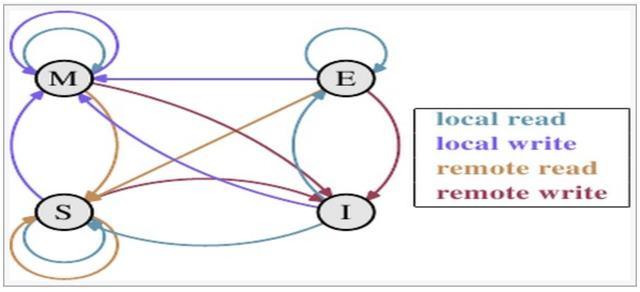

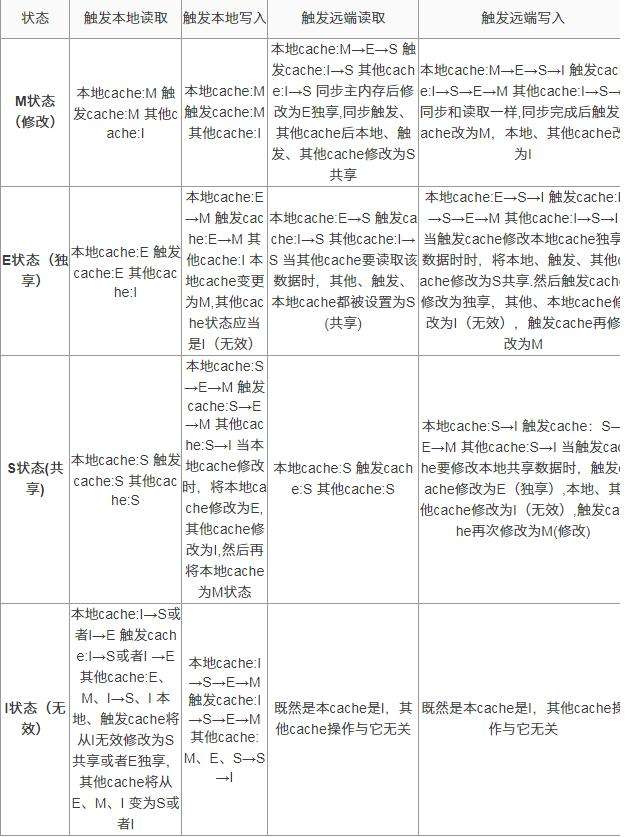

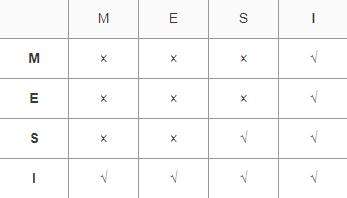

- CPU缓存一致性协议—MESI详解

MESI(也称伊利诺斯协议)是一种广泛使用的支持写回策略的缓存一致性协议,该协议被应用在Intel奔腾系列的CPU中. MESI协议中的状态 CPU中每个缓存行使用的4种状态进行标记(使用额外的两位b ...

- CPU缓存一致性协议与java中的volatile关键字

有关缓存一致性协议MESI自行百度. 提出问题:volatile在缓存一致性协议上又做了哪些事情?为啥它不保证原子性? 在缓存一致性协议下,CPU为了执行效率使用了写(存储)缓存和失效队列从而导致对用 ...

- Java内存模型(二)volatile底层实现(CPU的缓存一致性协议MESI)

CPU的缓存一致性协议MESI 在多核CPU中,内存中的数据会在多个核心中存在数据副本,某一个核心发生修改操作,就产生了数据不一致的问题,而一致性协议正是用于保证多个CPU cache之间缓存共享数据 ...

- 多线程之:MESI-CPU缓存一致性协议

MESI(Modified Exclusive Shared Or Invalid)(也称为伊利诺斯协议,是因为该协议由伊利诺斯州立大学提出)是一种广泛使用的支持写回策略的缓存一致性协议,该协议被应用 ...

- MESI-CPU缓存一致性协议

转http://blog.csdn.net/realxie/article/details/7317630 http://en.wikipedia.org/wiki/MESI_protocol MES ...

- 缓存一致性协议 mesi

m : modified e : exlusive s : shared i : invalid 四种状态的转换略过,现在讨论为什么有了这个协议,i++在多线程上还不是安全的. 两个cpu A B同时 ...

- 10 张图打开 CPU 缓存一致性的大门

前言 直接上,不多 BB 了. 正文 CPU Cache 的数据写入 随着时间的推移,CPU 和内存的访问性能相差越来越大,于是就在 CPU 内部嵌入了 CPU Cache(高速缓存),CPU Cac ...

随机推荐

- VS Code 中使用 GitHub pull request 插件提交代码

VS Code作为一个代码编辑器,受到很多人的喜爱:其中有很多非常有用的插件/扩展功能,也会极大的提高我们的工作效率. 这里介绍一下GitHub pull request,用来向GitHub提交在VS ...

- 【前端新手也能做大项目】:跟我一起,从零打造一个属于自己的在线Visio项目实战【ReactJS + UmiJS + DvaJS】(二)

本系列教程是教大家如何根据开源js绘图库,打造一个属于自己的在线绘图软件.当然,也可以看着是这个绘图库的开发教程.如果你觉得好,欢迎点个赞,让我们更有动力去做好! 本系列教程重点介绍如何开发自己的绘图 ...

- ACL2019: 《GraphRel: Modeling Text as Relational Graphs for Joint Entity and Relation Extraction》源码解析

论文地址:<GraphRel: Modeling Text as Relational Graphs for Joint Entity and Relation Extraction> G ...

- 你必须知道的容器日志 (2) 开源日志管理方案 ELK

本篇已加入<.NET Core on K8S学习实践系列文章索引>,可以点击查看更多容器化技术相关系列文章.上一篇<你必须知道的容器日志(1)>中介绍了Docker自带的log ...

- 【控制系统数字仿真与CAD】实验三:离散相似法数字仿真

一.实验目的 1. 了解离散相似法的基本原理 2. 掌握离散相似法仿真的基本过程 3. 应用离散相似法仿真非线性系统 4. MATLAB实现离散相似法的非线性系统仿真 5. 掌握SIMULINK仿真方 ...

- 《面试官之你说我听》:简明的图解Redis RDB持久化、AOF持久化

欢迎关注文章这一系列,一起学习 <提升能力,涨薪可待篇> <面试知识,工作可待篇> <实战演练,拒绝996篇> 如果此文对你有帮助.喜欢的话,那就点个赞呗,点个关注 ...

- 【NHOI2018】字符串变换

[题目描述] 给你一个全部由大小写字母组成的字符串,你每次可以将一个小写字母变换成对应的大写字母,或把一个大写字母变换成对应的小写字母.请问:至少要进行多少次变换才可以使整个字符串全部由大写字母或全部 ...

- Rust入坑指南:鳞次栉比

很久没有挖Rust的坑啦,今天来挖一些排列整齐的坑.没错,就是要介绍一些集合类型的数据类型."鳞次栉比"这个标题是不是显得很有文化? 在Rust入坑指南:常规套路一文中我们已经介绍 ...

- Rust 入门 (四)

所有权是 rust 语言独有的特性,它保证了在没有垃圾回收机制下的内存安全,所以理解 rust 的所有权是很有必要的.接下来,我们来讨论所有权和它的几个特性:借用.切片和内存结构. 什么是所有权 Ru ...

- Ansible 常见模块介绍

目录 Ansible 常见模块介绍 ping 模块 command 模块 cron 模块 user 模块 group 模块 copy 模块 file 模块 service 模块 shell 模块 sc ...