使用verilog编写锁存器与触发器

需要注意的地方有四点:

1、关于锁存器与触发器在原理上的不同点,以及代码的不同点

2、关于高电平有效与低电平有效之前的区别

3、理解实现复位与实现D触发器之间的区别

4、理解同步与异步之间的区别

锁存器代码编写

|

Module D_latch(d,clk,q); Input d; Input lck; Output reg q; always@(clk or d) if(clk) q<=d; endmodule |

D触发器,标准

|

Module D_ff(d,clk,q); Input d; Input lck; Output reg q; always@( posedge clk) q<=d; endmodule |

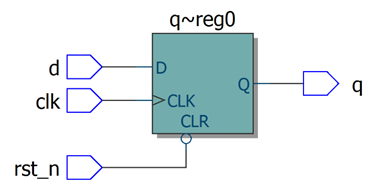

异步低有效D触发器

注意高电平有效跟低电平有效之间的区别

|

module code(clk,rst_n,d,q); input clk; input rst_n; input d; output reg q; always @( posedge clk or negedge rst_n) begin if(!rst_n) q <= 1'b0; else q <= d; end endmodule |

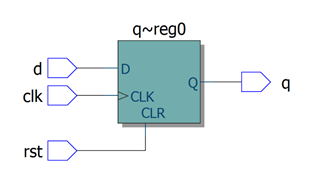

异步高有效D触发器

|

module code(clk,rst,d,q); //关于高有效还是低有效,都是驱动clk对输出端进行使能,有效 即为输 出为0,并不是输出要等于复位信号的值。 input clk; input rst; input d; output reg q; always @( posedge clk or posedge rst ) //注意这里是两个上升沿,高电平有效 begin if(rst) q <= 1'b0; else q <= d; end endmodule |

同步高有效D触发器

也就是说同步复位触发器时,必须使用触发器之外的门逻辑,才能构成同步触发器。

|

module code(clk,rst,d,q); input clk; input rst; input d; output reg q; always @( posedge clk) begin if(rst) q <= 1'b0; else q <= d; end endmodule |

使用verilog编写锁存器与触发器的更多相关文章

- Verilog中锁存器与多路选择器

Verilog中锁存器与多路选择器 Verilog是一种硬件描述语言,它代表的是硬件. Verilog代表的就是逻辑门和连接线. 对于一个always@(*)控制的块而言,只要块中的表达式包含的任意的 ...

- Verilog 编写规范

在学习Python时,作者有一句话对我影响很大.作者希望我们在学习编写程序的时候注意一些业内约定的规范.在内行人眼中,你的编写格式,就已经暴露了你的程度.学习verilog也是一样的道理,一段好的ve ...

- FPGA基础之锁存器与触发器的设计

转载:https://blog.csdn.net/lg2lh/article/details/39081061 一.锁存器 首先设计锁存器的时候应该清楚什么是锁存器,锁存器其实是对电平信号敏感的,一定 ...

- 【从零开始自制CPU之学习篇03】锁存器与触发器

本篇学习了两种锁存器:SR Latch和D Latch,一种触发器:D flip flop SR Latch:SR—锁存器 初始状态下,S和R都为0,Q和Q‘随机有一个为1另一个 为0(取决于电流速度 ...

- 关于verilog中if与case语句不完整产生锁存器的问题 分类: FPGA 2014-11-08 17:39 260人阅读 评论(0) 收藏

在很多地方都能看到,verilog中if与case语句必须完整,即if要加上else,case后要加上default语句,以防止锁存器的发生,接下来就来说说其中原因. 一,什么是锁存器?锁存器与触发器 ...

- 锁存器 Latch v.s. 触发器 Flip-Flop

转载 http://guqian110.github.io/pages/2014/09/23/latch_versus_flip_flop.html 根据 Wiki: Flip-flop (elec ...

- [FPGA]Verilog实现JK触发器组成的8421BCD码十进制计数器

目录 概述 电路分析 代码实现 参考文献 概述 本文以异步时序计数器为例,用Verilog实现以\(JK\)触发器组成的8421BCD码十进制异步计数器,并用ModelSim软件进行仿真验证. 电路分 ...

- 对Verilog 初学者比较有用的整理(转自它处)

*作者: Ian11122840 时间: 2010-9-27 09:04 ...

- 【接口时序】5、QSPI Flash的原理与QSPI时序的Verilog实现

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 4.Matlab版本:Matlab2014b/ ...

随机推荐

- 【工具】读取proprtties工具类

获取properties内容: 基本的使用看网络上大多是这样的,使用时注意线程安全以及读写的实时性问题. 1.直接通过流读取(反射): InputStream inStream = this.get ...

- Python文件中将print的输出内容重定向到变量中

有时候需要用到别人的代码, 但是又不想修改别人的文件, 想拿到输出的结果, 这时候就需要使用sys模块, 将print输出的内容重定向到变量中. Python调用sys模块中的sys.stdout, ...

- AntD使用timePiacker封装时间范围选择器(React hook版)

.katex { display: block; text-align: center; white-space: nowrap; } .katex-display > .katex > ...

- Jenkins+GitLab+Docker+SpringCloud+Kubernetes实现可持续自动化微服务

现有混合云平台的场景下,即有线下和线上的环境,又有测试与正式的场景,而且结合了Docker,导致打包内容有所区分,且服务的发布流程复杂起来,手工打包需要在编译阶段就要根据环境到处更改配置,因此纯手工发 ...

- python 实现一个计算器功能

#s = '1 - 2 * ( (60-30 +(-40/5) * (9-2*5/3 + 7 /3*99/4*2998 +10 * 568/14 )) - (-4*3)/ (16-3*2) )' #第 ...

- TCP/IP协议、三次握手、四次挥手

1.什么是TCP/IP协议 TCP/IP 是一类协议系统,它是用于网络通信的一套协议集合. 传统上来说 TCP/IP 被认为是一个四层协议 1) 网络接口层: 主要是指物理层次的一些接口,比如电缆等. ...

- SqlCommand的Parameters的用法

SqlCommand的Parameters的用法 可以用的SqlCommand的Parameters的方法SqlCommand cmd=new ("insert into notice(ly ...

- 哈工大计算机网络Week1-网络应用

目录 哈工大计算机网络Week1-网络应用 2.1网络应用的体系结构 特点 应采取什么结构 C/S结构 客户机/服务器 P2P CS vs P2P 混合结构 思考题目 2.2网络应用的基本原理 网络应 ...

- Facebook Libra - 第一笔交易

第一笔交易 假定 运行的是Linux或者macOS系统 网络连接正常 git已安装 macOS中安装了Homebrew Linux中安装了yum或者apt-get 提交一笔交易的步骤 克隆并构建Lib ...

- WinForm控件之【ListView】

基本介绍 项列表控件,拥有五种不同视图的样式供展示项集合. 常设置属性 Columns:‘详细信息’视图中用来显示的列: Groups:ListView列表中的组,将列表各项分组区域展示: Horiz ...