CRC校验原理和verilog实现方法(三)

1 代码生成

verilog实现CRC校验,可以充分发挥FPGA的硬件特性,即并行运算的能力。

具体实现方式,可以参考我上一篇博客,关键是用线性反馈移位寄存器表示出多项式,另外注意校验数据高位在先。然后根据电路结构推导出逻辑表达式,再转换成verilog就行了。

更高效的方法是利用现成的代码生成工具,例如附件的链接1,就是一种在线的CRC校验代码生成工具。

2 修改移植

我这里用代码生成工具生成多项式为x^4 + x^1 + 1,即CRC-4/ITU校验模型,校验输入数据位宽为4bit的CRC代码,并分享一下修改移植时的心得。

生成的代码如下,这个多项式和我上一篇博客举例所用多项式一样,所以生成的代码之前推导的逻辑表达式也是相同的。

function [3:0] nextCRC4_D4;

input [3:0] Data;

input [3:0] crc;

reg [3:0] d;

reg [3:0] c;

reg [3:0] newcrc;

begin

d = Data;

c = crc;

newcrc[0] = d[3] ^ d[0] ^ c[0] ^ c[3];

newcrc[1] = d[3] ^ d[1] ^ d[0] ^ c[0] ^ c[1] ^ c[3];

newcrc[2] = d[2] ^ d[1] ^ c[1] ^ c[2];

newcrc[3] = d[3] ^ d[2] ^ c[2] ^ c[3];

nextCRC4_D4 = newcrc;

end

endfunction

其实这段代码有用的只是中间那四行行为级赋值语句,可以直接拷贝到工程里使用。其中d是4位的校验数据,c是CRC寄存器。

用这段代码做CRC校验时,有几点需要明确:

1)数据位宽。

2)输入输出是否高低位反转。

3)c的初值。

4)输出是否按位取反。

其中第1点取决于通信时一帧数据的长度,第2、3点一般在常用的CRC校验模型中规定好了。这里用的CRC-4/ITU校验模型规定c的初值为0,输出不需要取反,输入输出高低位需要反转。

如果被校验数据data只有4bit,那么直接令data高低位反转后赋值d,c=0,组合逻辑输出的就是4位newcrc做高低位反转,最后得到的就是CRC校验码;

假如被校验的数据位数大于4bit,需要按字节来进行“叠加”校验。

比如数据data[15:0]=1577h,那么安照这样的校验流程:高字节低4bit(5h)反转后给d——newcrc作为下次校验的c的值——高字节高4bit(1h)反转后给d——newcrc作为下次校验的c的值——低字节低4bit(7h)反转后给d——newcrc作为下次校验的c的值——低字节高4bit(7h)反转后给d——newcrc反转后作为CRC校验码。

c的更新可以用寄存器实现。如下所示:

reg [3:0] c;

wire [3:0] d; //参与校验数据

assign d = {data_r[0], data_r[1], data_r[2], data_r[3]};//翻转数据位

assign newcrc[0] = crc_en & (d[3] ^ d[0] ^ c[0] ^ c[3]);

assign newcrc[1] = crc_en & (d[3] ^ d[1] ^ d[0] ^ c[0] ^ c[1] ^ c[3]);

assign newcrc[2] = crc_en & (d[2] ^ d[1] ^ c[1] ^ c[2]);

assign newcrc[3] = crc_en & (d[3] ^ d[2] ^ c[2] ^ c[3]);

always @(posedge clk or negedge rstn) begin

if(!rstn)

c <= 4'h0;//初始0

else begin

if(start_pos)

c <= 4'h0;

else if(crc_en)

c <= newcrc;

end

end

3 功能验证

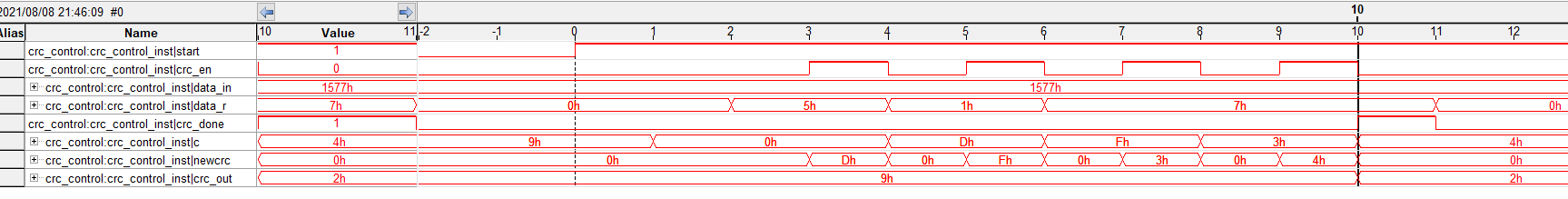

为了验证上面修改的代码功能,编写了测试代码,对16bit的数据求校验码。这里分别验证了data[15:0]=1577h和data[15:0]=4511h两个数据的CRC校验。

1)data[15:0]=1577h

在开发板上运行测试代码,用signalTAP观察结果(电脑上没有装Modelsim),其中data_in为待校验数据,经过4次计算,得到校验码为crc_out=0x2。

利用在线CRC计算工具(链接见我之前的博客),计算1577h的校验码,与测试结果一致:

2)data[15:0]=4511h

得到校验码为crc_out=0xF。

利用在线CRC计算工具(链接见我之前的博客),计算4511h的校验码,与测试结果一致:

这就说明,本文的“叠加”校验,可以实现对多字节数据的“分段”校验。多字节数据可以是4字节、16字节等,CRC校验代码中的输入数据d可以是1bit、2bit、4bit、8bit等。

不过据我的经验,要实现这种“叠加”校验,必须设置输入输出数据高低位反转,不然结果不对。也就是说如果你选的校验模型不需要数据位反转,那么只能做一次性的校验了。具体原因咱也研究不清楚,不知道有没有大神解答。

在线CRC代码生成链接:

1、https://www.easics.com/crctool/

CRC校验原理和verilog实现方法(三)的更多相关文章

- CRC校验原理和verilog实现方法(二)

1 前言 在 前面的博客 CRC校验原理和verilog实现方法(一) 中,介绍了CRC校验的原理和手动计算过程.本文说一下我在学习CRC校验FPGA实现的一点心得体会. 2 线性反馈移位寄存器 ...

- CRC校验原理和verilog实现方法(一)

1.CRC简介 CRC全称循环冗余校验(Cyclic Redundancy Check, CRC),是通信领域数据传输技术中常用的检错方法,用于保证数据传输的可靠性.网上有关这方面的博客和资料很多,本 ...

- 流水线技术原理和Verilog HDL实现(转)

源:流水线技术原理和Verilog HDL实现 所谓流水线处理,如同生产装配线一样,将操作执行工作量分成若干个时间上均衡的操作段,从流水线的起点连续地输入,流水线的各操作段以重叠方式执行.这使得操作执 ...

- 流水线技术原理和Verilog HDL实现

所谓流水线处理,如同生产装配线一样,将操作执行工作量分成若干个时间上均衡的操作段,从流水线的起点连续地输入,流水线的各操作段以重叠方式执行.这使得操作执行速度只与流水线输入的速度有关,而与处理所需的时 ...

- golang中浮点型底层存储原理和decimal使用方法

var price float32 = 39.29 float64和float32类似,只是用于表示各部分的位数不同而已,其中:sign=1位,exponent=11位,fraction=52位,也就 ...

- Verilog语言实现并行(循环冗余码)CRC校验

1 前言 (1) 什么是CRC校验? CRC即循环冗余校验码:是数据通信领域中最常用的一种查错校验码,其特征是信息字段和校验字段的长度可以任意选定.循环冗余检查(CRC)是一种数据传输检错功能, ...

- 用C#实现的几种常用数据校验方法整理(CRC校验;LRC校验;BCC校验;累加和校验)

CRC即循环冗余校验码(Cyclic Redundancy Check):是数据通信领域中最常用的一种查错校验码,其特征是信息字段和校验字段的长度可以任意选定.循环冗余检查(CRC)是一种数据传输检错 ...

- 常用校验码(奇偶校验码、海明校验码、CRC校验码)

一.奇偶校验码 二.海明校验码 三.CRC校验码 计算机系统运行时,各个部之间要进行数据交换.交换的过程中,会有发生误码的可能(即0变成1或1变成0),由于计算机的储存是通过二进制代码来实现的的, ...

- CRC校验的C语言实现

文章转自 循环冗余校验(CRC)算法入门引导 - Ivan 的专栏 - 博客频道 - CSDN.NET http://blog.csdn.net/liyuanbhu/article/details/7 ...

随机推荐

- 20204107 孙嘉临《Python程序设计》实验一报告

课程:<python程序设计> 班级:2041 姓名:孙嘉临 学号:20204107 实验教师:王志强 实验日期:2021年4月12日 必修/选修:公选课 ##一.实验内容 1.熟悉Pyt ...

- QGIS如何打开ArcGIS创建的GDB数据库文件

引言 QGIS作为一种开源的地理信息处理软件由于其界面友好.渲染速度快.开源免费等特性而获得业内很多人士的青睐,然而在实际的生产和处理过程中,GIS数据往往存储在ArcGIS的文件地理数据库(Geod ...

- Gerrit+replication 同步Gitlab

配置环境:gerrit 192.168.1.100gitlab 192.168.1.1011.创建秘钥 [root@gerrit ~]# ssh-keygen -m PEM -t rsa 2.添加ho ...

- 一QT获取当前时间和日期

获取日期和时间使用QDateTime类,该类中有一个静态成员函数可以返回当前的时间信息 我们可以直接调用这个静态函数获取当前时间 QDateTime time = QDateTime::current ...

- 27、Tomcat服务的安装与配置

服务器名称 ip地址 slave-node1 172.16.1.91 27.1. Tomcat简介: Tomcat是Apache软件基金会(Apache Software Foundation)的Ja ...

- SpringBoot Cache 深入

这上一篇文章中我们熟悉了SpringBoot Cache的基本使用,接下来我们看下它的执行流程 CacheAutoConfiguration 自动装配类 根据图中标注,看到它引用了CachingCon ...

- 谁知道百会CRM跟Zoho是一家公司吗?

说到ZohoCRM,无论是搜索引擎还是信息网站,总会有无数的身影.很多人不知道这两家公司的关系,甚至认为百会和Zoho是一家公司.那么,百会CRM和Zoho属于同一类公司吗?它们之间有什么关系?今天小 ...

- 【转载】CentOS-yum安装Nginx

查看系统版本 $ cat /etc/redhat-release Nginx 不在默认的 yum 源中,使用官网的 yum 源 $ rpm -ivh http://nginx.org/packages ...

- Html:行级元素和块级元素标签列表

块级元素 div p h1-h6 form ul ol dl dt dd li table tr td th hr blockquote address table menu pre HTML5: h ...

- Shell常用工具find,grep,sed,awk,xargs命令

最近学习shell命令,对grep,sed,awk命令有点混乱,故小结一下,巩固一遍. 注意:find , grep , sed, awk可使用基本正则表达式字符,find,grep,awk也支持扩展 ...