FPGA CFGBVS 管脚接法

说明

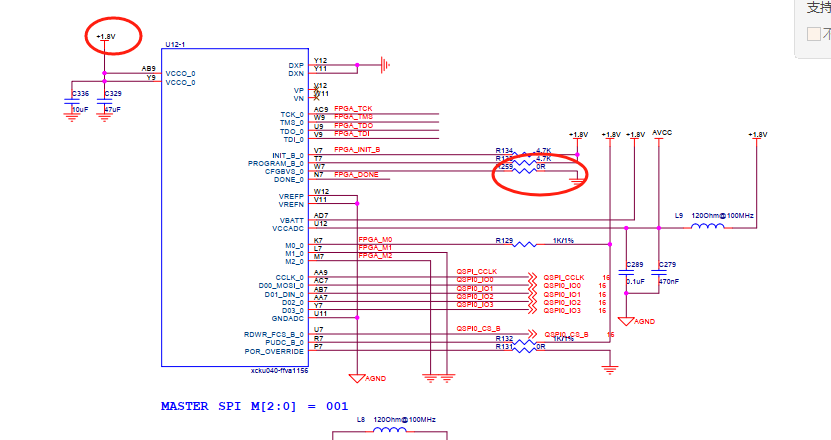

新设计了1个KU040 FPGA板子,回来之后接上JTAG FPGA不识别。做如下检查:

1、电源测试点均正常;

2、查看贴片是否有漏焊,检查无异常,设计上NC的才NC;

3、反复检查JTAG接线是否异常,贴片是否异常;

上述检查均无问题,开始查看原理图,逐个对照XILINX手册进行研究。

其中发现 CFGBVS 在设计图中接了地,对照XILINX 手册 https://www.amd.com/content/dam/xilinx/support/documents/user_guides/ug570-ultrascale-configuration.pdf

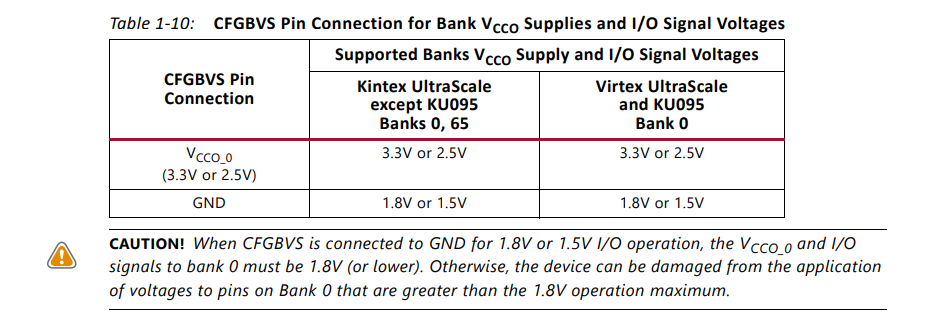

In the Kintex UltraScale and Virtex UltraScale FPGAs, the configuration banks voltage select

(CFGBVS) pin must be set to High or Low to determine the I/O voltage support for the pins

in bank 0, and for the multi-function pins in bank 65 when they are used during

configuration. The CFGBVS is a logic input pin referenced between VCCO_0 and GND. When

the CFGBVS pin is connected to the VCCO_0 supply of 3.3V or 2.5V, the configuration I/O

support operation at 3.3V or 2.5V. When the CFGBVS pin is connected to GND, the

configuration I/O support operation at 1.8V or 1.5V. There is no CFGBVS pin in the Artix

UltraScale+, Kintex UltraScale+, and Virtex UltraScale+ FPGAs because their configuration

I/O only support operation at 1.8V or 1.5V.

Configuration is not supported below the minimum recommended operating voltage for

1.5V as specified in the data sheet. The CFGBVS pin setting determines the I/O voltage

support for bank 0 at all times, before, during, and after configuration. CFGBVS similarly

controls the voltage tolerance on bank 65, but only during configuration.

也就是说,这里原理图 CFGBVS 接地肯定是不对的,必须拉高到3.3V,还好留了1个0欧姆电阻在这里 还可以飞线补救一下。

FPGA CFGBVS 管脚接法的更多相关文章

- Quartus II中FPGA的管脚分配保存方法

一.摘要 将Quartus II中FPGA管脚的分配及保存方法做一个汇总. 二.管脚分配方法 FPGA 的管脚分配,除了在QII软件中,选择“Assignments ->Pin”标签(或者点击按 ...

- (转载)Quartus II中FPGA的管脚分配保存方法(Quartus II)

一.摘要 将Quartus II中FPGA管脚的分配及保存方法做一个汇总. 二.管脚分配方法 FPGA 的管脚分配,除了在QII软件中,选择"Assignments ->Pin&quo ...

- 4.FPGA芯片管脚解释

用户I/O:不用解释了. 配置管脚: MSEL[1:0] 用于选择配置模式,比如AS.PS等. DATA0 FPGA串行数据输入,连接到配置器件的串行数据输出管脚. DCLK FPGA串行时钟输出 ...

- quartus2中FPGA管脚分配保存方法(转)

一.摘要 将Quartus II中FPGA管脚的分配及保存方法做一个汇总. 二.管脚分配方法 FPGA 的管脚分配,除了在QII软件中,选择“Assignments ->Pin”标签(或者点击按 ...

- FPGA研发之道(25)-管脚

管脚是FPGA重要的资源之一,FPGA的管脚分别包括,电源管脚,普通I/O,配置管脚,时钟专用输入管脚GCLK等. 本文引用地址:http://www.eepw.com.cn/article/2664 ...

- FPGA Timing笔记

很多FPGA工程师都会遇到timing的问题,如何让FPGA跑到更快的处理频率是永久话题.决定FPGA的timing关键是什么?如何才能跑到更快的频率呢? A. 第一步需要了解FPGA的timing路 ...

- 【小梅哥FPGA进阶学习之旅】基于Altera FPGA 的DDR2+千兆以太网电路设计

DDR2电路设计 在高速大数据的应用中,高速大容量缓存是必不可少的硬件.当前在FPGA系统中使用较为广泛的高速大容量存储器有经典速度较低的单数据速率的SDRAM存储器,以及速度较高的双速率DDR.DD ...

- 第一个FPGA工程—LED流水灯

这一章我们来实现第一个FPGA工程-LED流水灯.我们将通过流水灯例程向大家介绍一次完整的FPGA开发流程,从新建工程,代码设计,综合实现,管脚约束,下载FPGA程序.掌握本章内容,大家就算正式的开始 ...

- 如何新建Quartus工程—FPGA入门教程【钛白Logic】

这一章我们来实现第一个FPGA工程—LED流水灯.我们将通过流水灯例程向大家介绍一次完整的FPGA开发流程,从新建工程,代码设计,综合实现,管脚约束,下载FPGA程序.掌握本章内容,大家就算正式的开始 ...

- FPGA与图像处理

用FPGA做图像处理最关键的一点优势就是:FPGA能进行实时流水线运算,能达到最高的实时性.因此在一些对实时性要求非常高的应用领域,做图像处理基本就只能用FPGA.例如在一些分选设备中图像处理基本上用 ...

随机推荐

- Python基础篇(安装)

Python简介 Python是Guido van Rossum发布于1991年的一种计算机程序设计语言.是一种动态的.面向对象的脚本语言,是一种解释型的,弱类型的高级计算机语言.需要注意的是pyth ...

- Windows 11提示“无法枚举容器中的对象。”

*为什么会出现这一错误提示?* 在Windows系统当中,对文件或文件夹的权限进行设置可以有效地保护隐私内容.登录管理员账户可以对权限进行更改,并且有权决定是否将内容共享给多个用户使用.但是在某些情况 ...

- Python 潮流周刊#53:我辈楷模,一个约见诺奖得主,一个成为核心开发者

本周刊由 Python猫 出品,精心筛选国内外的 250+ 信息源,为你挑选最值得分享的文章.教程.开源项目.软件工具.播客和视频.热门话题等内容.愿景:帮助所有读者精进 Python 技术,并增长职 ...

- 基于WebSocket的modbus通信(三)- websocket和串口

WebSocket传递ModbusTCP数据包 错误纠正 上一篇还有个错误,就是客户端写数据时服务端不需要响应,但我的服务端响应了的.我选择改客户端,把写数据时接收到的响应丢弃. PrintBytes ...

- sort awk 文本处理命令

sort: 1.将文件的每一行作为一个单位,相互比较 2.默认升序 3.以字符来进行对比,从首字符开始往后,依次按ASCII码值排序 sort 显示文件内容 (类似cat) 选项: -u 去掉重复行 ...

- php基本语法与安装

// 什么是PHP // PHP 是 后端语言的一种 // 主要作用就是实现数据交互 // ...

- kettle从入门到精通 第五十六课 ETL之kettle Microsoft Excel Output

1.9.4 版本的kettle中有两个Excel输出,Excel输出和Microsoft Excel输出.前者只支持xls格式,后者支持xls和xlsx两种格式,本节课主要讲解步骤Microsoft ...

- JavaScript模块化笔记

JavaScript模块化笔记 一个模块就是一堆被封装到一个文件当中的代码,并使用export暴露部分代码给其他的文件.模块专注于一小部分功能并与应用的其他部分松耦合,这是因为模块间没有全局变量或共享 ...

- disabled 和 readonly 都是 HTML 表单元素的属性,它们有一些相同点和不同点。

disabled 和 readonly 都是 HTML 表单元素的属性,它们有一些相同点和不同点. 相同点: disabled 和 readonly 属性都可以用于表单中的输入框.文本域等元素,用于控 ...

- 图片预加载需要token认证的地址处理

1.添加函数修改img的属性: /** * * @param {*} idName 传入的id,获取改img的dom,添加相应的数学 */ export const proxyImg = (idNam ...