移位寄存器的设计(VHDL)及testbench的编写

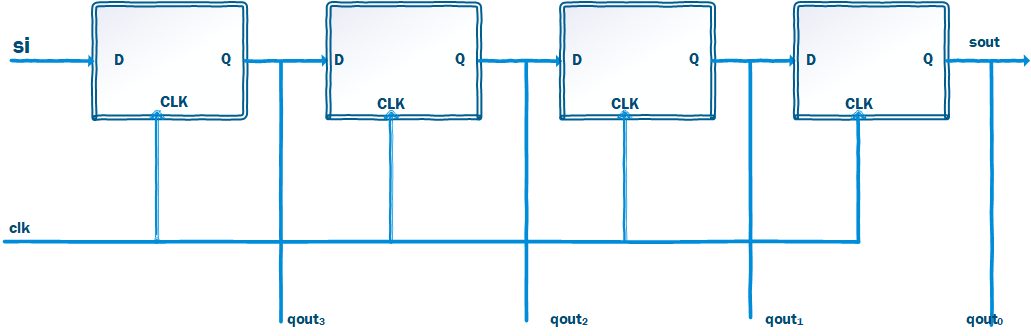

移位寄存器是一种常用的存储元件,此处由D触发器构成,如下图所示。

当时钟边沿到来时,存储在移位寄存器的数据朝一个方向移动一个BIT位。

移位寄存器的功能主要为:串并转换,并串转换和同步延迟。

vhdl代码如下:

1 library ieee;

2 use ieee.std_logic_1164.all;

3

4 entity shiftreg_rb is --实体说明及端口说明

5 port(

6 si,clr_bar,clk:in std_logic;

7 qout:buffer std_logic_vector(3 downto 0)--由于qout端口既是当前D触发器的输入也是上一个D触发器的输出。

8 ); --即qout信号是被驱动源驱动的同时还要驱动下一个端口。

9 end entity shiftreg_rb; --此情况下要使用buffer模式的端口。

10

11 architecture behavior of shiftreg_rb is

12 begin

13 process (clk) ---当时钟发生变化(上升沿或下降沿发生),执行进程

14 begin

15 if clk='1' then --时钟上升沿触发

16 if clr_bar = '0' then --时钟使能

17 qout <= "0000";

18 else

19 qout(0) <=qout(1);--数据左移

20 qout(1) <=qout(2);

21 qout(2) <=qout(3);

22 qout(3) <=si;

23 end if;

24 end if;

25 end process;

26 end behavior;

Testbench编写:

1 LIBRARY IEEE;

2 USE IEEE.std_logic_1164.all;

3 USE IEEE.NUMERIC_STD.ALL;

4 USE IEEE.MATH_REAL.ALL;

5 USE IEEE.STD_LOGIC_UNSIGNED.ALL;

6 USE IEEE.STD_LOGIC_ARITH.ALL;--因为将INTEGER型数据转换成STD_LOGIC_VECTOR需要使用CONV_STD_LOGIC_VECTOR命令。

7 --而此命令在IEEE.STD_LOGIC_ARITH.ALL中。

8

9 ENTITY shiftreg_tb IS --testbench实体声明,由于testbench位最高层模块,因此无输入输出端口。

10 END shiftreg_tb;

11

12 ARCHITECTURE testbench OF shiftreg_tb IS

13 COMPONENT shiftreg_rb IS --例化子模块(元件)前,需进行子模块(元件)声明

14 port(

15 si,clr_bar,clk:in std_logic;

16 qout:buffer std_logic_vector(3 downto 0)

17 );

18 END COMPONENT;

19 SIGNAL si,clk:STD_LOGIC; --信号声明,为元件例化时所用

20 SIGNAL clr_bar:STD_LOGIC:='1'; --信号声明,为元件例化时所用

21 SIGNAL qout:STD_LOGIC_VECTOR(3 downto 0);

22 SIGNAL temp1:INTEGER range 0 to 15; --将产生的伪随机数转化为整数型数值temp1

23 SIGNAL temp2:STD_LOGIC_VECTOR(3 DOWNTO 0); --将temp1转化逻辑位矢量temp2

24 SIGNAL count1:STD_LOGIC_VECTOR (0 to 3):="0100";--计数信号

25 CONSTANT clk_period :time:=50 ns; --时钟信号

26

27

28 BEGIN

29 U_shiftreg_rb:shiftreg_rb PORT MAP( --UUT(被测元件shiftreg_rb)的例化

30 si=>si,

31 clr_bar=>clr_bar,

32 clk=>clk,

33 qout=>qout

34 );

35

36 PROCESS

37 VARIABLE seed1,seed2:POSITIVE; --伪随机数生成格式 种子seed1,seed2位positive型的,默认位1,改变种子的值会生成不同的随机数

38 VARIABLE rand:REAL; --伪随机数生成格式 rand必须为real型数值

39 BEGIN

40 IF count1="0100" THEN --每个200ns产生一次随机数

41 UNIFORM(seed1,seed2,rand);

42 temp1 <= INTEGER(TRUNC(rand*15.0)); --生成的随机数范围在0~15,且把生成的实数型随机数转化为整型。

43 temp2 <=CONV_STD_LOGIC_VECTOR(temp1,4);--由于没找到直接将整数型转化为标准逻辑型(STD_LOGIC)的命令,所以先将整型随机数转化为标准逻辑矢量型

44 --** 此处要注意,要实现移位寄存器的并转串模式,不能将随机数信号直接加再qout上,因为buffer型端口的驱动源只来自其内部。

45 --** 不过可以将qout改成inout类型试试,不过目前没成功。还一种方法是将多位信号分别加在D触发器的输入端口,这种方法肯定可行。

46

47 si <= temp2(0); --再将temp2的最低位赋值给移位寄存器的输入si,这样也可以产生一个随机的输入信号si。

48 count1 <= "0000";

49 END IF;

50 WAIT FOR(clk_period/2); --使clk时钟信号周期为25ns

51 clk <= '1';

52 count1<= count1 +'1';

53 WAIT FOR(clk_period/2);

54 clk <= '0';

55

56 END PROCESS;

57 END testbench;

自动仿真.do文件的编写

quit -sim #退出仿真

.main clear #清空命令框 vlib ./lib #在.do文件所在目录创建名为lib的文件夹

vlib ./lib/work #在lib文件夹里创建名为work的文件夹

vmap work ./lib/work #将物理文件地址./lib/work映射到逻辑工作库work vcom -work work ./shiftreg_tb.vhd #编译vhdl文件,且将编译结果放在逻辑库work中

vcom -work work ./../design/*.vhd #编译vhdl文件,且将编译结果放在逻辑库work中 vsim -voptargs=+acc work.shiftreg_tb #不带优化的启动modelsim仿真 add wave -divider {shiftreg_tb} #添加测试列表名

add wave shiftreg_tb/clk #添加待测信号

add wave shiftreg_tb/si

add wave shiftreg_tb/clr_bar

add wave shiftreg_tb/count1

add wave shiftreg_tb/temp1

add wave shiftreg_tb/temp2

add wave shiftreg_tb/qout

add wave -divider {U_shiftreg_tb}

add wave shiftreg_tb/U_shiftreg_rb/* run 1us #仿真运行1us

编写好自动测试文件后,将其与测试平台shiftreg_tb.vhd文件放在一个文件名sim下。

打开modelsim,输入命令 do run.do

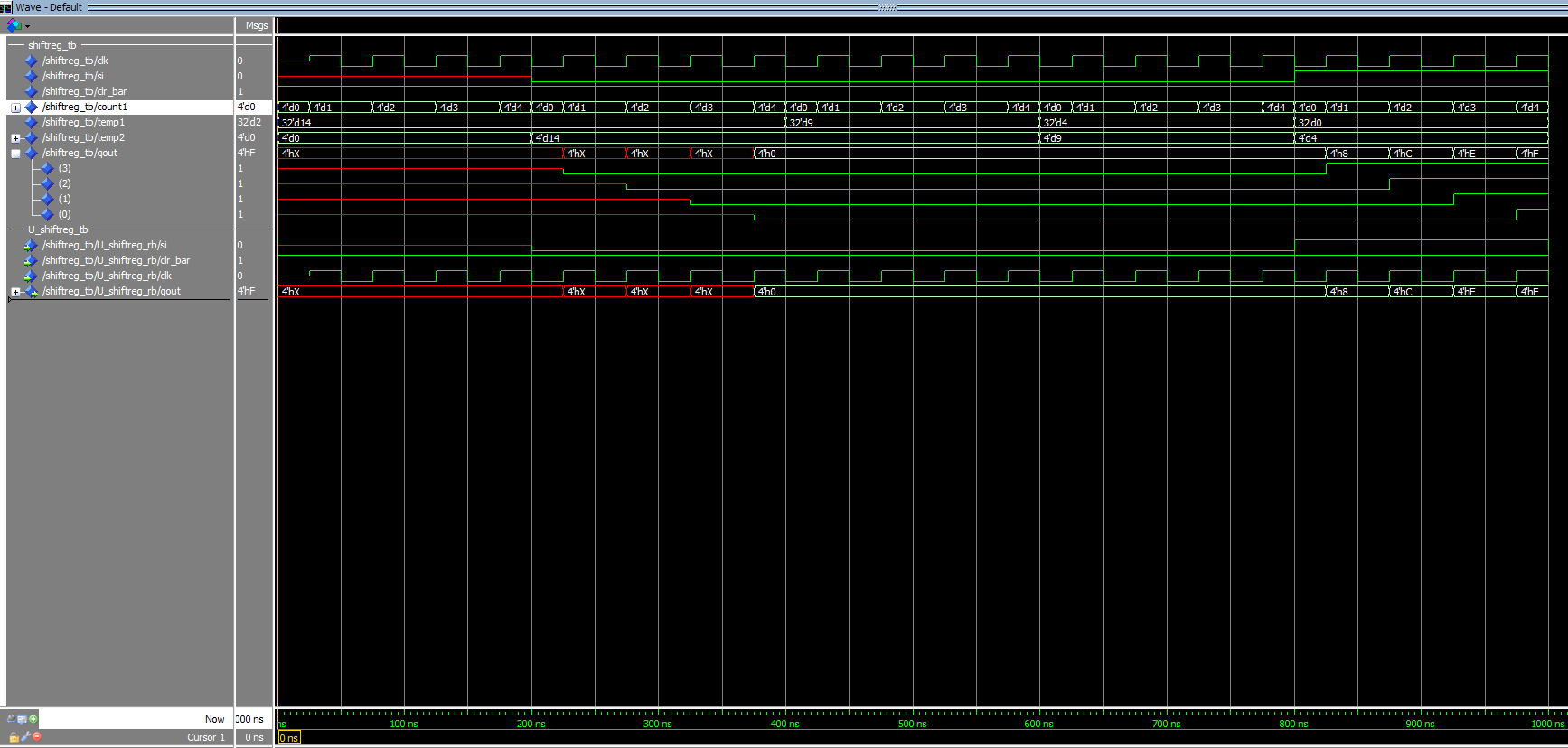

仿真结果如下:

移位寄存器的设计(VHDL)及testbench的编写的更多相关文章

- VHDL的testbench的编写(转)

大多数硬件设计人员对verilog的testbench比较熟悉,那是因为verilog被设计出来的目的就是为了用于测试使用,也正是因为这样verilog的语法规则才被设计得更像C语言,而verilog ...

- Testbench的编写

Testbench的作用,在于给我们编写的可综合代码的模块送入激励.即在我们波形仿真中用编写testbench来代替拖拽波形.其中还包括了我们硬件仿真与matlab仿真的联调建立(将matlab产生的 ...

- Testbench文件编写纪要(Verilog)

之前在使用Verilog做FPGA项目中.以及其他一些不同的场合下,零散的写过一些练手性质的testbench文件,开始几次写的时候,每次都会因为一些基本的东西没记住.写的很不熟练,后面写的时候稍微熟 ...

- JavaScript网站设计实践(四)编写about.html页面,利用JavaScript和DOM,选择性的显示和隐藏DIV元素

一.现在我们在网站设计(三)的基础上,来编写about.html页面. 这个页面要用到的知识点是利用JavaScript和DOM实现选择性地显示和隐藏某些DIV about.html页面在前面我们为了 ...

- SSM实战——秒杀系统之DAO层实体定义、接口设计、mybatis映射文件编写、整合Spring与Mybatis

一:DAO实体编码 1:首先,在src目录下,新建org.myseckill.entity包,用于存放实体类: 2:实体类设计 根据前面创建的数据库表以及映射关系,创建实体类. 表一:秒杀商品表 对应 ...

- 设计一个JavaScript框架需要编写哪些模块

在这个js框架随处乱跑的时代,你是否考虑过写一个自己的框架?下面的内容也许会有点帮助. 一个框架应该包含哪些内容? 1. 语言扩展 大部分现有的框架都提供了这部分内容,语言扩展应当是以ECMAScri ...

- JavaScript网站设计实践(六)编写live.html页面 改进表格显示

一.编写live.html页面,1.JavaScript实现表格的隔行换色,并且当鼠标移过时当前行高亮显示:2.是输出表格中的abbr标签的内容 实现后的效果图是这样的: 1.实现思路 在输出表格的时 ...

- JavaScript网站设计实践(五)编写photos.html页面,实现点击缩略图显示大图的效果

一.photos.html页面,点击每一张缩略图,就在占位符的位置那里,显示对应的大图. 看到的页面效果是这样的: 1.实现思路 这个功能在之前的JavaScript美术馆那里已经实现了. 首先在页面 ...

- JavaScript网站设计实践(七)编写最后一个页面 改进表单

一.最后一个页面 contact.html.改进表单 在该页面实现的功能: 几乎所有的网站都会有表单填写,对于用户输入和填写的数据,首先我们一般现在前台验证,然后再去后台验证. 在前台最简单的验证:检 ...

- Android实训案例(四)——关于Game,2048方块的设计,逻辑,实现,编写,加上色彩,分数等深度剖析开发过程!

Android实训案例(四)--关于Game,2048方块的设计,逻辑,实现,编写,加上色彩,分数等深度剖析开发过程! 关于2048,我看到很多大神,比如医生,郭神,所以我也研究了一段时间,还好是研究 ...

随机推荐

- C# 用树形列表 动态 显示菜单

如图 页面加载 private void Form1_Load(object sender, EventArgs e) { GetMenu(treeView1, menuStrip1);//将menu ...

- C# WPF 简单自定义菜单切换动画

微信公众号:Dotnet9,网站:Dotnet9,问题或建议,请网站留言: 如果您觉得Dotnet9对您有帮助,欢迎赞赏 C# WPF 简单自定义菜单切换动画 内容目录 实现效果 业务场景 编码实现 ...

- 【面试题精讲】如何使用Stream的聚合功能

有的时候博客内容会有变动,首发博客是最新的,其他博客地址可能会未同步,认准https://blog.zysicyj.top 首发博客地址 系列文章地址 求和(Sum): List<Integer ...

- [转帖]etcd raft模块解析

https://www.cnblogs.com/luohaixian/p/16641100.html 1. Raft简介 raft是一个管理复制式日志的共识算法,它是通过复制日志的方式来保持状态机里的 ...

- [转帖]Linux运维常用150个命令

Linux运维常用150个命令 转载自:www.cnblogs.com/bananaaa/p/7774467.html 命令 功能说明 线上查询及帮助命令(2个) man 查看命令帮助,命令的词典,更 ...

- [转帖]Linux中awk命令正确的求最大值、最小值、平均值、总和

https://blog.csdn.net/fireblue1990/article/details/51622416 test.txt文件内容: 9 11 35 21 42 118 求最大值: aw ...

- vCenter 宕机后证书续期处理

vCenter 宕机后证书续期处理 背景 最近护网, 我司被选中作为防守方 因为发现一个vCenter控制台出现异常访问, 被管理员强行断网. 因为是周六的事情,当时自己也没太在意,想着工作日添加网络 ...

- [转帖]shell命令替换~date用法~如果被替换命令的输出内容包括多行或有多个连续的空白符,输出变量时应该将变量用双引号包围

https://www.cnblogs.com/mianbaoshu/p/12069458.html Shell 命令替换是指将命令的输出结果赋值给某个变量.比如,将使用ls命令查看到的某个目录中的内 ...

- [转帖]漏洞预警|Apache Tomcat 信息泄露漏洞

http://www.hackdig.com/03/hack-953615.htm 棱镜七彩安全预警 近日网上有关于开源项目Apache Tomcat 信息泄露漏洞,棱镜七彩威胁情报团队第一时间探测到 ...

- /dev/null 先后顺序的问题

https://blog.csdn.net/x1131230123/article/details/114317752