USB2.0学习笔记连载(五):EZ-USB重要寄存器的配置

本篇博客主要讲解EZ-USB一些重要寄存器的配置,首先对于本篇博客所讲的内容,读者应该到官网上去下载相关的手册,其中包括《EZ-USB Technical Reference Manual》,《Dvk Users Guide》,《CY7C68013A中英文数据手册》,此外还应去Cypress官网下载一个应用笔记,如下图所示:

上面资料中《EZ-USB Technical Reference Manual》包含了需要配置的寄存器信息和一些配置信息,比较重要。《CY7C68013A中英文数据手册》讲解了CY7C68013的一些电气特性以及一些参数信息比较重要。《Dvk Users Guide》介绍了官网提供的例程如何调试以及硬件如何被PC机识别等关键信息,比较重要。《AN61345》介绍了FPGA和FX2LP使用Slave FIFO模式下的配置和调试信息,比较重要。

上面资料中《EZ-USB Technical Reference Manual》包含了需要配置的寄存器信息和一些配置信息,比较重要。《CY7C68013A中英文数据手册》讲解了CY7C68013的一些电气特性以及一些参数信息比较重要。《Dvk Users Guide》介绍了官网提供的例程如何调试以及硬件如何被PC机识别等关键信息,比较重要。《AN61345》介绍了FPGA和FX2LP使用Slave FIFO模式下的配置和调试信息,比较重要。

有了上述手册之后,我们首先打开《AN61345》里面所讲的内容,这篇笔记里面介绍了使用USB CY7C68013的slave FIFO模式应该如何去配置。

上图是典型的FX2LP和FPGA的通信示意图,对于GPIF接口而言,是让FX2LP芯片作为主设备,提供给外部设备所需要的驱动信号,而Slave FIFO模式是FX2LP作为从设备,负责数据的传输,而外部设备是主设备,负责传感器的驱动以及数据的产生。所以我们采用的方案架构是Slave FIFO模式,让FPGA作为主设备。

上面两个图是FPGA 和FX2LP芯片进行通信所需要的信号,之前笔者以及提及过了,这里不再赘述。

对于USB的传输方式,主要包括中断(interrupt),块传输(bulk),同步(Isochronous),控制(control),其中bulk传输比较重要,比较常用,所以必须要掌握。

打开 《Dvk Users Guide》后,在12页给出了USB 主函数框架的示意图,如上图所示。首先上电之后,初始化各状态变量,然后对各变量进行初始化赋值。再使能中断。

那么对于上电复位之后,需要初始化一些寄存器,在《AN61345》中的第8页已经给出了一些提示。

关于相关寄存器的具体说明,可以查看手册《EZ-USB Technical Reference Manual》。所有寄存器的配置也是完成CY7C68013内部结构所需要的配置,如下图所示。

1.8051内核工作寄存器 CPUCS(page338)

CPUCS = 0x12; //48MHZ CLKOUT ENALBE,时钟不反向,CLKOUT PIN驱动,有时钟输出;

2.IFCLK引脚的相关配置 IFCONFIG(page339)

IFCONFIG =0x03; //选择为外部时钟,且时钟频率为30MHz,且为同步slaveFIFO模式,输入IFCLK(5~48MHz)(0000_0011)。

3.FIFO深度控制及数量和方向选择 EPXFG深度配置(page352)

选择FIFO的数量以及FIFO的深度为512,位宽为8位;由于笔者设计的板卡中只用到了FIFO2,也就是EP2,深度为512 ,位宽为8位。其他FIFO暂时用不到。

EP2CFG = 0xE0; // disabled...

EP4CFG = 0x60; // disabled...

EP6CFG = 0x60; // disabled...

EP8CFG = 0x60; // disabled...

4.FIFO位宽设置 EPXFIFOCFG深度配置(page353)

RAW,Gray 模式的数据位输出为8bit。

EP2FIFOCFG = 0x08; // autoin, 8 Bit Wide

5.USB终端输出方式选择EP1IN/OUTCFG终端配置(page350)

在设置USB的传输方式,选择默认值bulk传输方式。

EP1OUTCFG = 0xA0; // default values

EP1INCFG = 0xA0; // default values

6.芯片版本控制 REVCTL(page348)

采用系统默认的值。

REVCTL = 0x03; //Cypress highly recommends setting both bits to 1

7.FIFO输出状态控制 PINFLAGAB/CD(page342)

PINFLAGSAB = 0x00;

PINFLAGSCD = 0x00;

由外部的FIFOADR[1:0]来决定使用哪一个FIFO。

8.FIFO复位 FIFORESET(page342)

手册上面的要求如下图所示:

//复位FIFO,先复位端点,再清空端点

延时;

FIFORESET = 0x80;// activate NAK-ALL to avoid race conditions

延时;

FIFORESET = 0x02;// reset, FIFO 2

延时;

FIFORESET = 0x04;// reset, FIFO 4

延时;

FIFORESET = 0x06;// reset, FIFO 6

延时;

FIFORESET = 0x08;// reset, FIFO 8

延时;

FIFORESET = 0x00;// deactivate NAK-AL

延时;

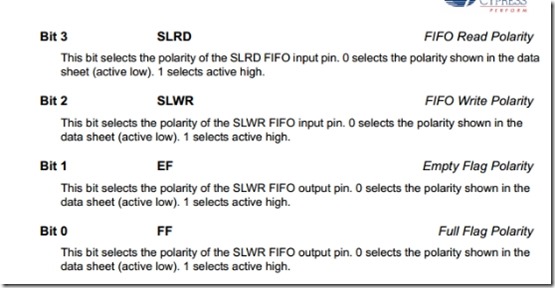

9.FIFO引脚极性判断 FIFOPINPOLAR(page346)

在硬件设计中,将SLRD直接拉高处理;PKEND也直接拉高,不做包处理;

FIFOPINPOLAR = 0x04; //BIT[5:0] = {PKTEND, SLOE, SLRD, SLWR, EMPTY, FULL}

//Set SLWR High Valid; PKTEND,SLOE,SLRD EMPTY, FULL Low Active

10.引脚复用可选IO功能 PORTACFG(page382)

其中在A区的引脚复用了片选SLCS信号,所以要将其设置为1;

PORTACFG |= 0x40; //IFCOG[1:0] = 11(Slave FIFO Mode), Set PORTACFG[6] to USE PA7-SLCS

11.特殊功能寄存器 自动指针设置AUTOPTRSETUP (page332)

//Set Autopointer, enable dual autopointer

AUTOPTRSETUP |= 0x01;

12.设置自动报传 EPXAUTOINLENH/L

//设置为Autoin时的自动传输包大小

EP2AUTOINLENH = 0x02; // EZ-USB automatically commits data in 512-byte chunks

// EP2AUTOINLENH = 0x04; // EZ-USB automatically commits data in 1024-byte chunks

EP2AUTOINLENL = 0x00;

笔者设计的USB部分如上图所示,由于FPGA引脚有限,采用8bit数据总线传输,USB部分只做写入功能,所以预留USB_WR引脚,同步时钟USB_IFCLK,SLRD,PKEND直接拉高,SLCS拉低,FIFOADR[1:0] = 00,选择FIFO中的EP2,增加USB触发信号引脚,作为FPGA写入使能信号,增加CMOS_VSYNC帧同步信号,作为CMOS视频的同步信号。

USB2.0学习笔记连载(五):EZ-USB重要寄存器的配置的更多相关文章

- USB2.0学习笔记连载(三):通用USB驱动程序解析

对于USB驱动的开发,读者可以使用Windows DDK.DriverStudio等多种开发工具来实现USB的驱动,但是驱动程序的开发过程都比较复杂,而且很容易致使USB主机内存泄露而死机.那么对于笔 ...

- USB2.0学习笔记连载(二):USB基础知识简介

USB接口分为USB A型.USB B型.USBmini型.USBmicro型.USB3.0其中每种都有相应的插座和插头. 图1 图2 上图是USBA型接口,图1为插座,图2为插头.插座指向下行方向, ...

- USB2.0学习笔记连载(一):CY7C68013特性简介

上一篇博客已经给出了整个视频板卡架构,那么对于USB接口部分需要着重理解和学习. 对于目前来说,若是利用FPGA去模拟USB2.0内核,难度还是挺大的,整个状态的收发都不好控制.现在目前都在使用桥接芯 ...

- USB2.0学习笔记连载(十九):EZ-USB TRM手册重要部分介绍

TRM手册中给出了所有的寄存器配置,在 slave fifo模式或者 GPIF模式等,所以对于用到的各种寄存器配置需要查看此手册,当然还可以配合着应用手册<AN61345>. ...

- USB2.0学习笔记连载(十七):keil实现寄存器的配置及相关函数讲解(一)

首先要实现对寄存器的配置,可以参考手册<Development kit User Guide>,如下图所示: 此文件包含在 文件中.上述的应用文档详细介绍了如何利用KEIL实现对固件程序 ...

- USB2.0学习笔记连载(六):USB2.0硬件设计需要注意事项

笔者在设计USB2.0时找到了一个官方给的硬件设计正确设计指南,其中有些内容还挺nice的.不单单只是USB的设计,其中有些思想可以应用到其他的场合中. 对于USB2.0而言,全速状态下可以达到480 ...

- USB2.0学习笔记连载(十八):keil实现寄存器的配置及相关函数讲解(二)

其实之前也有提及过,Cypress公司提供的官方文件和应用手册真的可以解决很多问题.做的也很人性化,操作也及其简单,几乎只要在 TD_int()里面配置一些常用的参数即可,其他都可以不用操作. 作为一 ...

- USB2.0学习笔记连载(十四):USB驱动安装及固件程序的编写

在之前的博客中已经讲过,驱动程序最核心的两个文件,一个是xxx.sys文件,一个是xxx.inf文件,主机是寻找xxx.inf文件. 在下面的文件中有相关关于USB驱动的说明.对于用户来说,xxx.s ...

- USB2.0学习笔记连载(九):USB设备驱动的安装

在第一次插入USB设备时(笔者用的是自己做的USB最小系统来测试),插入电脑后,在设备管理器中会显示 未知设备,如下图所示: 点击右键,选择属性,在详细信息中可以看到硬件ID以及PID等,如下图所示. ...

随机推荐

- android AlertDialog设置点击button不退出(转)

转载于http://blog.csdn.net/csh159/article/details/8127280 使用的是java里面的反射机制: dialog = new AlertDialog.Bui ...

- javascript 关于局部变量和全局变量

js中函数运行过程不仅仅是单纯的局部变量覆盖全局变量.和函数里面的声明情况有关. 比方: <script> var a =1; function test(){ alert(a); //a ...

- hdu 2544 最短路(两点间最短路径)

题目:http://acm.hdu.edu.cn/showproblem.php?pid=2544 方法一:dijkstra算法,求两点之间最短路径. /*********************** ...

- HTML5学习笔记(十五):方法

在一个对象中绑定函数,称为这个对象的方法. 在JavaScript中,对象的定义是这样的: var xiaoming = { name: '小明', birth: 1990 }; 但是,如果我们给xi ...

- mongoose的update函数中的回调函数是必须要传的吗

mongoose中的update的回调函数是必须要传的,如果不传,则不会更新. 例如这样写是不会更新的 tagModel.update({name:tagName},{$inc:{total:1}}, ...

- FFmpeg(3)-AVFormatContext 结构体内容分析

AVIOContext *pb IO Context,.自定义一些读写格式或者从内存当中读时用到此成员变量. char filename[1024]; ...

- Tomcat 安装为服务后台自动启用

1.首先设置环境变量 2.Java_home 3.path 4.在运行输入cmd命令后 输入tomcat所安装的路径文件中的service.bat直接拖进来即可 此时要注意 如果服务器用户没有管理员权 ...

- python(48):re.split 多分隔符

问题描述: 使用多个界定符分割字符串 问题 你需要将一个字符串分割为多个字段,但是分隔符(还有周围的空格)并不是固定的. 解决方案 string 对象的 split() 方法只适应于非常简单的字符串分 ...

- 【工具】Sublime + MarkdownEditing + OmniMarkupPreviewer使用起来

Package Control的安装 下载安装Sublime Text3后,View -> Show Console调用Console. 在Console输入以下代码安装: import url ...

- (转)Using Python3.5 in Ubuntu - Trusty

转自:https://www.reddit.com/r/IPython/comments/3lf81w/using_python35_in_ubuntu_trusty/Note:照这个方案安装pyth ...