HDMI ip中的时钟 vid_clk与ls_clk

|

文件模块

|

mr_rate_detect

|

|

|

refclock

|

被测时钟

|

|

|

measure_clk

|

参考时钟,为固定100M

|

|

|

reset

|

复位,高电平有效

|

|

|

refclock_measure

|

在一定时间内被测时钟的计数值

|

|

|

valid

|

计数完成时的效指示信号

|

tmds_clk时钟既与色彩深度有关,也与数据速率有关。

tmds时钟速率(tmds clock rate)时钟通道在HDMI电缆上振荡的速率。当字符速率小于等于340Mcsc时,TMDS时钟速率与字符速率相等。

当字符速率大于340Mcsc时,tmds时钟速率是字符速率的1/4。

字符速率(TMDS character Rate):HDMI传输线上每个数据通道上10位字符传输的速率,字符速率的表述单位为Mega-characters/second/channel(Mcsc),

当编码方式为4:2:0时24的YCbCr时,字符速率等于0.5倍的像素时钟速率;

当编码方式为4:2:0时30的YCbCr时,字符速率等于0.625倍的像素时钟速率;

当编码方式为4:2:0时36的YCbCr时,字符速率等于0.75倍的像素时钟速率;

当编码方式为4:2:0时48的YCbCr,4:2:2YCbCr或者RGB4:4:4 24位时,字符速率等于1倍的像素时钟速率;

当编码方式为4:4:4时30的RGB时,字符速率等于1.25倍的像素时钟速率;

当编码方式为4:4:4时36的RGB时,字符速率等于1.5倍的像素时钟速率;

当编码方式为4:4:4时48的RGB时,字符速率等于2倍的像素时钟速率;

像素时钟速率(Pixel Clock Rate)视频时钟中的像素传输脉冲。当像素复制有效时也包括复制像素(比如,480p的单像素复制会产生一个54M的像素时钟)

当TMDS_Bit_clock_Ratio为1时,说明接收到的HDMI字符速率在大于340 Mcsc,这时实际的TMDS_CLK时钟是字符速率的四分之一,所以程序提供的计算

字符速率的方法是:

assign measure_for_compare = TMDS_Bit_clock_Ratio? {measure[21:0], 2'b00} : measure;当TMDS_Bit_clock_Ratio为1时说明,字符速率

大于340Mcsc,字符速率= TMDS_CLK*4。

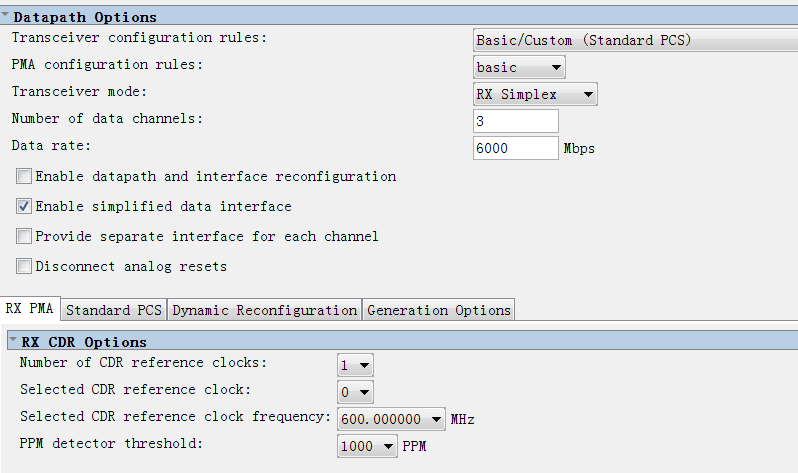

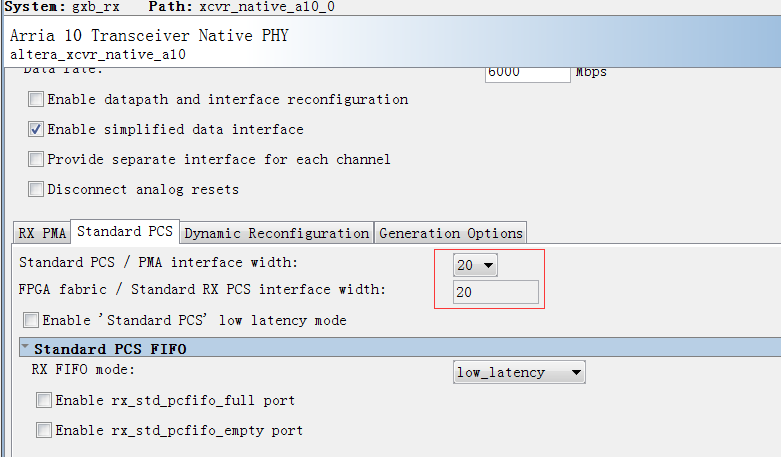

2、cdr_clk时钟的确定

cdr_clk时钟频率做为PMA部分中CDR的参考时钟,该时钟的大小与线速率有关的,如下图中的设置部分,设置Date Rate =6000Mbps,

cdr参考时钟频率为600M,而PAM与PCS之间的接口位宽为20。查看CDR的内部结构可以知道,CDR其实也是一个PLL,输出为高速串行时钟,该

高速串行时钟频率就是6000M,也就是说cdr对时钟进行了10倍频。当然如果cdr参考时钟为300M也是可以的,这样CDR就是进行20倍倍频,所以

CDR的参考时钟与ls_clk的时钟不是很明显,但是PCS部分接口位宽与线速率的倍数关系,刚好是串行时钟与ls_clk之间的关系。也就是说,

6000M/20=300M就是ls_clk的频率。但也有例外就是因为GXB只能接收1Gbps以前的数据速率,当数据速率低于1Gbps时要对数据进行过采样,

过采则要由CDR参考时钟及PLL配置来决定,举例说明:如果速率为500Mbps,参考时钟为500M,要满足不小于1Gbps的要求,则要把PLL倍频到1G

以前这里以1.5G为例,也就是PLL要三倍频,这样采到的串行数据是1.5Gbps,串转并以后,1.5G/20 = 75M,这个时钟就rx_clk的时钟,但不是

ls_clk的时钟,因为ls_clk对应的是实际的链路时钟,实际的链路上是500Mbps/20= 25M,也就是串转并之后再进行去过采样的结果。

4、ls_clk与vid_clk时钟的确定

|

DIM

|

TMDS_Bit_clock_Ratio

|

TMDS_CLK

|

CDR_CLK

|

LS_CLK

(2symbol)

|

VID_CLK

(2symbol)

|

|

8bpc

4k60fps

|

1

|

148.5

|

594

|

297

|

297

|

|

12bpc

4K30FPS

|

1

|

111.375

|

445.5

|

222.75

|

148.5

|

|

8bpc

4K30FPS

4K25fps

4k24fps

4k23fps

4k29fps

|

0

|

297

|

297

|

148.5

|

148.5

|

|

12bpc

1080p60fps

|

0

|

222.75

|

222.75

|

111.375

|

74.25

|

|

8bpc

1080P60fps,

1080p50fps

|

0

|

148.5

|

148.5

|

74.25

|

74.25

|

|

12bpc

1080p30fps

1080p24fps

1080p25fps

720p60fps

720p50fps

|

0

|

111.375

|

111.375

|

55.6875

|

37.125

|

|

8bpc

1080p30fps

1080p24fps

1080p25fps

720p60fps

720p50fps

|

0

|

74.25

|

371.25

(像素复制5倍)

74.25*5

|

37.125

|

37.125

|

|

8bpc

720p30fps

|

0

|

37.125

|

185.625

|

18.625

|

18.625

|

|

12bpc

720p30fps

|

0

|

55.6875

|

278.4375

|

27.9375

|

18.625

|

|

8bpc

720x576,50fps

720x480,60fps

|

0

|

27

|

135

|

13.5

|

13.5

|

|

12bpc

720x480,60fps

|

0

|

40.5(27*1.5)

|

202.7276(40.5*5)

|

10.125

|

13.5

|

HDMI ip中的时钟 vid_clk与ls_clk的更多相关文章

- TCP/IP中链路层的附加数据(Trailer数据)和作用

1.TCP/IP中链路层的附加数据是什么 在用wireshark打开报文时,链路层显示的Trailer数据就是附加数据,如图 2.如何产生 1.例如以太网自动对小于64字节大小的报文进行填充(未实验) ...

- TCP/IP中最高大上的链路层简介(二)

引言 对于程序猿来讲,似乎越接近底层,就越显得高大上.这也算是程序猿们的共同认知吧,虽然不是所有人.今天LZ就和各位一起探讨一下TCP/IP中最高大上的一层,也就是最底层的链路层. 这一层LZ了解的还 ...

- TCP/IP协议原理与应用笔记11:TCP/IP中地址与层次关系

1. 网络中常用的地址: 2. TCP/IP中地址与层次关系 :

- BAT面试上机题从3亿个ip中找出访问次数最多的IP详解

我们面临的问题有以下两点:1)数据量太大,无法在短时间内解决:2)内存不够,没办法装下那么多的数据.而对应的办法其实也就是分成1)针对时间,合适的算法+合适的数据结构来提高处理效率:2)针对空间,就是 ...

- TCP/IP中的传输层协议TCP、UDP

TCP提供可靠的通信传输,而UDP则常用于让广播和细节控制交给应用的通信传输. 传输层协议根据IP数据报判断最终的接收端应用程序. TCP/IP的众多应用协议大多以客户端/服务端的形式运行.客户端是请 ...

- 数字设计中的时钟与约束(gate)

转载:https://www.cnblogs.com/IClearner/p/6440488.html 最近做完了synopsys的DC workshop,涉及到时钟的建模/约束,这里就来聊聊数字中的 ...

- HDMI IP学习笔记

在HDMI的IP核中点击,生成例子.找到./simulaion/mentor文件夹,把modelsim路径转到该路径下,即可仿真.

- TCP/IP中你不得不知的十大秘密

这段时间 有一点心很浮躁,不过希望自己马上要矫正过来.好好学习编程!这段时间我想好好地研究一下TCP/IP协议和网络传输这块!加油 一.TCP/IP模型 TCP/IP协议模型(Transmission ...

- 三叔学FPGA系列之一:Cyclone V中的时钟资源

之前的项目中更多的是有师兄提供经验和帮助,追求的是快速上手,所以不管对于硬件电路设计,还是verilog电路编程,甚至是FPGA内部的资源,都没来得及系统地学习,最近在做算法到电路的实现,正好系统学习 ...

随机推荐

- 认识Thymeleaf:简单表达式和标签 基础信息

转载:https://www.cnblogs.com/beyrl-blog/p/6633182.html 本文只适用于不会Java对HTML语言有基础的程序员们,是浏览了各大博客后收集整理,重新编辑的 ...

- 使用clear来清除localStorage保存对象的全部数据

<!doctype html> <html> <head> <meta charset="utf-8"> <title> ...

- windows上安装RabbitMQ

windows下 安装 rabbitMQ 及操作常用命令 rabbitMQ是一个在AMQP协议标准基础上完整的,可服用的企业消息系统.它遵循Mozilla Public License开源协议,采用 ...

- Luogu 2147 洞穴勘测 - LCT

Solution $LCT$ 打上 $cut$ , $link$ 和 $finroot$ 即可 Code #include<cstdio> #include<cstring> ...

- 利用gulp搭建less编译环境

什么是less? 一种 动态 样式 语言. LESS 将 CSS 赋予了动态语言的特性,如 变量, 继承, 运算, 函数. LESS 既可以在 客户端 上运行 (支持IE 6+, Webkit, ...

- Linux设置桌面图标 (双击运行jar包)

Ubuntu平台 预备条件: 1)平台是Gridion上的Ubuntu 2)安装了JRE (版本如下) 3)在IDE(我用的是IDEA)打包成可运行的jar文件 设置步骤: 1)新建.desktop文 ...

- Linux安装及入门

Linux安装及学习 Linux遇到的问题: 在安装过程中因为代码输错(少空格)而质疑自己下载的ubuntu和virtualbox版本,于是卸载之后重新安装了一次,后来才发现是代码输错了(教程中的空格 ...

- Spring IOC(二)beanName 别名管理

Spring IOC(二)beanName 别名管理 Spring 系列目录(https://www.cnblogs.com/binarylei/p/10198698.html) 一.AliasReg ...

- Linux 禁止root 用户登录启用sudo

1.添加sudo用户执行visudo命令,找到: 复制代码 代码如下: root ALL=(ALL) ALL 在下面增加:(注意,qianyunlai 是Linux新增的一个普通用户),没有的话可创建 ...

- 隐马尔科夫_HMM

有向图 抽象:λ代表输入:输入一个句子,λi表示句子中的每个字 O代表输出:[B词首/M词中/E词尾/S单独成词] max=maxP(O1 O2 On/ λ1 λ2 λn) 假设: (1)当前观察值只 ...