S5PV210 时钟体系分析

S5PV210 时钟体系

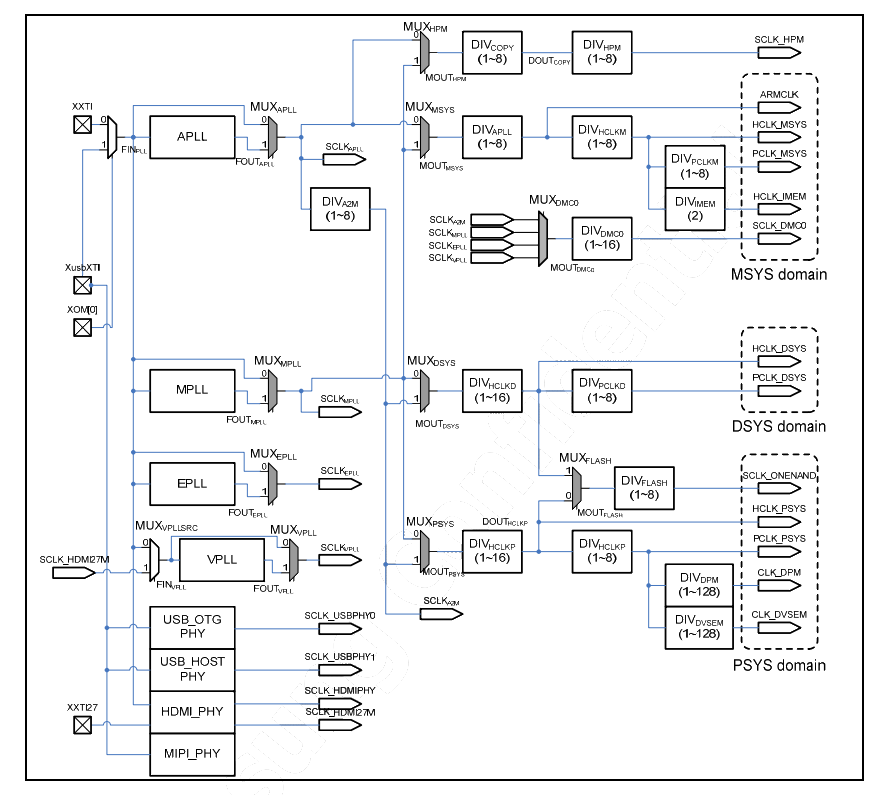

如下面时钟结构图所示,S5PV210 中包含 3 大类时钟域, 分别是主系统时钟域(简称 MSYS)、显示相关的时钟域(简称 DSYS)、 外围设备的时钟域(简称 PSYS)。

1) MSYS:用来给 cortex a8 处理器、DRAM 控制器、3D、IRAM、IROM、INTC(中断控制器)等提供时钟;

2) DSYS:用来给显示相关的部件提供时钟,包括 FIMC、FIMD、JPEG 和 multimedia IPs;

3) PSYS:用来给外围设备提供时钟,如 i2s、spi、i2c、uart 等。

Mini210S 外接的晶振频率(简称 Fin)为 24MHz,通过时钟控制逻辑 PLL 可以提高系统时钟。

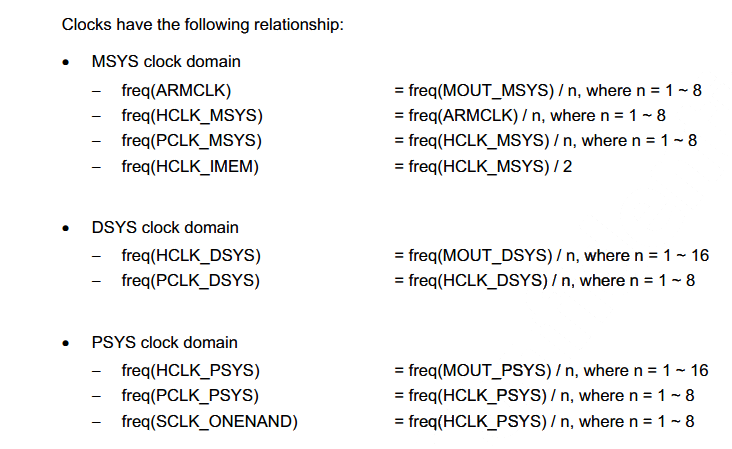

S5PV210 共有 4 个倍频器,即 PLL, 包括 APLL(供 MSYS 使用),MPLL(供 DSYS 使用),EPLL(供 PSYS使用),VPLL(供 video 相关的时钟使用)。 3 大类时钟域中,可以使用不同的分频,使其给不同部件输出所需要的时钟,各类时钟的关系如下图:

芯片手册上给出了参考值, 我们按照参考值设置即可, 各类时钟的参考值如下图:

时钟初始化程序

#define APLL_MDIV 0x7d

#define APLL_PDIV 0x3

#define APLL_SDIV 0x1

#define MPLL_MDIV 0x29b

#define MPLL_PDIV 0xc

#define MPLL_SDIV 0x1

#define set_pll(mdiv, pdiv, sdiv) (1<<31 | mdiv<<16 | pdiv<<8 | sdiv)

#define APLL_VAL set_pll(APLL_MDIV,APLL_PDIV,APLL_SDIV)

#define MPLL_VAL set_pll(MPLL_MDIV,MPLL_PDIV,MPLL_SDIV)

void clock_init()

{

/* 1 设置各种时钟开关, 暂时不使用 PLL */

CLK_SRC0 = 0x0;

/* 2 设置锁定时间,使用默认值即可 */

APLL_LOCK = 0x0000FFFF;

MPLL_LOCK = 0x0000FFFF;

/* 3 设置分频 */

CLK_DIV0 = 0x14131440;

/* 4 设置 PLL */

APLL_CON0 = APLL_VAL;

MPLL_CON = MPLL_VAL;

/* 5 设置各种时钟开关,启用 PLL */

CLK_SRC0 = 0x10001111;

}

程序分析:

第一步 设置各种时钟开关,暂时不使用 PLL

在未设置 PLL 和各种分频系数之前,我们不能使用 PLL, 为了保险起见, 暂时直接使用频率较低的外接的 24MHz 晶振,待设置好 PLL 和分频系数后再重新设置各种时钟开关。

第二步 设置锁定时间

设置 PLL 后,时钟从 Fin 提升到目标频率时,需要一定的时间,即锁定时间,使用默认值即可。

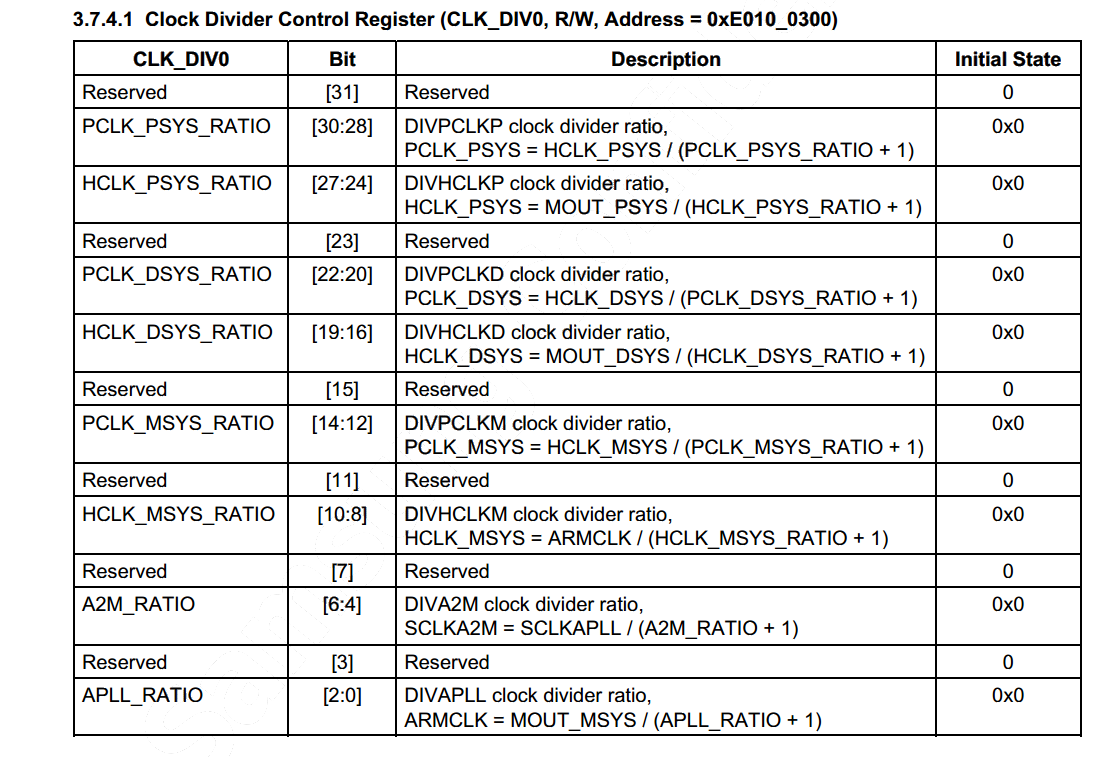

第三步 设置分频

与分频相关的寄存器是 CLK_DIV0,见下图:

根据手册中给出的参考值来设置该寄存器。

ARMCLK = 1000MHz = MOUT_MSYS / (APLL_RATIO + 1),经过在第四和第五步的设置后, MOUT_MSYS会被设置为 1000MHz,所以 APLL_RATIO=0 即可

SCLKA2M = 200MHz = SCLKAPLL / (A2M_RATIO + 1),由于 SCLKAPLL = 1000MHz,所以 A2M_RATIO=4。

HCLK_MSYS = 200MHz = ARMCLK / (HCLK_MSYS_RATIO + 1),所以 HCLK_MSYS_RATIO=4

PCLK_MSYS = 100MHz = HCLK_MSYS / (PCLK_MSYS_RATIO + 1),所以 PCLK_MSYS_RATIO=1

HCLK_DSYS = 166MHz = MOUT_DSYS / (HCLK_DSYS_RATIO + 1), 经过在第四和第五步的设置后,MOUT_DSYS =667MHz, 所以 HCLK_DSYS_RATIO=3

PCLK_DSYS = 83MHz = HCLK_DSYS / (PCLK_DSYS_RATIO + 1),所以 PCLK_DSYS_RATIO=1

HCLK_PSYS = 133Mhz = MOUT_PSYS / (HCLK_PSYS_RATIO + 1), 经过在第四和第五步的设置后,MOUT_PSYS =667MHz 所以 HCLK_PSYS_RATIO=4

PCLK_PSYS = 66Mhz = HCLK_PSYS / (PCLK_PSYS_RATIO + 1), 所以 HCLK_PSYS_RATIO=1

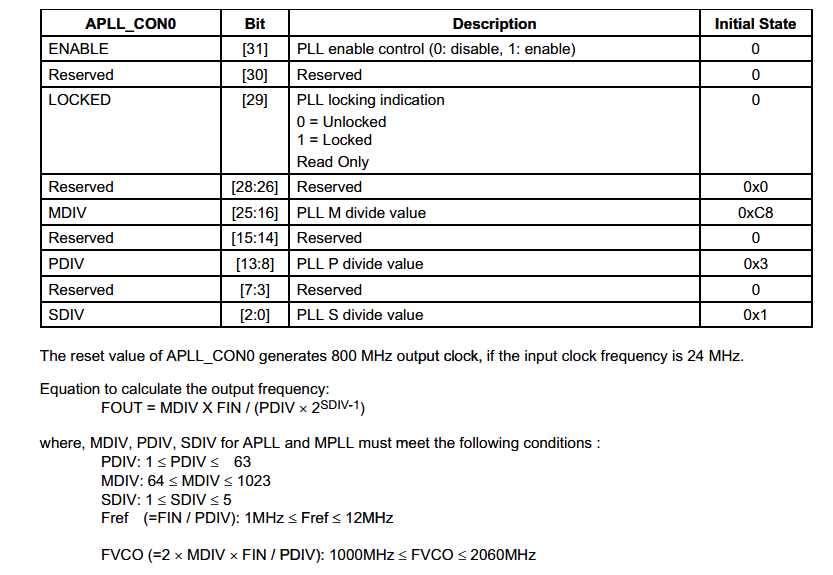

第四步 设置 PLL

PLL 即倍频器,用来放大运行频率。 设置好分频后,我们就需要设置 PLL 了。 APLL 和 MPLL 的启动是通过分别设置 APLL_CON0 和 MPLL_CON 寄存器,我们逐个来设置。

APLL_CON0

APLL_CON0 负责设置 APLL, FINPLL=24MHz,经过 APLL 后,我们将输出 FOUT=1000Mhz 的时钟频率, FOUT 的计算公式如下:

FOUT=MDIV*FIN/(PDIV*2^(SDIV-1)) = 1000 MHz

由于 FIN=24MHz,FOUT=1000MHz,我们可以这样取值: MDIV= 0x7d, PDIV= 0x3, SDIV=1。这 3 个值并不是固定死的,只要能使 FOUT=1000Mhz,任意搭配都是可以的。

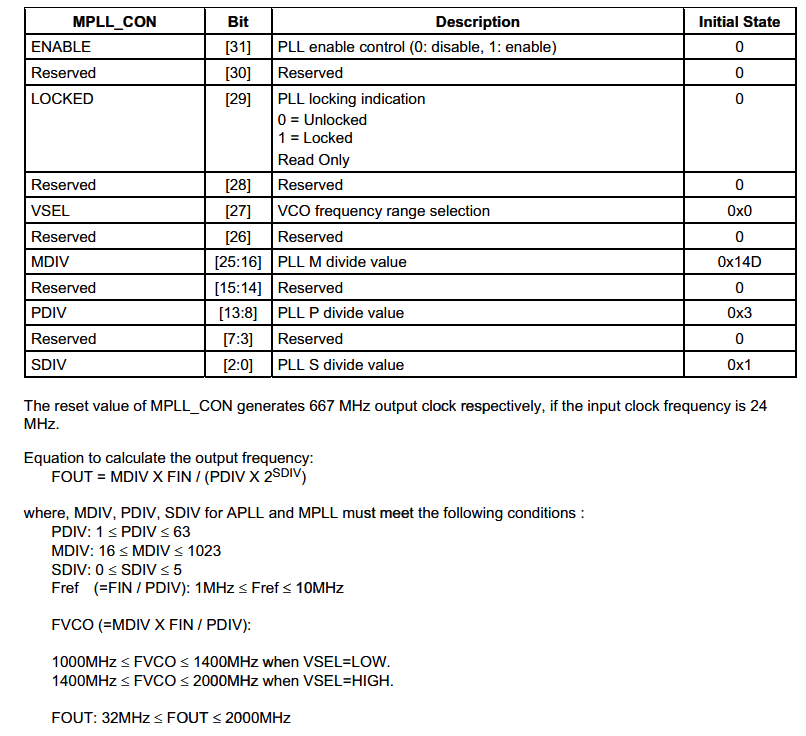

MPLL_CON

MPLL_CON 寄存器负责设置 MPLL,经过 MPLL 后,我们将输出 FOUT=667Mhz 的时钟频率, FOUT 的计算公式如下:

FOUT=MDIV*FIN/(PDIV*2^SDIV) = 667 MHz

由于 FIN=24MHz,FOUT=667MHz,我们可以这样取值: MDIV=0x29B,PDIV= 0xC, SDIV=1。这 3 个值并不是固定死的,只要能使 FOUT=667Mhz,任意搭配都是可以的。

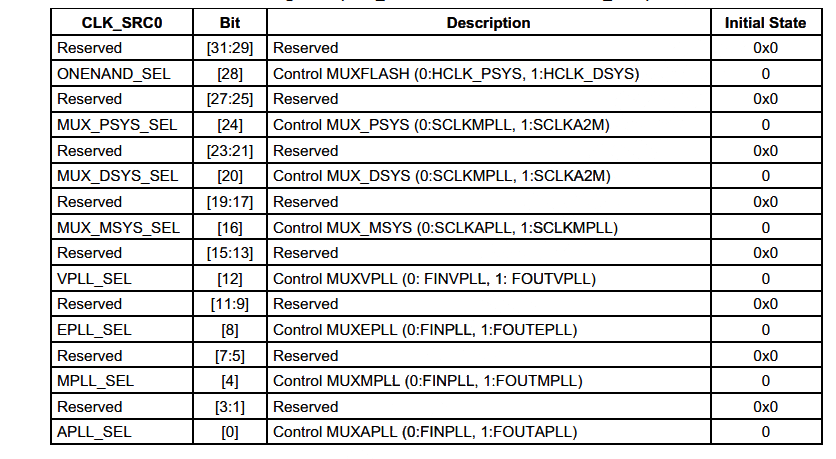

第五步 设置各种时钟开关

参考 S5PV210 时钟结构图,设置各种时钟开关:

APLL_SEL = 1,使用 FOUTAPLL

MPLL_SEL = 1,使用 FOUTMPLL

EPLL_SEL = 1, 使用 FOUTEPLL

VPLL_SEL = 1,使用 FOUTVPLL

MUX_MSYS_SEL = 0, 使用 SCLKAPLL

MUX_DSYS_SEL = 0, 使用 SCLKMPLL

MUX_PSYS_SEL = 0,使用 SCLKMPLL

ONENAND_SEL = 1, 使用 HCLK_DSYS

所以 CLK_SRC0 = 0x10001111;

以上程序,通过设置时钟相关的寄存器,达到了初始化时钟的目的(实际上我们并不需要设置好所有部件的工作时钟,我们只需设置好我们需要使用的硬件部件的工作时钟即可)。

本篇文章参考:《友善之臂210手册》

S5PV210 时钟体系分析的更多相关文章

- S3C2440时钟体系

注:以下内容学习于韦东山老师arm裸机第一期视频教程 一. 2440时钟简介 1.1 2440是一个SOC(system on chip)系统,不仅有很多CPU,还有很多外设,在2440芯片手册有系统 ...

- STM32F4时钟配置分析

//学习STM32F4的过程中关于时钟上面讲的比较好 特地转发与大家分享 STM32F4时钟设置分析 原文博客链接:http://blog.csdn.net/jdh99,作者:jdh,转载请注明. 环 ...

- headfirst设计模式(5)—工厂模式体系分析及抽象工厂模式

先编一个这么久不写的理由 上周我终于鼓起勇气翻开了headfirst设计模式这本书,看看自己下一个设计模式要写个啥,然后,我终于知道我为啥这么久都没写设计模式了,headfirst的这个抽象工厂模式, ...

- RFID:ISO14443、15693、18000体系分析

射频标签的通信标准是标签芯片设计的依据,目前国际上与RFID相关的通信标准主要有:ISO/IEC 18000标准(包括7个部分,涉及125KHz, 13.56MHz, 433MHz, 860-960M ...

- 第九篇:S3C2400时钟体系

S3C2400时钟体系 S3C2400时钟配置流程 该学习板使用了外部晶振12Mhz 晶振--->经过MPLL(锁相环) --->(倍频得到)FCLK--->(对FCLK分频得到)H ...

- [netty4][netty-transpot]Channel体系分析

Channel体系分析 接口与类结构体系 -- [I]AttributeMap, ChannelOutboundInvoker, Comparable -- [I]AttributeMap ---- ...

- 第010课_掌握ARM芯片时钟体系

from:第010课_掌握ARM芯片时钟体系 第001节_S3C2440时钟体系结构 S3C2440是System On Chip(SOC),在芯片省不仅仅有CPU,还有一堆外设. 至于有哪些外设,可 ...

- s3c2440裸机-时钟编程(一、2440时钟体系介绍)

1.总线框架 下图是2440的总线框架,其中有AHB(Advanced High performance Bus)高速总线,APB(Advanced Peripheral Bus)外围总线. 不同总线 ...

- 总结:S5PV210时钟系统

在数据手册<S5PV210_UM_REV1.1>中的section 02_system/3 CLOCK CONTROLLER(354页) 一.时钟域 在S5PV210的SoC中,时钟系 ...

随机推荐

- c语言基础课第三次作业

7-1找出最小值 1.实验代码 #include <stdio.h> int main(void) int n, i, m, min; scanf("%d", & ...

- 如何解决XMLHttpRequest cannot load file:~~~~~~~~~~~. Cross origin requests are only supported for protocol schemes: http, data, chrome, chrome-extension, https, chrome-extension-res

原因:Chrome不支持本地Ajax请求. 解决: 右击Chrome浏览器快捷方式,选择“属性”,在“目标”中加上"--allow-file-access-from-files", ...

- 21.ArrayList

ArrayList是实现List接口的动态数组,所谓动态就是它的大小是可变的.实现了所有可选列表操作,并允许包括 null 在内的所有元素.除了实现 List 接口外,此类还提供一些方法来操作内部用来 ...

- Alpha阶段项目复审(冲鸭队)

Alpha阶段项目复审(冲鸭队) 组名 优点 缺点 排名 天冷记得穿秋裤队 支持文件离线开源下载,没有限速 部分功能未实现 1 中午吃啥队 点餐系统用户需求较高,系统功能完善 界面可以再完善一下些 2 ...

- 关于SGA中的granule size

1.什么是granule? granule直译为颗粒,ORACLE为SGA 中的组件(eg:log buffer/db buffer/large pool等)分配的最小单元为一个granule. 所以 ...

- uniGUI日志的控制

uniGUI日志的控制 (2015-10-12 08:30:29) 转载▼ 标签: unigui 分类: uniGUI uniGUI本身提供了日志功能,利用uniServerModule.Server ...

- CentOS 7安装新版RabbitMQ解决Erlang 19.3版本依赖

通过yum等软件仓库都可以直接安装RabbitMQ,但版本一般都较为保守. RabbitMQ官网提供了新版的rpm包(http://www.rabbitmq.com/download.html),但是 ...

- [UWP]如何实现UWP平台最佳图片裁剪控件

前几天我写了一个UWP图片裁剪控件ImageCropper(开源地址),自认为算是现阶段UWP社区里最好用的图片裁剪控件了,今天就来分享下我编码的过程. 为什么又要造轮子 因为开发需要,我们需要使用一 ...

- 深入浅出TCP/IP协议

目录 什么是网络协议? 谁来制定这个网络协议? TCI/IP协议 什么是socket? http协议属于应用层还是传输层? soap可以使用HTTP协议进行传输吗? 各层协议举例 什么是网络协议? 话 ...

- Java实现大数相加、相乘(不使用BigInteger)

大数相加: package algorithm; //使用BigInteger类验证 import java.math.BigInteger; public class BigAdd { public ...