在数字电路中,出于应用的需要,我们可以使用无符号数,即包括0及整数的集合;也可以使用有符号数,即包括0和正负数的集合。在更加复杂的系统中,也许这两种类型的数,我们都会用到。

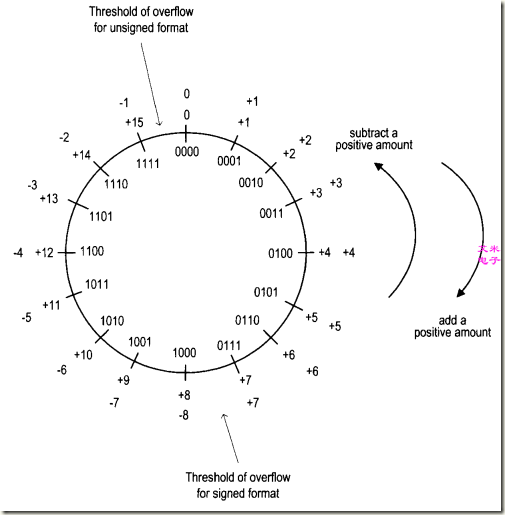

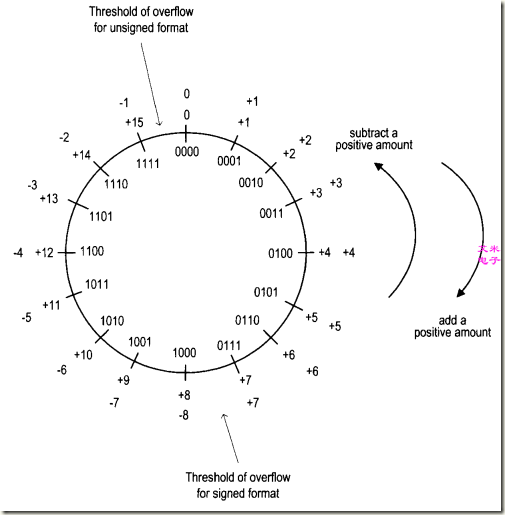

有符号数通常以2的补码形式来表示。图1列出了4位二进制表示法所对应正负数。进一步观察,我们发现两种类型数的加减法是一样的,做加法和减法就是 在数轮上按正时钟转转或按反时钟转。比方说,1001+0100,意味着从1001按照顺时钟方向移动4个位置,其结果为1101。在无符号数类型中,它 代表(+9)+(+4)=+13;而在有符号数类型中,它则代表(-7)+(+4)=-3。从数轮上看,若是加法所得的结果溢出了,那么也就是穿越了数轮 的临界点。注意这个临界点对于无符号数和有符号数来说,是不一样的:无符号数,是介于1111和0000之间;有符号数,则是介于0111和1000之 间。

物理加减法的行为正好和数轮的移动类似。只要所有的运算子和结果具有相同的位宽,那么有符号数或无符号数的形式就可用于相同的电路。比方说,设a、b和sum都是8位信号,表达式

无论这些信号被转译成有符号数或无符号数,它都会引用相同的硬件且使用相同的二进制表示法。这种现象在其他算术运算中也是正确的(但是它不可用于非算术运算中,比方说有理数运算或溢出标志位的生成)。

图1 4位二进制数轮

此外,当运算子或其结果的位宽不同时,我们需要区分它究竟使用哪一种符号类型。因为不同的符号类型需要不同的扩展位。对于无符号数,前置一个0,即 所谓的零扩展位;对于有符号数来说,需要前置n个所谓的符号扩展位。比方说4位二进制表示的-5为1011;当其扩展成8位时,应该变为 1111_1011,而不是0000_1011。

举个例子,设a和sum为8位信号,b为4位信号即b3b2b1b0。表达式

需要将b扩展为8位。如果是无符号数形式,那么b扩展为0000_b3b2b1b0;如果是有符号数形式,那么b扩展为 b3b3b3b3_b3b2b1b0。上述表达式所引用的硬件包括位宽扩展电路和加法器。因为对于有符号数和无符号数来说,扩展电路是不同的;所以上面那 个表达式,对应有符号数和无符号数形式,要使用不同的硬件实现。

2 Verilog-1995中的有符号数

在Verilog-1995中,只有integer数据类型被转移成有符号数,而reg和wire数据类型则被转移成无符号数。由于integer 类型有固定的32位宽,因此它不太灵活。我们通常使用手动加上扩展位来实现有符号数运算。下面的代码片段将描述有符号数和无符号数的运算:

03 |

reg [7:0] sum1, sum2, sum3, sum4; |

05 |

// same width. can be applied to signed and unsigned |

07 |

// automatica 0 extension |

10 |

sum3 = a + {4{ 1'b0 }, c}; |

11 |

// manual sign extension |

12 |

sum4 = a + {4{c[3]}, c}; |

在第一条语句中,a、b和sum1有相同的位宽,因此无论是转译成有符号数还是无符号数,它都将引用相同的加法器电路。

在第二条语句中,c的位宽仅为4,在加法运算中,它的位宽会被调整。因为reg类型被作为无符号数看待,所以c的前面会被自动置入0扩展位。

在第三条语句中,我们给c手动前置4个0,以实现和第二个表达式一样的效果。

在第四条语句中,我们需要把变量转译成有符号数。为了实现所需的行为,c必须扩展符号位到8位。没有其他的办法,只好手动扩展。在代码中,我们重复复制c的最高位4次(4{c[3]})来创建具有扩展符号位的8位数。

3 Verilog-2001中的有符号数

在Verilog-2001中,有符号形式也被扩展到reg和wire数据类型中。哈哈,新加一个关键字,signed,可以按照下面的方式定义:

使用有符号数据类型, 第2节所述代码可以被改写为:

3 |

reg signed [7:0] sum1, sum4; |

5 |

// same width. can be applied to signed and unsigned |

7 |

// automatic sign extension |

第一条语句将引用一个常规的加法器,因为a、b和sum1具有相同的位宽。

第二条语句,所有的右手边变量都具有signed数据类型,c被自动扩展符号位到8位。因此,无需再手动添加符号位。

在小型的数字系统中,我们通常可以选用有符号数或者无符号数。然而,在一些大型的系统中,会包括不同形式的子系统。Verilog是一种弱类型语 言,无符合变量和有符号变量可以在同一表达式中混用。根据Verilof的标准,只有当所有右手边的变量具有signed数据类型属性的时候,扩展符号位 才被执行。否则,所有的变量都只扩展0。考虑下面的代码片段:

1 |

reg signed [7:0] a, sum; |

由于c不具有signed数据类型属性,因此右手边的变量b和c的扩展位为0。

Verilog有两个系统函数,$signed和$unsigned(),用以将括号内的表达式转换为signed和unsigned数据类型。比方说,我们可以转换c的数据类型,

1 |

sum = a + b + $signed(c); |

现在,右手边的所有变量都具有signed数据类型属性,因此b和c将扩展符号位。

在复杂的表达式中,混用signed和unsigned数据类型将引入一些微妙的错误,因此应当避免混用。如果真的很有必要,那么表达式需要保持简单,同时通用转换函数,以确保数据类型的一致性。

- Verilog有符号数处理

内容主要摘自以下两个链接: https://www.cnblogs.com/LJWJL/p/3481995.html https://www.cnblogs.com/LJWJL/p/3481807 ...

- verilog 有符号数运算

1)之前的笔记写过<补码探讨>,可知在FPGA综合成电路的时候最底层都是以补码的形式在运算,正数的补码就是本身,负数的补码要取反+1. (2)那么Verilog中编程的时候对编程人员来说, ...

- verilog中的有符号数运算

verilog中的有符号数运算 http://hi.baidu.com/lixu1113/item/d00dc095f86aed48f142159a verilog中的有符号数运算 有符号数的计算:若 ...

- verilog中的有符号数理解(转)

verilog中的有符号数运算 有符号数的计算:若有需要关于有号数的计算,应当利用Verilog 2001所提供的signed及$signed()机制. Ex: input signed [7:0] ...

- verilog中符号位的扩展问题

以下内容转自 艾米电子 - 使用有符号数,Verilog(http://www.cnblogs.com/yuphone/archive/2010/12/12/1903647.html) Verilog ...

- Verilog有符号整型数(signed int)比大小

本文参考了https://blog.csdn.net/wenxinwukui234/article/details/42119265/ 关于2进制补码的思考和讨论. ================= ...

- C语言基础(5)-有符号数、无符号数、printf、大小端对齐

1.有符号数和无符号数 有符号数就是最高位为符号位,0代表正数,1代表负数 无符号数最高位不是符号位,而就是数的一部分而已. 1011 1111 0000 1111 1111 0000 1011 10 ...

- matlab和FPGA中无符号数和有符号数的转化(转)

在FPGA 设计过程中经常会遇到关于数表示之间的转化问题,最常见的是无符号数和有符号数之间的转化问题.(1)在FPGA设计过程中,能够很直接的看出数字的位宽,但经常以无符号数的形式输出,在后继的处理中 ...

- quartus ii有符号数的问题(待完善)

1.有符号数是以补码的形式存储的,在modelsim仿真时,补码自动转换为有符号的十进制数. 2.关于截位的问题: 当只取寄存器中的其中m位时,这时候取得的数是按照无符号位来处理的? 3.reg型数据 ...

- C语言中无符号数和有符号数之间的运算

C语言中无符号数和有符号数之间的运算 C语言中有符号数和无符号数进行运算(包括逻辑运算和算术运算)默认会将有符号数看成无符号数进行运算,其中算术运算默认返回无符号数,逻辑运算当然是返回0或1了. un ...

随机推荐

- WordPress版微信小程序2.4版发布

自从发布2017年9月16日WordPress版微信小程序2.2.8版本后,这个一个多月来,WordPress版微信小程序,在经过一些比较小的更新后,今天发布阶段性的版本:2.4版 .这版本主要是功能 ...

- Kafka介绍与消息队列

消息队列的好处: 消息队列(Message Queue) 消息: 网络中的两台计算机或者两个通讯设备之间传递的数据.例如说:文本.音乐.视频等内容. 队列:一种特殊的线性表(数据元素首尾相接),特殊之 ...

- XAMPP 虚拟主机配置,实现多域名访问本地项目

XAMPP 虚拟主机配置,实现多域名访问本地项目 1.首先你既然要配置多个虚拟主机,那你肯定需要多个站点的目录文件.你可以在e盘创建 www文件夹,然后在该文件件中新建两个站点目录,假设test.co ...

- JS高级-异步

单线程 只有一个线程,同一时间只能做一件事 原因:避免DOM渲染的冲突 浏览器需要渲染DOM JS可以修改DOM结果 JS执行的时候,浏览器DOM渲染会暂停 两段JS也不能同时执行(修改DOM就冲突) ...

- Mysql数据表去重

查询不重复元素个数 select count(distinct domain) from black_botnet_domian; 查询表中元素个数大于等于2的元素 SELECT goods_id,g ...

- java常见面试题及答案 11-20(JVM)

11.JVM内存分哪几个区,每个区的作用是什么? Java虚拟机主要分为以下一个区: 方法区:1. 有时候也成为永久代,在该区内很少发生垃圾回收,但是并不代表不发生GC,在这里进行的GC主要是对方法区 ...

- OS与Internet

1 操作系统 操作系统(Operating System,简称OS)是管理和控制计算机硬件与软件资源的计算机程序,是直接运行在“裸机”上的最基本的系统软件,任何其他软件都必须在操作系统的支持下才能运行 ...

- Django01-Django基础

一.什么是web框架? 框架,即framework,特指为解决一个开放性问题而设计的具有一定约束性的支撑结构,使用框架可以帮你快速开发特定的系统.对于所有的Web应用,本质上其实就是一个socket服 ...

- JAVA结合testng断言verify(断言失败不中断继续执行)

原理: 1.自已构造一个断言类,把Assert.assertEquals给try catch住. 2.利用testng的监听类在测试方法运行结束后进行分析. 代码: 断言类: package com. ...

- win server 2012 服务器不能ping通

以windows server 2012作为服务器,服务器能够ping通局域网中的客户端A,但A不能ping通服务器. 解决办法: 确定服务器中系统->远程设置->远程桌面选项下为允许选项 ...