基于FPGA的数字钟设计---第三版---郝旭帅电子设计团队

本篇为各位朋友介绍基于FPGA的数字钟设计---第三版。

功能说明:

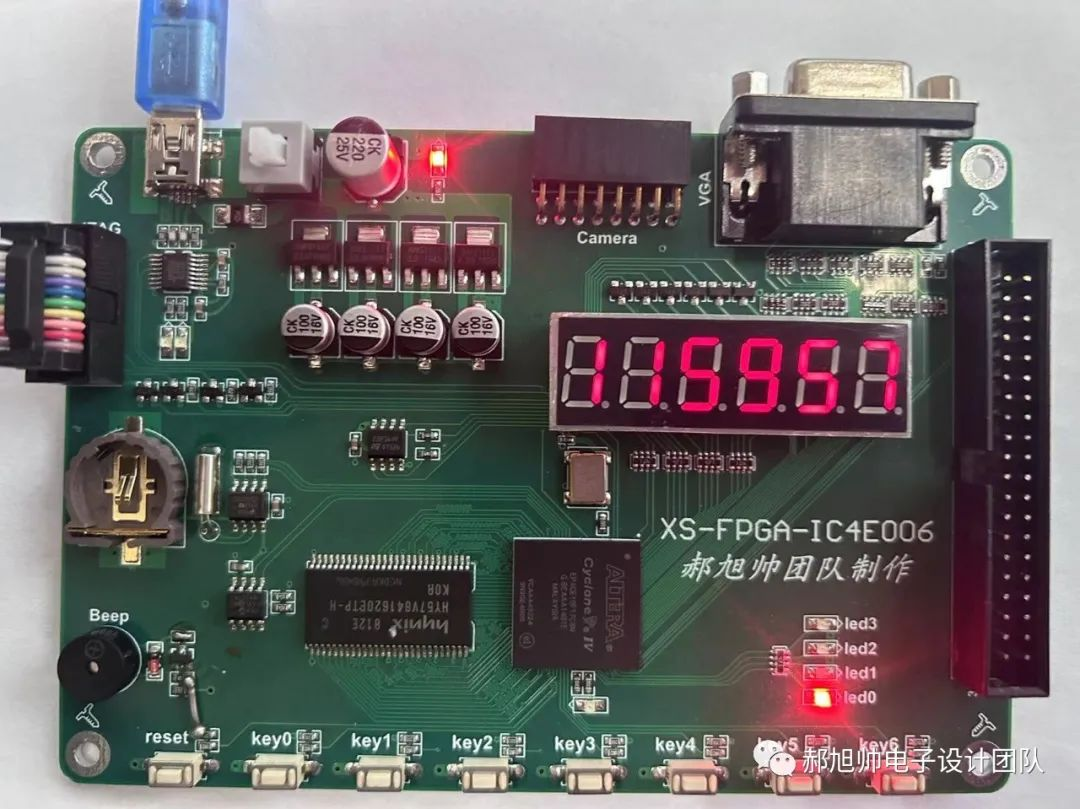

在数码管上面显示时分秒(共计六个数码管,前两个显示小时;中间两个显示分钟;最后两个显示秒)。

利用按键可以切换24/12小时制(默认24小时制)。

led1的亮灭表示24小时制(亮)还是12小时制(灭)。

led2的亮灭表示上午(亮)还是下午(灭),24小时制时,一直灭。

增加调整按键和加减按键。

调整按键不按下时,正常显示时分秒。

按下第一次,进入调整状态,时间停止,并且小时开始闪烁,通过加减按键可以进行调整。

按下第二次,分钟开始闪烁,通过加减按键可以进行调整。

按下第三次,秒开始闪烁,通过加减按键可以进行调整。

按下第四次,进入正常运行状态。

后续再按下时,重复以上的过程

使用平台:本次设计应用Altera的平台设计(芯片:EP4CE10F17C8N)。

仿真平台:Modelsim。

作者QQ:746833924

说明:本篇设计中不涉及到IP和原语,代码在其他平台依然可以适用;当其他板卡电路不同时,会导致不同的现象出现,如有需要修改代码请联系作者;如需作者使用的板卡,请联系作者;

设计思想如下:

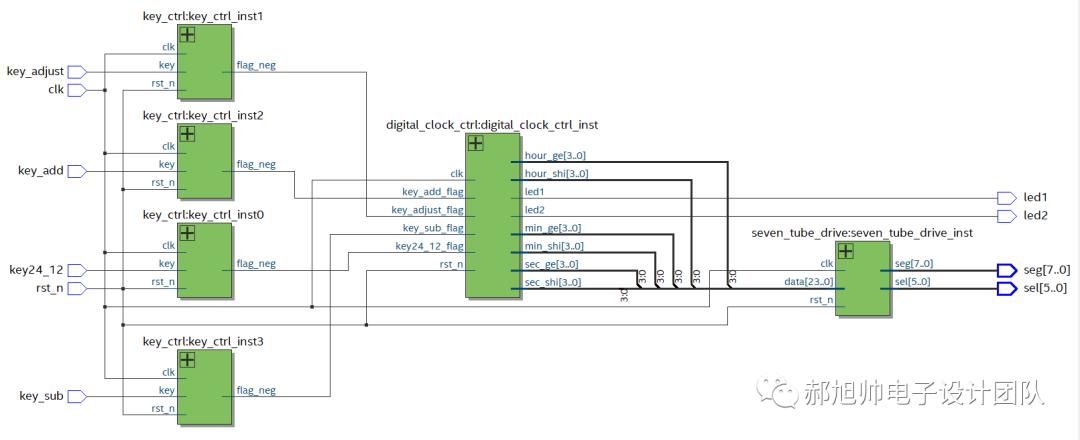

key_ctrl模块负责将外部的按键信号进行消抖,并且产生对应边沿变化时的脉冲;digital_clock_ctrl模块负责根据脉冲信号和设计逻辑产生对应数字逻辑和led的状态;seven_tube_drive(七段数码管驱动)模块负责将digital_clock_ctrl模块产生的数字逻辑显示到数码管上。

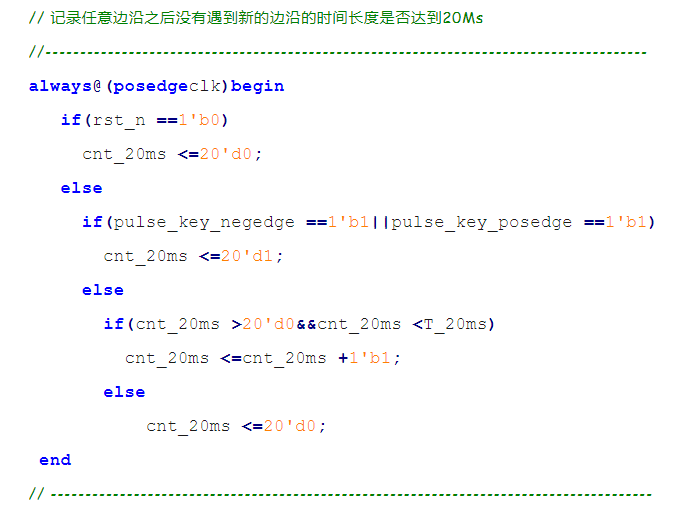

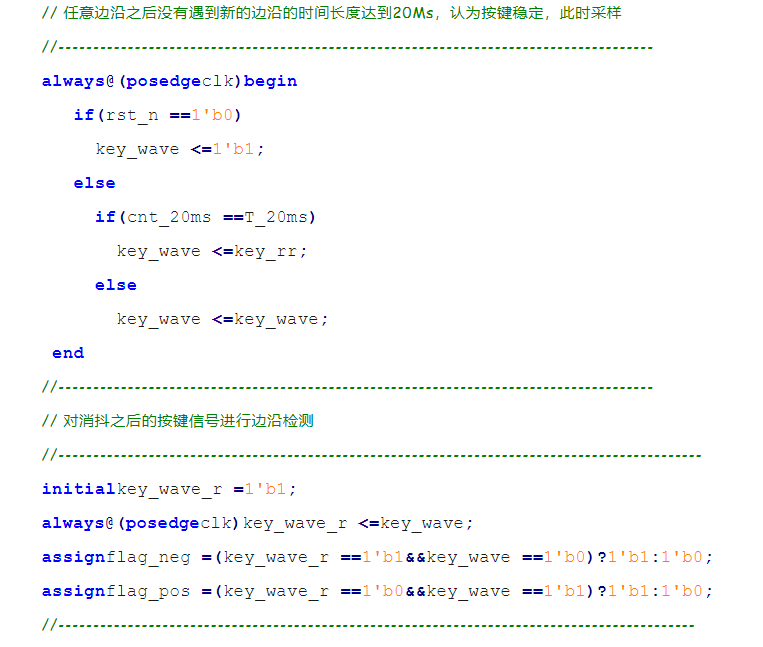

key_ctrl模块设计思想为:按键信号是由外部机械式按键产生,每次按下或者抬起时,会产生一定的抖动。如果直接对其进行边沿检测就会导致多次触发。故而需要设计按键消抖,进而对消抖之后的波形进行边沿检测。消抖原理为:外部按键信号发生改变后,如果能够持续20ms,没有新的改变,就认为此次改变不是抖动,而是真正的按下,然后进行采样即可。

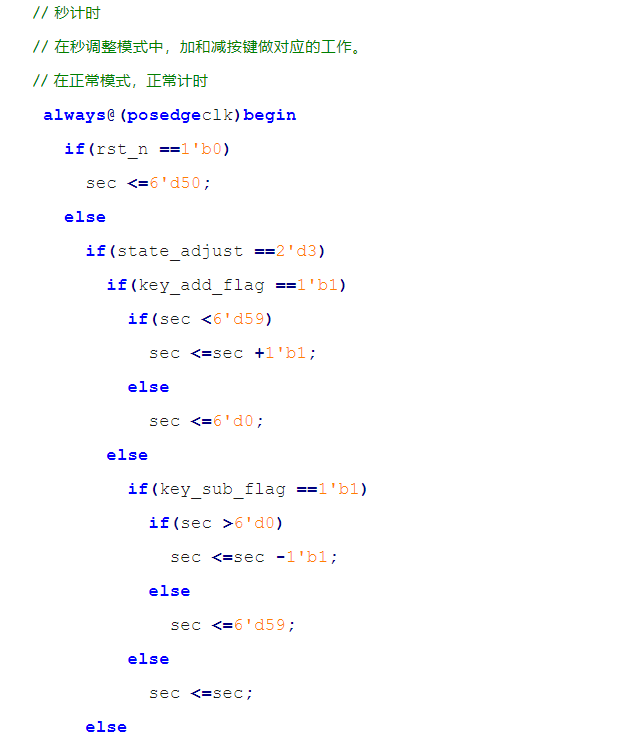

digital_clock_ctrl模块的设计思想:首先根据外部的调整脉冲,确定工作状态。

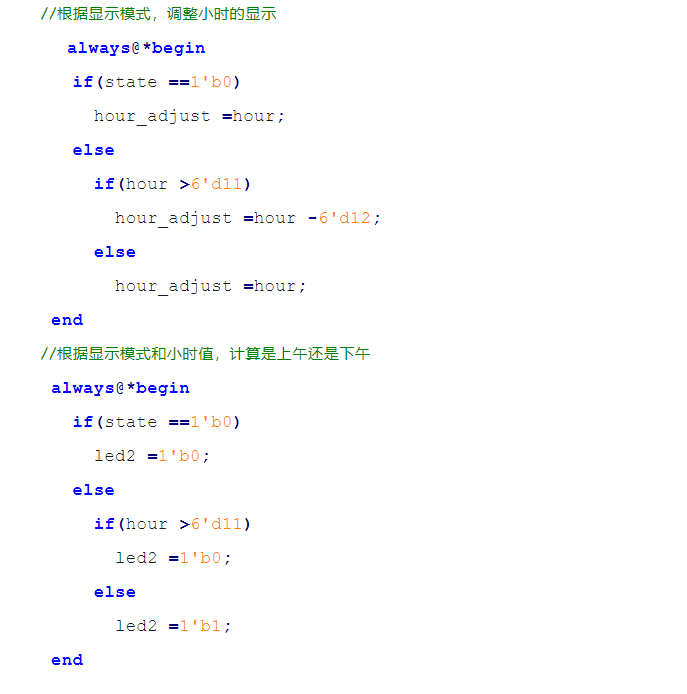

24小时进制和12小时进制在外部按键按下时切换;分和秒的显示没有改变,小时的显示需要调整。24小时制时,正常显示;12小时制时,时大于11时,需要减去12;并且利用led2进行表是为上午还是下午。

如果在调整模式中,启动一个一秒钟的计时器。

分钟和小时类似,在这里不在赘述。

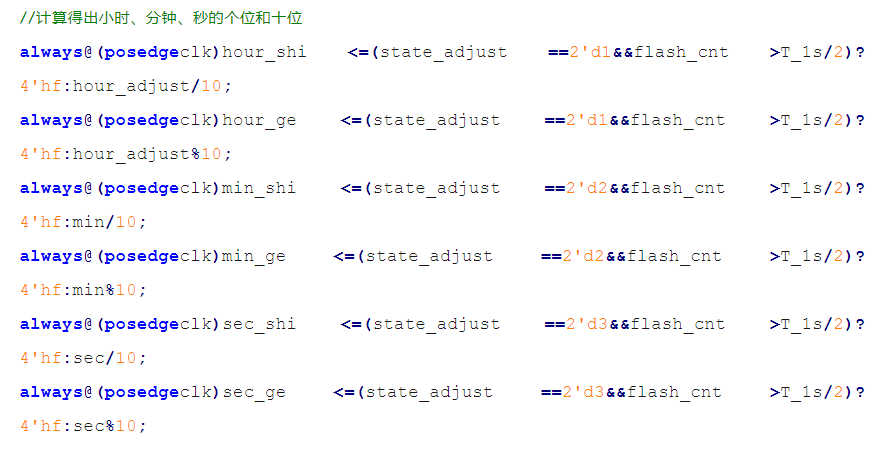

在正常模式下将需要显示的时、分、秒的十位和个位计算出来。在对应的调整模式下,需要前半秒输出对应的数字,后半秒输出全F。在数码管驱动中,当输入正常数字0~9显示数字,当输入F时数码管熄灭,此时数码管就闪烁起来了。

所有的逻辑在复位时,可以给予各种值,下板时,通过按下复位,可以让数字钟从自己想要的时间开始运行。

以上即为digital_clock_ctrl模块的设计思想;

七段数码管为普通六位一体的共阳极数码,采用动态驱动的方式,在此不再赘述。

下板后(下板成功,按下复位并释放,复位的时间设置为上午11时59分50秒),我们就可以看到数字钟的运行情况。

当然我们也可以使用按键进行调节到我们想要的任何时间点。

下板后,led1点亮(24小时制),经过10秒后,可以看到12时0分0秒。

下板后,演示视频(链接)如下:

https://www.bilibili.com/video/BV1FT4y1x7RQ/?vd_source=b5405faeab8632f02533bcbfc5e52e55

本设计所有内容(设计代码、设计工程)链接为:

链接:https://pan.baidu.com/s/1Bo6GK1bm1vDXfahwZusKVg

提取码:i9xj

本篇内容中有部分资源来源于网络,如有侵权,请联系作者。

更多的内容可以关注作者的其他博客,也可以关注微信公众账号:郝旭帅电子设计团队

基于FPGA的数字钟设计---第三版---郝旭帅电子设计团队的更多相关文章

- 基于FPGA的数字识别的实现

欢迎大家关注我的微信公众号:FPGA开源工作室 基于FPGA的数字识别的实现二 作者:lee神 1 背景知识 1.1基于FPGA的数字识别的方法 通常,针对印刷体数字识别使用的算法有:基于模版 ...

- FPGA经典:Verilog传奇与基于FPGA的数字图像处理原理及应用

一 简述 最近恶补基础知识,借了<<Verilog传奇>>,<基于FPGA的嵌入式图像处理系统设计>和<<基千FPGA的数字图像处理原理及应用>& ...

- 基于FPGA的数字秒表(数码管显示模块和按键消抖)实现

本文主要是学习按键消抖和数码管动态显示,秒表显示什么的,个人认为,拿FPGA做秒表真是嫌钱多. 感谢 感谢学校和至芯科技,笔者专业最近去北京至芯科技培训交流了一周.老师的经验还是可以的,优化了自己的代 ...

- c语言程序与设计第三版-苏小红--第一轮学习笔记、难点整理

---恢复内容开始--- 1> 编程:需求分析.设计.编写程序(编码.编辑.链接.运行).调试程序 2> 指数形式:e的左边是数值部分(有效数字),不能省略,但可以表示成 .e-4:等等: ...

- 光源 材质 简析——基于《real time rendering》第三版 第五章

对于真是世界的渲染,有三个重要的组成部分,光源,材质,以及摄像机.下面,我们一个一个来简单介绍一下. 光源:方向光,点光源,聚光灯.但是,在和物体表面交互的时候,光源对物体表面的影响是依赖光的辐照度( ...

- 读Javascript高级程序设计第三版第六章面向对象设计--创建对象

虽然Object构造函数或者对象字面量都可以用来创建单个对象,但是缺点非常明显:使用同一接口创建很多对象,会产生大量重复代码. 工厂模式 1 function CreatePerson(name,a ...

- 卷积神经网络应用于tensorflow手写数字识别(第三版)

import tensorflow as tf from tensorflow.examples.tutorials.mnist import input_data mnist = input_dat ...

- 基于FPGA的中值滤波算法实现

在这一篇开篇之前,我需要解决一个问题,上一篇我们实现了基于FPGA的均值滤波算法的实现,最后的显示效果图上发现有一些黑白色的斑点,我以为是椒盐噪声,然后在做基于FPGA的中值滤波算法的实验时,我发现黑 ...

- 基于FPGA的Sobel边缘检测的实现

前面我们实现了使用PC端上位机串口发送图像数据到VGA显示,通过MATLAB处理的图像数据直接是灰度图像,后面我们在此基础上修改,从而实现,基于FPGA的动态图片的Sobel边缘检测.中值滤波.Can ...

- 基于FPGA的肤色识别算法实现

大家好,给大家介绍一下,这是基于FPGA的肤色识别算法实现. 我们今天这篇文章有两个内容一是实现基于FPGA的彩色图片转灰度实现,然后在这个基础上实现基于FPGA的肤色检测算法实现. 将彩色图像转化为 ...

随机推荐

- Linux 下 C语言 open() 和 fopen() 区别

Linux 下 C语言 open() 和 fopen() 区别 fopen() #include <stdio.h> FILE *fopen(const char *path, con ...

- jdk-14.0.1环境搭建及cmd环境编译执行

1.安装包获取 https://www.oracle.com/java/technologies/javase/jdk14-archive-downloads.html 2.环境变量配置 最新版本的J ...

- studio

- ndk开发之native层访问java层

一.native层访问java层的成员变量 java层的成员变量可以分为实例变量和静态变量,不过他们的访问方法比较类似,可以分为以下三步: 获取java类对应的jclass对象 获取需要访问的成员变量 ...

- [ABC202E] Count Descendants 题解

Count Descendants 题目大意 给定一颗以 \(1\) 为根的树,多次询问求某点的子树中深度为给定值的点的个数. 思路分析 对于每个深度开一个 vector,从大到小存下这个深度的所有点 ...

- ES6入门(一)

1.let声明的变量只在let命令所在的代码块内有效 2.不存在变量提升,先使用变量,后定义变量,就会报错. 3.let不允许在相同作用域内,重复声明同一个变量.

- 人工智能AI浪潮的掀起,打工人何去何从?

感谢你阅读本文 自从2022年11月30日OpenAI公司推出了ChatGPT,至今一年了,而这一年国内也发生了天翻地覆的变化,各大厂商纷纷推出了自己的大模型和解决方案,例如百度的文心一言,阿里的通义 ...

- 空地一体化网络综述_Space-Air-Ground Integrated Network: A Survey

摘要 空地一体化网络(SAGIN)主要解决的是单一网络下的局限性问题,此综述文章从网络设计.资源分配.到性能的优化,对近几年SAGIN的总结. 引言 受限于网络容量和覆盖范围,仅依靠地面通信系统无法在 ...

- 使用 Jenkins + Github + dokcer-compose 部署项目-实战篇

使用 Jenkins + Github + dokcer-compose 部署项目-实战篇 需要声明的一点是,此处实现的项目自动构建原理是 Github+Jenkins 的 webhook,因此得保证 ...

- Vue源码学习(十四):diff算法patch比对

好家伙, 本篇将会解释要以下效果的实现 1.目标 我们要实现以下元素替换的效果 gif: 以上例子的代码: //创建vnode let vm1 = new Vue({data:{name:'张三' ...