用FPGA对ASIC进行原型验证的过程(转)

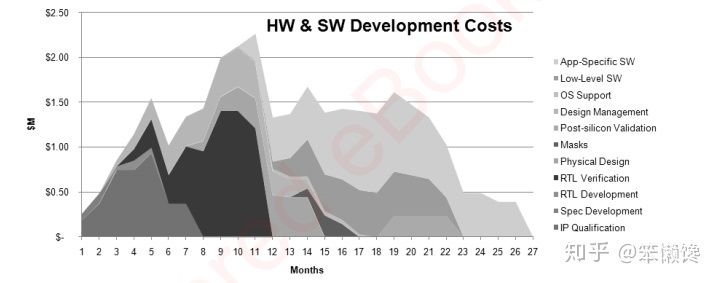

鉴于芯片设计的复杂度提升, 成功设计一个芯片所牵扯的步骤与过程也愈加复杂,所需花费的资金也成倍增加,一个典型的芯片开发项目的周期和花销如下所示

可以见到在芯片制造出来之前,很多精力会花费在RTL代码验证工作上,另外软件的相关开发工作,也会在得到芯片前开始,这2方面都需要借助FPGA原形来模拟芯片的行为,帮助硬件开发和软件开发者,共同提升工作效率。

FPGA原型在数字芯片设计中,基本是必不可少的,原因非常明显,相比用仿真器,或者加速器等来跑仿真,FPGA的运行速度,更接近真实芯片,可以配合软件开发者来进行底层软件的开发。当然FPGA原型作为芯片的替身,也是有诸多限制的,比如规模限制,速度限制,功耗限制,结构限制等,在使用FPGA原型作为芯片的替代时,需要进行相应的修改,才能完成相应功能,甚至有些功能最终无法覆盖。

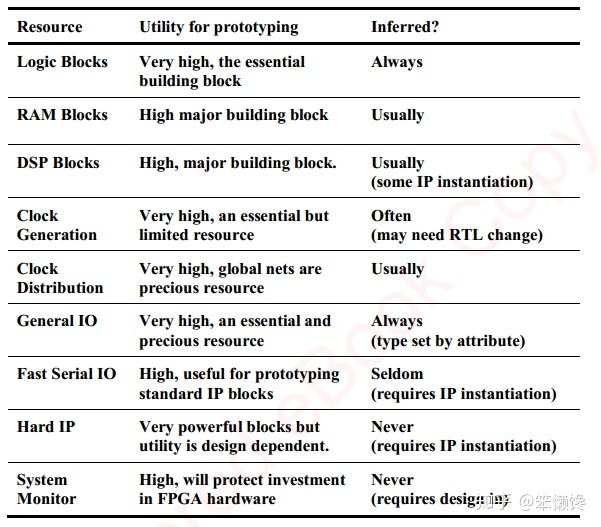

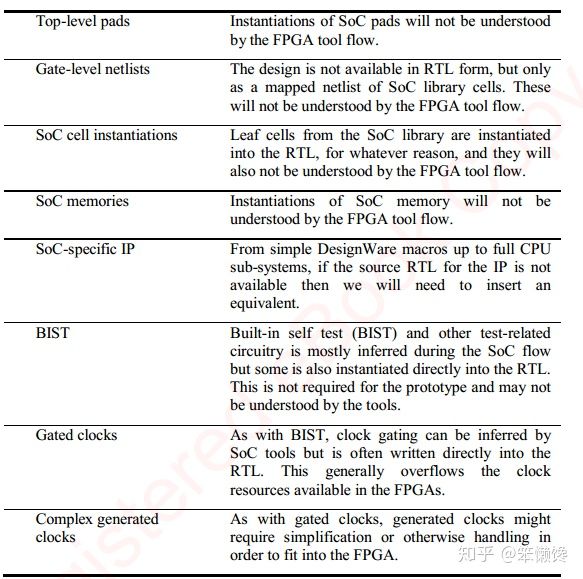

如果对FPGA中可以映射为ASIC的资源做逐一对比,我们可以得到这样的表格。

以上表格看出,除了普通的RTL逻辑以及基本端口,其他的类似存储时钟DSP等,最好都是做手动修改进行映射,把ASIC设计转换为FPGA比较靠谱。

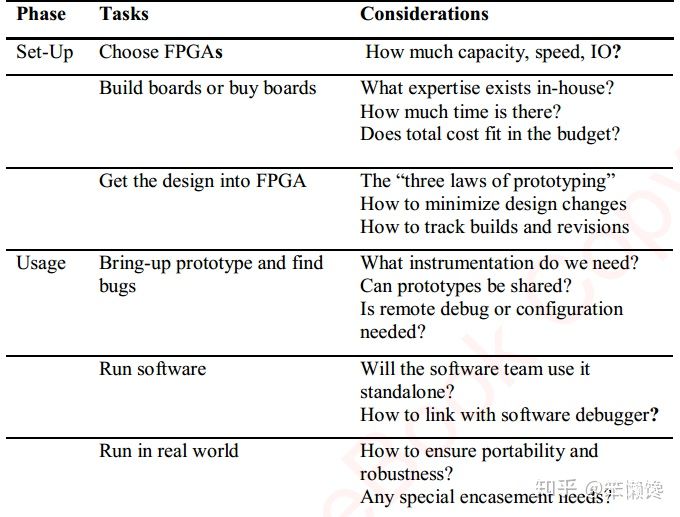

要把一块ASIC做出FPGA的原型,需要大致一下步骤,

1 FPGA选型

2 做板或者购买原型板。

3 将ASIC设计转换装入FPGA

4 调试启动FPGA原型

5 载入软件协同运行

6 软硬件系统验证

下文就按照这些步骤逐一讨论:

第一个就是FPGA的选型问题,在选型前,当然需要对ASIC的设计进行大致的了解,包括以下各方面:

选型问题最关心的几个维度:

1 容量 其中包括纯逻辑容量,存储容量,dsp单元容量这些

2 内置IP 包括时钟,存储控制,cpu等的硬核

3 接口 普通接口与专用高速接口

4 速度 资源占用率在50%左右时的速度,一般被用来评估原型

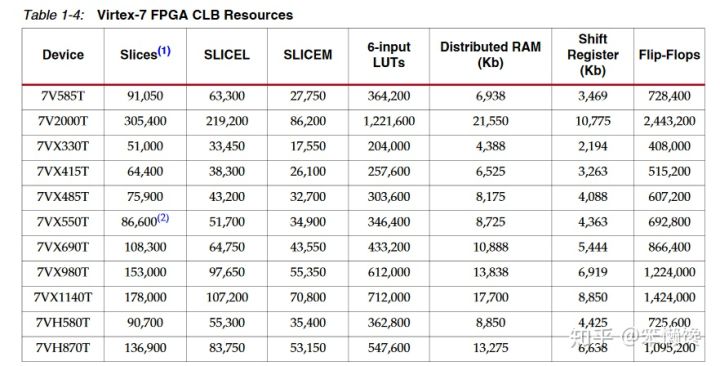

其中纯逻辑容量,也就是ASIC中组合电路与触发器的容量,是可以直接与FPGA中的资源换算的。

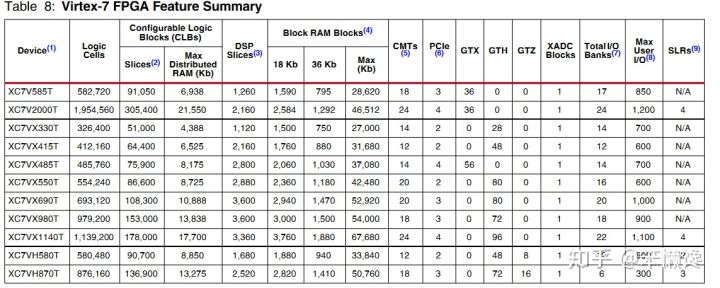

比如上图xilinx V7 2000T中有2.4M FF,大致对应ASIC的2输入与非门10M gates,如果使用率按照50%算,大概放置5M逻辑门没问题。

内置的存储器,可以实现21M的单双端口ram,rom,fifo等,如果ASIC中使用的存储稍微多一点,也可以用lut实现部分的存储,替代block ram。

如果使用较多乘加运算,也可以映射fpga中的dsp器件实现,具体各种型号的FPGA包含多少器件,可以参考xilinx文档。

对于内置ip,最先要考虑的,就是时钟模块MMCM,一般FPGA会有几个到几十个时钟模块,例如下表2000T中包含24个CMTs,也就是24个PLL和MMCM,每组PLL和MMCM可以对一个时钟域的时钟进行分频倍频。一般ASIC会包含多个时钟域,每个时钟域至少需要一个CMTs对时钟进行操作,可以据此选择使用哪个FPGA器件。

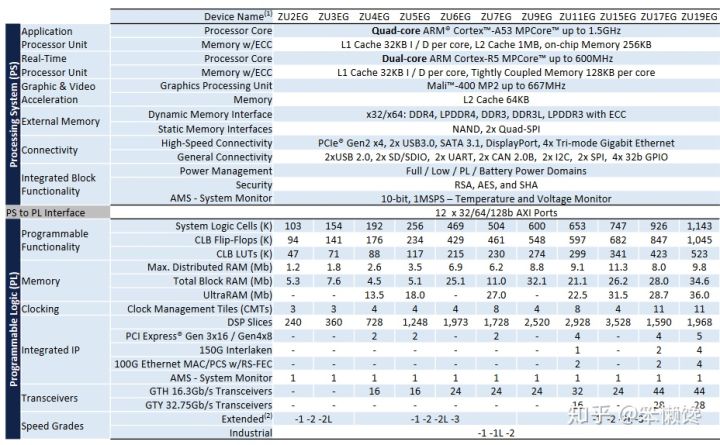

如要选择带有ARM硬核的FPGA来模拟ASIC中的ARM核,则需要选择zynq系列。系统中自研的逻辑,则通过AXI挂入总线中,当然这样未必能使FPGA与ASIC中的系统完全一致,但是作为一个圆形,也是足够的,以下是部分带有ARM核的FPGA的容量以及相应IP情况

对于接口的限制,一般FPGA的普通接口数量够大,不会成为瓶颈,主要在于ASIC所需的特定接口,在FPGA中是否能够满足,很多时候这些特定接口需要外接phy才能完成相应功能。

影响FPGA最终运行速度的因素很多,包括代码风格,具体设计,资源占用率,FPGA型号等,所以这需要在RTL代码基本框架完成后,通过工具综合才能得到一个大致数值,所以作为ASIC原型,尽量选择速度够快的FPGA。

通过以上限定条件,基本可以选出使用哪种FPGA型号,但是可能ASIC资源占用太多,任何一种都装不下,这就有2种解决方式了。一种是分块分别验证,当然这样风险极高,且没法直接验证最终系统。

另外就是使用多片FPGA得到原型,这就要涉及不同FPGA之中功能划分的问题,这个是比较麻烦且有难度的事情,对FPGA电路设计,以及ASIC到FPGA的代码转换,都有挺多新问题。

第2步就是制版,这需要考量的方面也是相当多,比如信号完整性,电源问题,时钟问题,可扩展性等,本人对此没有直接经验,也就无从展开。当然对于需要多个FPGA的验证板,一般实力的团队,未必能搞定,所以选择花钱买平安,直接选用类似HAPS这样的验证系统,可能更靠谱。

第3步就是ASIC的设计装入FPGA。这需要对原本面向ASIC的代码,进行修改。

对于一般的纯RTL逻辑,在ASIC中与FPGA中都可以综合出可用结果,但是以下表中的器件,需要修改

芯片中的pad,一般是fab厂给出的硬核,具有输入输出,驱动上下拉控制等。在转换成FPGA时,一般会在例化中直接用assign替代,并.XDC或者.v中指定上下拉等

如果有ASIC门级网表,可以把底层ASIC实例器件用verilog行为描述替换,在FPGA综合中则可以对应实现。其他的简单cell例化,也可以这样转换一下。

对于存储器,一般可以在FPGA中找到与ASIC功能一致的SRAM,ROM ,可以直接把FPGA MEM 外包一层改变端口名字,替代ASIC MEM。小的嵌入flash,则可以把FPGA的SRAM包一层逻辑来模仿。

其他的硬核IP, 可能需要在FPGA中寻找功能一致的,并相应修改接口,与ASIC代码中其他部分有效连接。

对于BIST,最直接的办法是去除,一般不会影响实际功能。

对于各种门控时钟,倍频分频等,一般需要针对FPGA做手动修改,使用DCM完成与芯片中时钟一致的行为。

以下就一些修改中会出现的具体问题,详细说明。

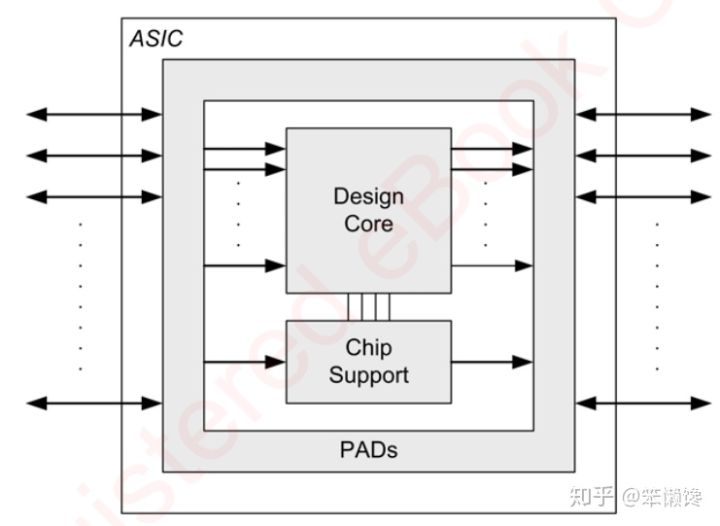

首先我们拿到的ASIC设计的结构,基本如下图所示,最外一圈是各种pad ring,里边先是芯片的各种辅助功能,包括 clk, rst, power, test,debug等。然后是与芯片实际功能相关的部分,可能包括部分模拟电路,数字电路包括cpu,mem 总线,各种逻辑控制等。我们需要明确用FPGA来原形验证的,主要是数字电路中的那些核心功能,芯片核心外部的那些辅助逻辑,很多是需要修改的,也是无法得到验证的。这里的pad一般直接在FPGA中直接去例化一个包含几个assign语句的 FPGA PAD 等效实例,clk rst 需要根据具体上电顺序,时钟资源做调整,一般会对rst功能进行简化,做成一个全局复位,clk中的分频与关断功能会放在CMT中实现。power控制,一般在FPGA中直接忽略,因为用FPGA几乎无法模拟各种UPF指定的行为。debug test可以根据实际情况保留或者去除,但是即使保持,一般也不会真的去用。核心功能中需要更改的,一般就是各种内部存储器了。

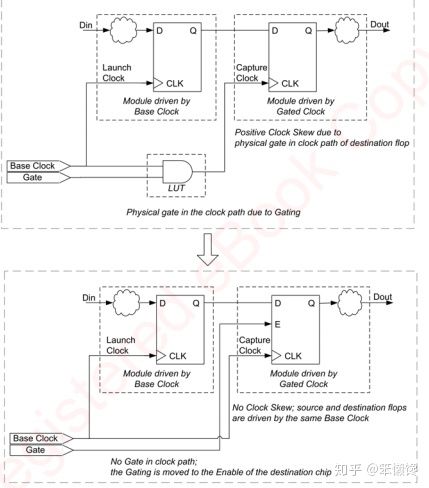

时钟门控 clock gating 一般在ASIC中广泛使用,一般会在clk模块中例化成由latch与门组成的门控单元,对某个模块进行时钟控制。这些门控单元,如果直接在FPGA中例化为相同逻辑的latch与门,逻辑功能是没有问题的。但是这时与门出来的受控时钟,则不能再FPGA的专用时钟网络中走线,而是走普通的信号网络,这样FPGA能达到的频率很差。为了纠正这样情况,可以把对寄存器的门控,放在寄存器端,也就是选用FPGA中行如FDCE这样带门控的寄存器。这个过程可以手动完成,但是比较麻烦,一般来说专门的FPGA综合工具能做这种自动转换。比如 vivado中使用 (* gated_clock = "true" *) input clk_a; 标定受控时钟,并在脚本加入 -gated_clock_conversion on 综合选项。

当然如果需要的可控时钟不太多,也就是少于FPGA中BUFGCE的数量,则可以直接把门控信号加在 BUFGCE的控制端,输出就是走时钟网络的门控信号了。如果FPGA器件中有 BUFHCE,则可以对更多层级的时钟进行门控,也就可以得到更多的受控时钟。

有关FPGA门控时钟的更详细解释,可以参照 https://forums.xilinx.com/t5/General-Technical-Discussion/Reg-Clock-gati...

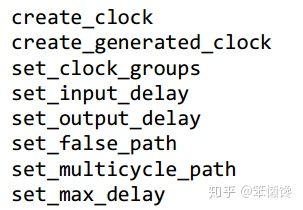

ASIC转变到FPGA使用的综合约束,在SDC与XDC基本相容,例如

这些都可以直接使用,当然很多情况下FPGA还是不可能跑到ASIC速度,必须降速运行。另外还需要添加FPGA中对管脚位置,类型,驱动强度等的约束,以及一些综合选项

以上即为对ASIC代码更改的主要部分,在下到FPGA板调试前,最好对更改的FPGA代码进行仿真,确认功能正常,减少上板调试的工作量。

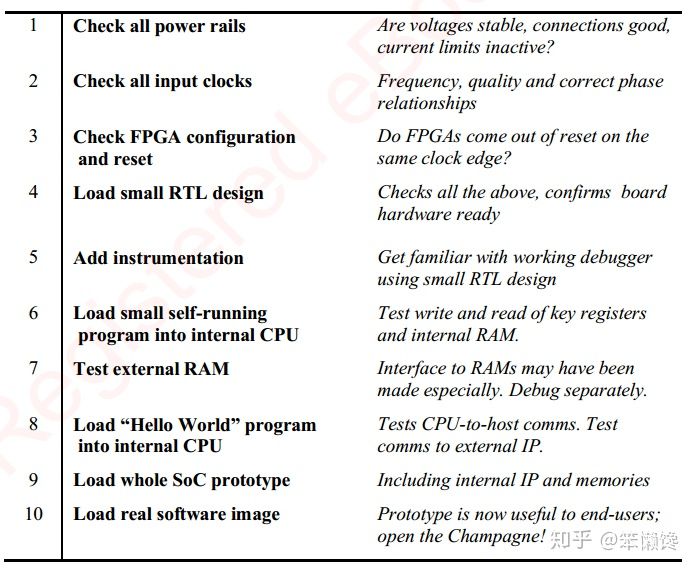

第4步为启动调试FPGA原型。

在把修改后的FPGA代码装入调试前,先需要保证FPGA板本身是正常可用的,这时如果是外购的开发板或者类似haps的验证系统,则会省去一些麻烦。

如果是头次开发的FPGA板,则需要先装入一个最简单的FPGA镜像文件,测试一下FPGA的电源供电,下载连接是否可用,然后通过几个用于测试的FPGA文件,测试下板上与FPGA连接的其他器件是否正常工作。一般头次设计的板子,多少会有各种问题,比如电源供电问题,管脚连接的差分信号匹配问题,阻抗匹配,电流驱动,信号质量等问题 如果板子通过了以上测试,则可以认为电路硬件设计没有问题,可以装入FPGA原形文件进行测试了。

装入修改了的FPGA原型模拟ASIC,一般不会一次成功,一般出现的问题可以分为以下三类:

1 RTL逻辑错误,包括原本ASIC既有的和修改过程引入的错误。

2 接口错误 与外部器件的电信号连接错误,包括电压不匹配,驱动电流不一致等。

3 软件错误 MCU运行的软件没有正确配置相关功能导致,这种一般在仿真中难以发现,因为仿真很少运行真正的软件系统。

对fpga原型的板上调试,可以归纳为以下步骤。

当载入实际运行的软件后,通过FPGA原型,就可以如同在实际芯片中一样,对软件进行测试修改,同时完成系统级的验证工作了。也就进入了步骤5.6,这与普通的嵌入式软件开发大致相同。

对于通过FPGA进行原型验证,有以下设计流程上的建议,值得参考

以上参考了xilinx网站内容,以及FPMM等书。

用FPGA对ASIC进行原型验证的过程(转)的更多相关文章

- SOC芯片的FPGA原型验证

FPGA验证在SOC设计非常重要,一般而言,做一些RAM和FIFO的替换以及相应代码转换.具体分下面几步: 1 替换RAM,FIFO和时钟 RAM和FIFO控制器需要RAM的接口都放在了设计顶层,方便 ...

- FPGA原型验证

为什么要做FPGA原型验证? FPGA原型验证可以在IC流片前对芯片功能和性能做出评估,同时,可以给软件设计人员提供验证平台.所有的设计,无论是SOC还是ASIC都需要被验证(功能和时序验证),以确保 ...

- FPGA与ASIC:它们之间的区别以及使用哪一种?

FPGA与ASIC:它们之间的区别以及使用哪一种? FPGA Vs ASIC: Differences Between Them And Which One To Use? VL82C486 Sing ...

- ASIC 前端功能验证等级与对应年薪划分[个人意见] (2011-07-04 15:33:35

下面的讨论转载自eetop,我选取了一些有意义的讨论,加了我的评注. 楼主zhhzhuawei认为 ===================================== 对于ASIC的前端功能验 ...

- 深度学习硬件:CPU、GPU、FPGA、ASIC

人工智能包括三个要素:算法,计算和数据.人工智能算法目前最主流的是深度学习.计算所对应的硬件平台有:CPU.GPU.FPGA.ASIC.由于移动互联网的到来,用户每天产生大量的数据被入口应用收集:搜索 ...

- FTS抓包看蓝牙验证的过程

1.概述 在进行蓝牙设备的连接时,为了保护个人隐私和数据保密的需要,需要进行验证. 2.一些Frame Frame74:本地发送Authentication requset command ...

- EDA技术与ASIC设计和FPGA开发有什么关系?FPGA在ASIC设计中有什么用途?

利用EDA技术进行电子系统设计的最后目标是完成专用集成电路ASIC的设计和实现:FPGA和CPLD是实现这一途径的主流器件.FPGA和CPLD通常也被称为可编程专用IC,或可编程ASIC.FPGA和C ...

- POC测试——原型验证,降低风险,IT系统销售工作之一

POC测试,即Proof of Concept,是业界流行的针对客户具体应用的验证性测试,根据用户对采用系统提出的性能要求和扩展需求的指标,在选用服务器上进行真实数据的运行,对承载用户数据量和运行时间 ...

- 【Spring源码分析】原型Bean实例化过程、byName与byType及FactoryBean获取Bean源码实现

原型Bean加载过程 之前的文章,分析了非懒加载的单例Bean整个加载过程,除了非懒加载的单例Bean之外,Spring中还有一种Bean就是原型(Prototype)的Bean,看一下定义方式: & ...

随机推荐

- Getting started with Processing 第六章总结

平移,旋转和缩放 前言 在这一章节中,平移.旋转和缩放都是以原点为基准的.并且是通过控制坐标系原点的位置来达到图元平移,旋转.缩放的视觉效果.作者在文中的原话是:另一种在屏幕上改变位置和移动物体的技术 ...

- 【简单易懂】JPA概念解析:CascadeType(各种级联操作)详解

https://www.jianshu.com/p/e8caafce5445 [在一切开始之前,我要先告诉大家:慎用级联关系,不要随便给all权限操作.应该根据业务需求选择所需的级联关系.否则可能酿成 ...

- canvas绘图在手机上边缘粗糙

辛辛苦苦用canvas绘图,做好动画后,想看看效果,结果在手机上一打开,效果是有了,但是边缘特别粗糙,这怎么可以呢,有一种说法是你用canvas绘图时候在手机retain屏幕上,他把一个像素分为两个像 ...

- centOS 6.5安装python和nginx

一.安装python3.5 1.安装python3.5

- Confluence 6 如何保持我空间的整洁

如果你有很多用户在同一个空间中编辑和创建内容,你的空间将会很快的变得混乱不堪.你可以使用下面的一些步骤来避免这个的发生. 创建一系列的指南 让你的合作编辑用户知道创建页面的上级页面是什么,这样可以保证 ...

- sqlserver给指定用户授权访问指定表

一. 背景 外部公司的人授权访问我们公司的数据库,数据接口调用,要给他们建立查看指定的视图和授权的账号,因此要在数据库中,给指定用户授权访问指定表 二.sqlserver 脚本 ---创建视图CR ...

- Codeforces Round #250 (Div. 1)E. The Child and Binary Tree

题意:有一个集合,求有多少形态不同的二叉树满足每个点的权值都属于这个集合并且总点权等于i 题解:先用生成函数搞出来\(f(x)=f(x)^2*c(x)+1\) 然后转化一下变成\(f(x)=\frac ...

- leetcode-algorithms-11 Container With Most Water

leetcode-algorithms-11 Container With Most Water Given n non-negative integers a1, a2, ..., an , whe ...

- 安卓——BroadcastReceiver

package com.example.administrator.myapplication_reciver; import android.content.BroadcastReceiver; i ...

- poj-2154-polya+euler函数

Color Time Limit: 2000MS Memory Limit: 65536K Total Submissions: 11758 Accepted: 3783 Descriptio ...