Tcl写法

#===============================================================

#Analysi&Synthesis

execute_module -tool map

#===============================================================

#Fitter(Place&Route)

execute_module -tool fit

#===============================================================

#Assembler(Generate programming files)

execute_module -tool asm

set make_assignments 0

if { $make_assignments } {

set_global_assignment -name FAMILY "Cyclone V"

set_global_assignment -name DEVICE 5CEFA5F23I7

set_global_assignment -name TOP_LEVEL_ENTITY altera_wireless_top

set_global_assignment -name RESERVE_ALL_UNUSED_PINS_WEAK_PULLUP "AS INPUT TRI-STATED"

set_global_assignment -name EDA_SIMULATION_TOOL "ModelSim (Verilog)"

#添加verilog文件

set_global_assignment -name VERILOG_FILE hb_i2_5m_4ch_16x.v

set_global_assignment -name QIP_FILE fir_23p04_4x_linux_ipv2/fir_23p04_4x_linux_ip.qip

set_global_assignment -name SIGNALTAP_FILE ad_test0806v2.stp

set_global_assignment -name TEXT_FILE output_files/stp1_auto_signaltap_0.txt

##===============SYSCLK=============================================================================

set_location_assignment PIN_M8 -to clk_n

set_location_assignment PIN_M9 -to clk_p

set_instance_assignment -name IO_STANDARD "DIFFERENTIAL 2.5-V SSTL CLASS II" -to clk_n

set_instance_assignment -name IO_STANDARD "DIFFERENTIAL 2.5-V SSTL CLASS II" -to clk_p

}

感觉TCL中if else语句在用的时候是注意空格间隔等问题的,如果执行过程报错,就严格按下面的写法来用。

set broken 0

if { $broken } {

puts "failure -- exit status $broken"

exit -code $broken

} else {

puts "success"

}

/*********************************************************************************/

1、设置路径

cd命令用于更改modelsim的路径,如果仿真正在执行cd命令无效;如果找开了一个工程,那cd命令会关闭当前的工程

语法:cd <dir>

eg:cd e:/fpga

/*********************************************************************************/

2、alias 显示和建立用户定义的别名,有点相当于c语言中的“宏定义”

Syntax

alias [<name> ["<cmds>"]]

当cmds为多组命令时用”;“分开,并且用双引号

eg: alias ld "dev_com;com;elab"

eg2:

alias dev_com {

if [ string match "*ModelSim*" [ vsim -version ] ] {

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_primitives.v" -work altera_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/220model.v" -work lpm_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/sgate.v" -work sgate_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_mf.v" -work altera_mf_ver

vlog -sv "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/altera_lnsim_for_vhdl.sv" -work altera_lnsim_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/cyclonev_atoms_ncrypt.v" -work cyclonev_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/cyclonev_hmi_atoms_ncrypt.v" -work cyclonev_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/cyclonev_atoms_for_vhdl.v" -work cyclonev_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/cyclonev_hssi_atoms_ncrypt.v" -work cyclonev_hssi_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/cyclonev_hssi_atoms_for_vhdl.v" -work cyclonev_hssi_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/cyclonev_pcie_hip_atoms_ncrypt.v" -work cyclonev_pcie_hip_ver

vlog "$QUARTUS_INSTALL_DIR/eda/sim_lib/mentor/cyclonev_pcie_hip_atoms_for_vhdl.v" -work cyclonev_pcie_hip_ver

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_syn_attributes.vhd" -work altera

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_standard_functions.vhd" -work altera

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/alt_dspbuilder_package.vhd" -work altera

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_europa_support_lib.vhd" -work altera

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_primitives_components.vhd" -work altera

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_primitives.vhd" -work altera

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/220pack.vhd" -work lpm

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/220model.vhd" -work lpm

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/sgate_pack.vhd" -work sgate

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/sgate.vhd" -work sgate

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_mf_components.vhd" -work altera_mf

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_mf.vhd" -work altera_mf

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/altera_lnsim_components.vhd" -work altera_lnsim

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/cyclonev_atoms.vhd" -work cyclonev

vcom "$QUARTUS_INSTALL_DIR/eda/sim_lib/cyclonev_components.vhd" -work cyclonev

}

}

这样的话,在modelsim的命令窗输入dev_com,就会执行所有的编译文件命令。

/*********************************************************************************/

echo 在脚本框中输出指定的内容

Syntax

echo [<text_string>]

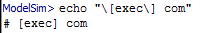

如上图,在modelsim的命令行中输入ech "\exec\] com" 就会输出 #[exec] com,其实就相关于matlab 中的output命令

/*********************************************************************************/

eidt

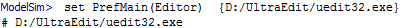

上面的命令用于设置modelsim的文件编辑器

Syntax

edit [<filename>]

[<filename>]用于指定要编辑文件的名字

在命令窗中输入help

可以看到哪些Tcl包已经下载,哪些还没有。Loaded表示已经下载,Not Loaded表示还没有下载

输入help –tcl

输入 help flow如下:

Tcl写法的更多相关文章

- modelsim如何使用tcl脚本来写编译文件

对于modelsim进行仿真,可以通过GUI来进行仿真,当然更加快速的方法可以使用TCL脚本文件进行快速仿真. Modelsim采用TCL脚本文件仿真的具体流程如下所示: 具体的操作步骤如下 ...

- 常用命令 tcl & shell

TCL 常用命令: 1. 当前时间 [exec date +%m%d_%H%M] (实际是调用shell命令 date),比如在 icc 中保存cell 时可以用:save_mw_cel ...

- 状态机的Verilog写法

“硬件设计很讲究并行设计思想,虽然用Verilog描述的电路大都是并行实现的,但是对于实际的工程应用,往往需要让硬件来实现一些具有一定顺序的工作,这就要用到状态机思想.什么是状态机呢?简单的说,就是通 ...

- obj.style.z-index的正确写法

obj.style.z-index的正确写法 今天发现obj.style.z-index在js里面报错,后来才知道在js里应该把含"-"的字符写成驼峰式,例如obj.style.z ...

- java设计模式之单例模式(几种写法及比较)

概念: Java中单例模式是一种常见的设计模式,单例模式的写法有好几种,这里主要介绍三种:懒汉式单例.饿汉式单例.登记式单例. 单例模式有以下特点: 1.单例类只能有一个实例. 2.单例类必须自己创建 ...

- .NET跨平台之旅:数据库连接字符串写法引发的问题

最近在一个ASP.NET Core站点中遇到一个奇怪问题.当用dotnet run命令启动站点后,开始的一段时间请求执行速度超慢,有时要超过20秒,有时甚至超过1分钟,日志中会记录这样的错误: Sys ...

- 【兼容写法】HttpServerUtility.Execute 在等待异步操作完成时被阻止。关键词:MVC,分部视图,异步

异常处理汇总-后端系列 http://www.cnblogs.com/dunitian/p/4523006.html MVC6之前的版本,对分部视图的异步支持不是很好 问题: 视图里面有分布视图:@{ ...

- Tcl internal variables

Tcl internal variables eryar@163.com 在Tcl中内置了一些变量,并赋予了一定的功能.内置变量列表如下: 变量名称 功能描述 argc 指命令行参数的个数. argv ...

- 常用原生JS方法总结(兼容性写法)

经常会用到原生JS来写前端...但是原生JS的一些方法在适应各个浏览器的时候写法有的也不怎么一样的... 今天下班有点累... 就来总结一下简单的东西吧…… 备注:一下的方法都是包裹在一个EventU ...

随机推荐

- numpy linspace arange函数

linspace(start, end, num_of_points), 区间 [start, end],产生一个等差数列,差为:(end-start)/(num_of_point-1). arang ...

- jquery 阻止冒泡事件和阻止默认事件

jQuery 冒泡和默认事件: <!DOCTYPE html> <html lang="en"> <head> <meta charset ...

- 两个关于URL解析的例子

例一: /* 解析URL查寻串中的name=value参数对 将name=value对存储在对象属性中,并返回对象 alert(getQuery().name) */ function getQuer ...

- 由于C++类库版本不同导致的OpenCV编译链接错误

太长不看版:GCC4和GCC5使用的C++标准库下,string的名字不一样,导致链接错误. 之前在Ubuntu下使用OpenCV的时候一切正常.后来再次编译的时候,连接器提示有些库函数找不到: ma ...

- 判断是否有TrueType字体

function IsTrueTypeAvailable : bool;var {$IFDEF WIN32} rs : TRasterizerStatus; {$ELSE} rs : TRaste ...

- JAVA数据类型(转载)

JAVA中值类型的只有short,char,byte,int,long,double,float,boolean八大基本类型,其他的所有类型都是引用类型. 首先我们都知道在编程中赋值运算“=”的意思是 ...

- Group by 内部排序

1.right join # update_time gid=>sid, group_status => s_table select a.* from comment as a ri ...

- selenium -- 鼠标悬停

针对页面上的二级菜单,需要鼠标悬停才能进行操作. /** * Clicks (without releasing) in the middle of the given element. This i ...

- clamp 函数

返回范围内的一个数值.可以使用 clamp 函数将不断增加.减小或随机变化的数值限制在一系列的值中. float clamp(float minnumber, float maxnumber, flo ...

- Codeforces Beta Round#2

Codeforces Beta Round#2 http://codeforces.com/contest/2 A 模拟题 #include<bits/stdc++.h> using na ...