FPGA基础学习(5) -- 时序约束(实践篇)

距离上一篇有关时序的理论篇已经有一段时间了(可以参考博文FPGA时序约束——理论篇),实际上此段时间,甚至到今天对FPGA的时序一直还是处于一种“朦胧”的状态,经历了一个阶段的学习和项目时间,稍微有点感触,故借此总结一下。

1. 理论回顾

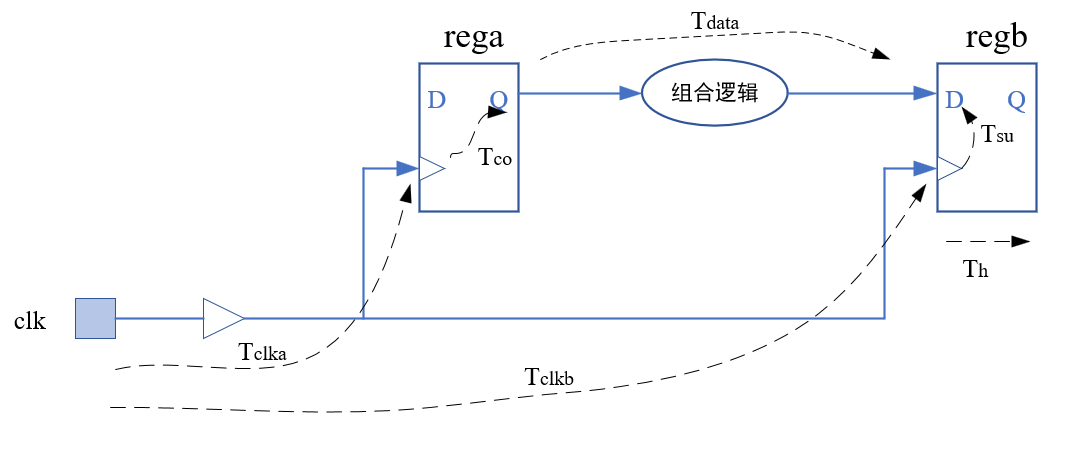

先来回顾一下有关时序的理论知识,上图是典型的同步时序模型及其时序图,由发起寄存器(rega)、组合逻辑、捕获寄存器(regb)及其中间的走线组成。

源时钟clk到达rega的时钟端口时,会有一定的延迟,从而形成clka。同理,时钟延迟到达regb的时钟端口,形成clkb。Tco为有效数据出现在发起寄存器Q端口所需时间。Tdata为数据延迟,包括组合逻辑延迟和走线延迟。Tsu表示捕获寄存器建立时间要求。Th表示捕获寄存器保持时间要求。其中Tco、Tsu和Th是由FPGA的芯片工艺决定的。所以,我们所谓的时序约束,实际上就是对时钟延迟和Tdata做一定的要求或者干预,其中Tdata由组合逻辑(代码)及布局布线决定,这也决定了系统最高的工作频率。

2. 时间裕量

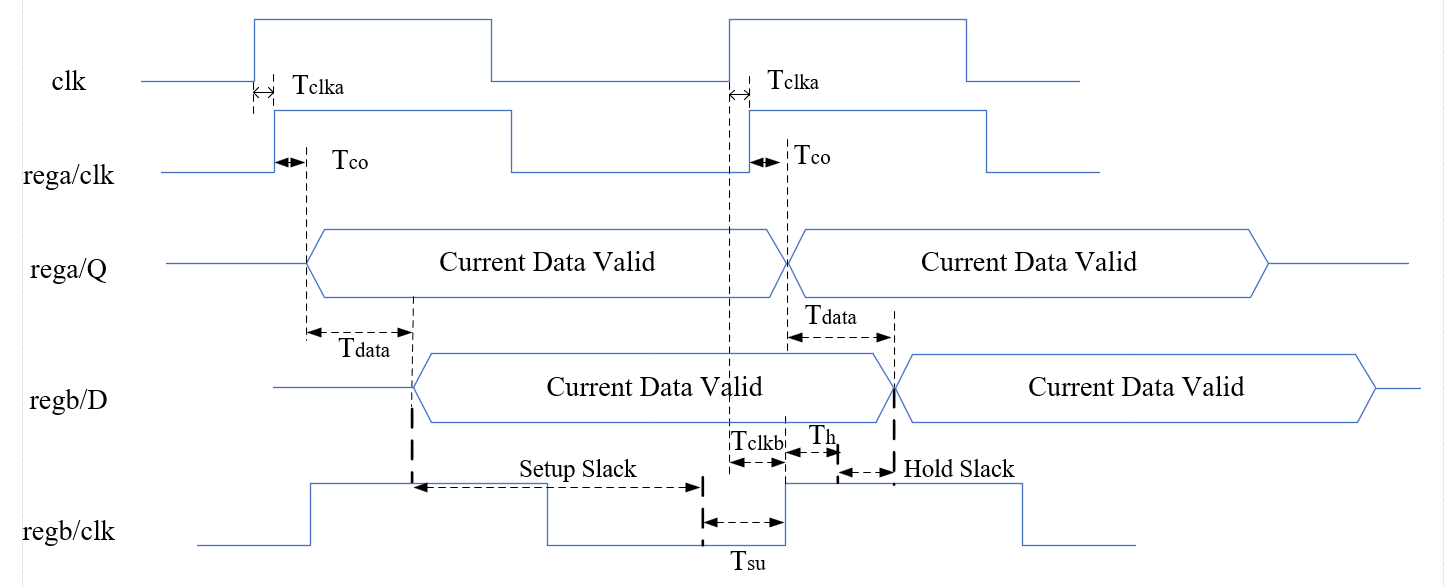

时间裕量包括建立时间裕量和保持时间裕量(上图中的setup slack和hold slack)。从字面上理解,所谓“裕量”即富余的、多出的。什么意思呢?即保持最低要求的建立时间或保持时间所多出的时间,那么“裕量”越多是不是就意味着时序约束越宽松呢?应该是这样的。

通俗的讲,一个FPGA工程在综合实现后,是否满足时序约束,其实就是看所有的捕获寄存器是否能正确稳定捕获到发起寄存器发出的数据。如上图所示,也就是说到达捕获寄存器的数据输入端口D(regb/D)的数据要满足建立和保持时间要求,也就是说在Tsu之前,current data valid就要准备就绪,而在Th之后呢,current data valid还要多维持一段时间。换言之,在Tsu之前以及Th之后多出的这部分时间,我们就称之为“裕量”,裕量越大,时序越宽松。裕量的大小与时钟频率、代码设计以及布局布线有着紧密的联系。一个设计的时序报告中,裕量为负数时,表示时序约束出现违例,虽然个别违例不代表你的工程就有致命的问题,但是这是一个风险(时序报告是按照工艺、电压以及温度的上下限给出的结果)。当违例数较多,也就意味着设计在实际环境中出现问题的概率也会越大。

3. 最大延迟和最小延迟

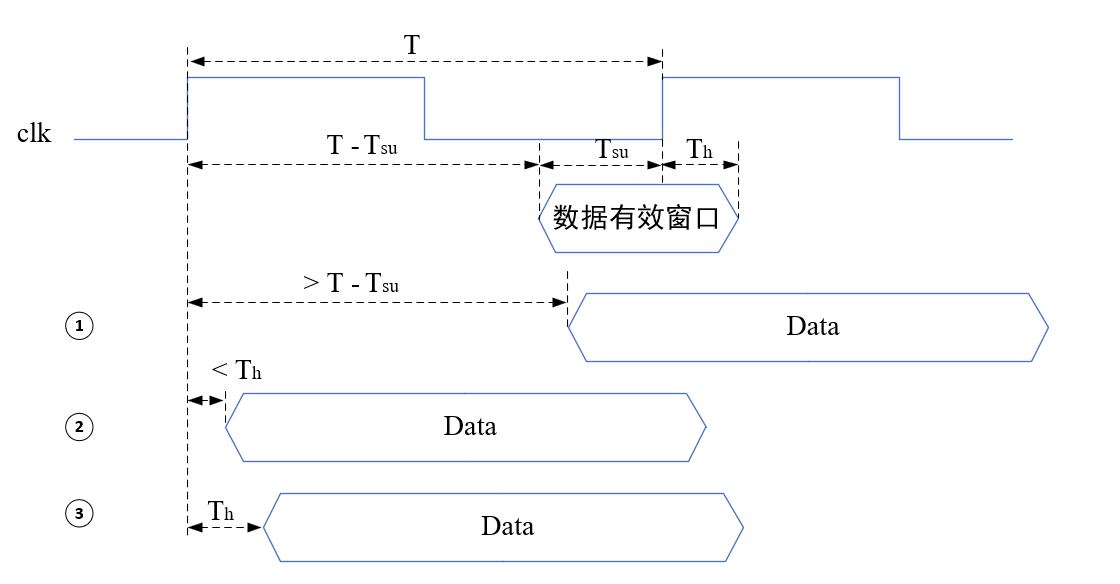

如下图所示,“数据有效窗口”表示捕获的数据满足建立时间和保持时间,在此窗口中要捕获的数据不能发生变化,否则将引起不稳定的结果。

我们来看1、2、3三种情况,在分析之前,首先要明确Data的持续时间长度一定是一个时钟周期(多周期打拍另说)。1:当延迟时间大于T-Tsu时,Data在建立时间区域内才到达regb,所以不满足建立时间要求,这就是说数据来的“太晚了”;2:当Data延迟了很小一段时间(<Th),Data在保持时间内就变化了,所以不满足保持时间,这就是说数据来的“太早了”。3:当Data延迟了Th,Data则满足建立时间要求又刚好满足保持时间要求,这就是说数据来的“正巧”。

综上所述,数据的最大延迟是T-Tsu,最小延迟是Th。一看是看到这儿有点纳闷,最大延迟我们还能理解,延迟太大,捕获不到数据,这是理所当然。延迟还有下限是什么意思?仔细看看文章开头的时序模型和时序图,实际生成的电路图之后,除了要满足Th的要求外,数据路径和捕获时钟路径肯定不太可能一定拥有相同的延迟,举个极端的例子,如果clkb延迟非常大,那么current data valid必须增加延迟才能保证被clkb捕获到。

一般而言,在综合之后,我们需要特别关注的是建立时间的时序违例,因为可以通过增加布线长度来保证保持时间。大多数保持时间违例在实现之后自然会被优化掉。

4. 案例分析

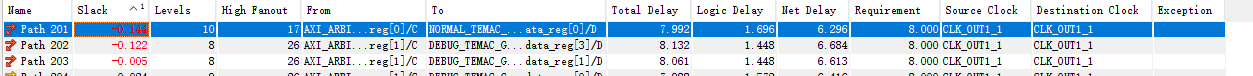

以下是在实际工程(VIVADO平台)中的时序分析结果:

如上图所示,综合后给出的时序报告,可以看到ADC的时钟出现了hold时序违例,clk_out1_1出现了setup违例。然后进行实现,实现完成后hold违例消失(正如上面所述,保持时间往往可以修改布线长度来保证),如下图所示为实现后的结果,目前只存在3条路径出现setup违例,即建立时间裕量为负。

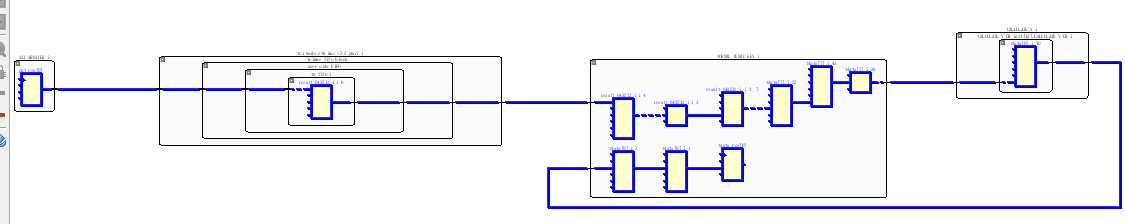

以path201为例:选中path201,按F4(或右键schematic),打开路径的原理图,如下图所示,可以看到该路径经历多个模块,时序路径较长。

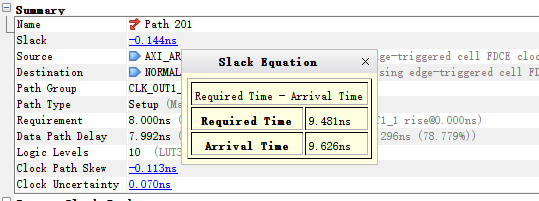

双击path201,会显示该路径的具体信息,点击slack可以弹出相应的需求时间和实际的到达时间,可以清晰的看到实际到达时间是长于需求时间的,所以出现时序违例的情况。

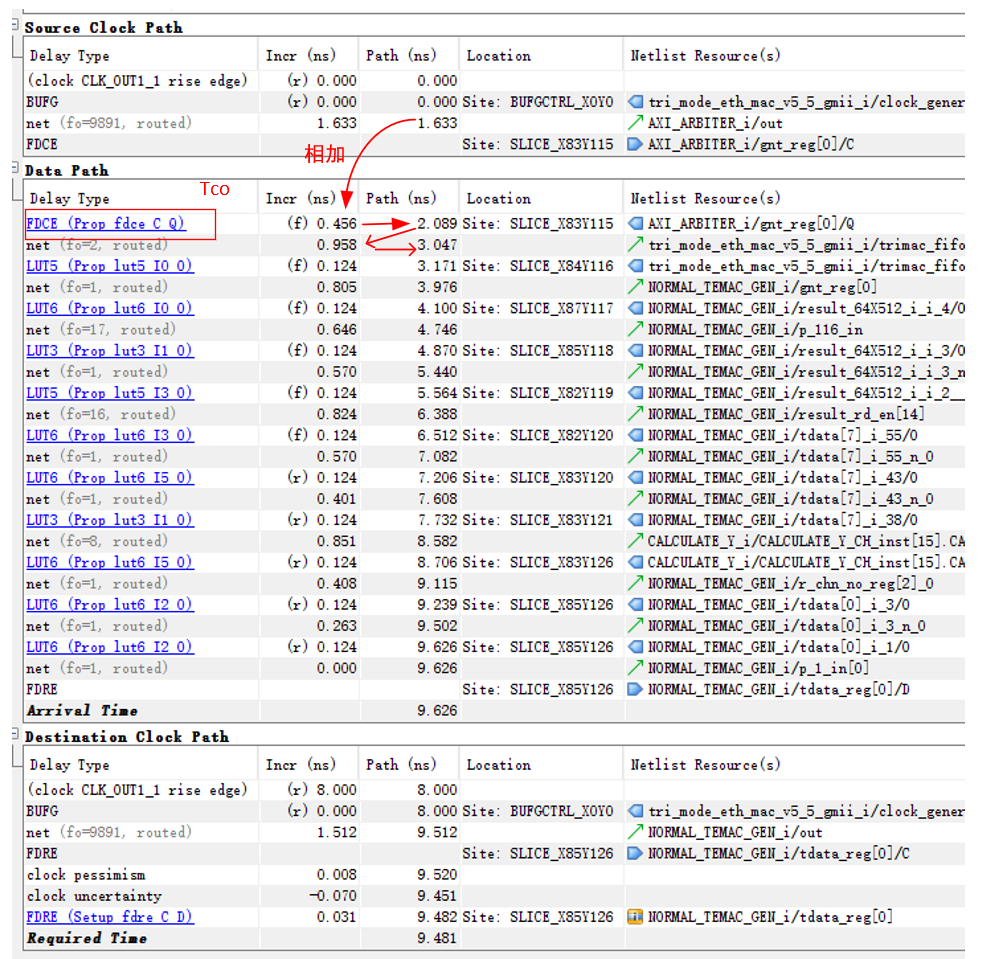

详细的原时钟时序、数据路径时序、目标时钟时序的各延迟数据如下图所示。值得注意的是数据路径信息,其中包括Tco延迟和布线延迟,各级累加之后得到总的延迟时间。通过观察各中间过程,分析其中延迟较大的环节,可以做相应的优化约束或代码有效。

一般而已,少量的时序违例(如本工程,只有3条路径违例),是可以通过实现策略(strategy)的修改达到要求。如果时序违例较严重,那么就需要详细的分析各时钟之间的关系(同步or异步)、是否分析该路径等各方面进行深刻的分析,然后修改时序约束文件,更严重的可能要手动布局及修改布线,我对这方面还理解的不是很透,所以等弄明白了再总结。

参考文献:

1.《VIVADO从此开始》——高亚军著(强烈推荐此书!!!!)

FPGA基础学习(5) -- 时序约束(实践篇)的更多相关文章

- FPGA基础学习(4) -- 时序约束(理论篇)

在FPGA 设计中,很少进行细致全面的时序约束和分析,Fmax是最常见也往往是一个设计唯一的约束.这一方面是由FPGA的特殊结构决定的,另一方面也是由于缺乏好用的工具造成的.好的时序约束可以指导布局布 ...

- FPGA基础学习(3) -- 跨时钟域处理方法

文章主要是基于学习后的总结. 1. 时钟域 假如设计中所有的触发器都使用一个全局网络,比如FPGA的主时钟输入,那么我们说这个设计只有一个时钟域.假如设计有两个输入时钟,如图1所示,一个时钟给接口1使 ...

- FPGA基础学习(9) -- 复位设计

目录 1. 常见问题 2. 常见的复位方式 3. 合理的复位设计 3.1 复位电平 3.2 异步复位同步化 3.3 恰到好处的复位 4. 补充 4.1 所谓的上电初始化 参考文献 一开始接触到FPGA ...

- FPGA基础学习(7) -- 内部结构之CLB

目录 1. 总览 2. 可配置逻辑单元 2.1 6输入查找表(LUT6) 2.2 选择器(MUX) 2.3 进位链(Carry Chain) 2.4 触发器(Flip-Flop) 参考文献: 一直以来 ...

- FPGA基础学习(6) -- 原语

目录 1. IBUF和IBUFDS(IO) 2. IDDR(Input/Output Functions) 3. IBUFG和IBUFGDS(IO) 原语,即primitive.不同的厂商,原语不同: ...

- FPGA基础学习(8) --内部结构之存储单元

目录 1. 基本结构 2. BRAM与DRAM的比较 3. BRAM的特点 4. Block Memory的使用 4.1 配置为RAM或ROM 4.2. 配置为FIFO 参考文献: 上一篇中提到了SL ...

- FPGA基础学习(2) -- FIFO IP核(Quartus)

ALTERA在LPM(library of parameterized mudules)库中提供了参数可配置的单时钟FIFO(SCFIFO)和双时钟FIFO(DCFIFO).FIFO主要应用在需要数据 ...

- FPGA基础学习(1) -- FFT IP核(Quartus)

为了突出重点,仅对I/O数据流为steaming的情况作简要说明,以便快速上手,有关FFT ip核模型及每种设置详细介绍请参考官方手册FFT MegaCore Function User Guide. ...

- 【转载】【时序约束学习笔记1】Vivado入门与提高--第12讲 时序分析中的基本概念和术语

时序分析中的基本概念和术语 Basic concept and Terminology of Timing Analysis 原文标题及网址: [时序约束学习笔记1]Vivado入门与提高--第12讲 ...

随机推荐

- AngularJS学习(一)

参考文章:http://blog.csdn.net/dc_726/article/details/17010325 1.HelloWorld篇 1.1 环境 下载:angular-1.2.5min.j ...

- PHP Curl请求Https接口

在请求http的时候只需要 file_get_contents("http://www.sojson.com/open/api/weather/json.shtml?city=$Positi ...

- 我的笔记,有关 PhotoShop,给自己的记忆宫殿

一直有心学习 PhotoShop ,各种教程也 download 了不少,什么祁连山.PS大师之路.Oeasy 等等.看了吗?丫蛋的只看了前面两集!还是在博客上写写坐下笔记,好记性不如烂笔头. 0.先 ...

- 公共技术点之 Java 反射 Reflection

本文摘录地址: http://codekk.com/open-source-project-analysis/detail/Android/Mr.Simple/%E5%85%AC%E5%85%B1%E ...

- 如何学习MySQL

转自高手的帖子 1.坚持阅读官方手册,看MySQL书籍作用不会特别大:(挑选跟工作相关的内容优先阅读,例如InnoDB存储引擎,MySQL复制,查询优化) 2.阅读官方手册,同时对阅读的内容做对应的测 ...

- linux ssh使用深度解析(key登录详解)

linux ssh使用深度解析(key登录详解) SSH全称Secure SHell,顾名思义就是非常安全的shell的意思,SSH协议是IETF(Internet Engineering Task ...

- Linux nethack

一.简介 游戏目标:在地下城的最底层取得炎多的护符项链(Amulet of Yendor),并返回最上层,在圣祭坛上供奉给神灵.完成整个游戏的奖赏是,玩家会成为不朽的半神. 二.安装 1)下载源码 ...

- 特征选择Boruta

A good feature subset is one that: contains features highly correlated with (predictive of) the clas ...

- Yii2邮箱发送与配置

1配置邮箱 在 common/config/web.php中写入以下代码配置 Mail代理 return [ 'components' => [ ...//your code, //以下是 ma ...

- rpmbuild SPEC语法

rpmbuild SPEC语法 摘自:http://bbs.chinaunix.net/thread-4179207-1-1.html spec文件写作规范 2008-09-28 11:52:17 分 ...