AXI总线简介

AXI全称Advanced eXtensible Interface,是Xilinx从6系列的FPGA开始引入的一个接口协议,主要描述了主设备和从设备之间的数据传输方式。在ZYNQ中继续使用,版本是AXI4,所以我们经常会看到AXI4.0,ZYNQ内部设备都有AXI接口。其实AXI就是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)的一个部分,是一种高性能、高带宽、低延迟的片内总线,也用来替代以前的AHB和APB总线。第一个版本的AXI(AXI3)包含在2003年发布的AMBA3.0中,AXI的第二个版本AXI(AXI4)包含在2010年发布的AMBA 4.0之中。

AXI协议具有如下特点:

. 总线的地址/控制和数据通道是分离的;

. 支持不对齐的数据传输;

. 在突发数据传输中只需要首地址;

. 同时具有分离读/写数据通道;

. 支持显著传输访问和乱序访问;

. 更加容易进行时序收敛

AXI4包含三种接口:

. AXI4——For high-performance memory-mapped requirements.

. AXI4-Lite——For simple, low-throughput memory-mapped communication (for example, to and from control and status registers).

. AXI4-Stream——For high-speed streaming data.

从上面的描述可以看出,AXI4协议相当于原来的AHB协议,提供高速的系统内部互连通道,可以支持burst模式,主要用于处理器访问存储等需要高速数据的场合;AXI4-Lite为外设童工单个数据传输,相当于原来的APB协议,用于访问一些低速外设;AXI4-Stream接口就像FIFO一样,数据传输的时候不需要地址,而是主从设备直接连续读写数据,主要用于如视频、高速AD、PCIe、DMA接口等需要高速数据传输的场合,跟Xilinx原来的Local Link协议类似。

AXI Interconnect

AXI协议严格的讲是一个点对点的主从接口协议,当多个外设需要互相交互数据时,我们需要加入一个AXI Interconnect模块,也就是AXI互联矩阵,作用是提供将一个或多个AXI主设备连接到一个或多个AXI从设备的一种交换机制(有点类似于交换机里面的交换矩阵)。Xilinx为我们提供了实现这种互联矩阵的IP核axi_interconnect_1,在前面的例子中,我们在XPS中可以看到。这个IP核最多可以支持16个主设备、16个从设备,如果需要更多的接口,可以多加入几个IP核。关于AXI Interconnect更多的知识,可参考Xilinx官方文档DS768。

AXI4和AXI4-Lite接口包含5个不同的通道:

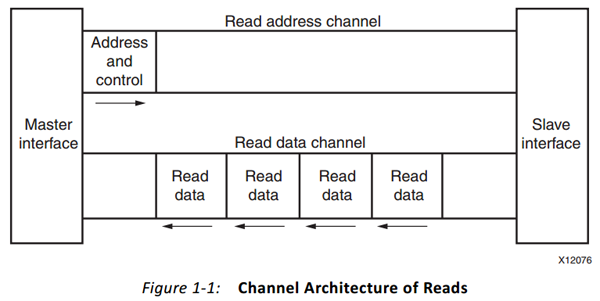

. Read Address Channel

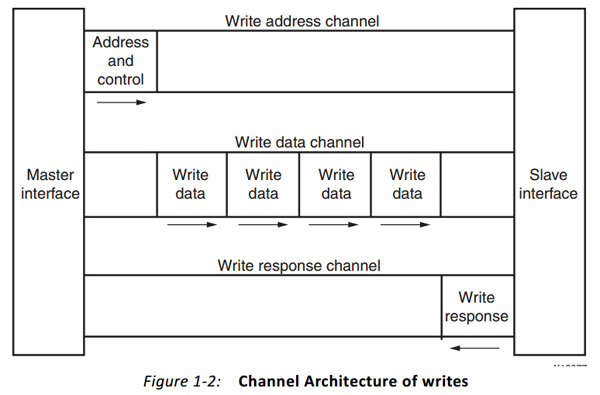

. Write Address Channel

. Read Data Channel

. Write Data Channel

. Write Response Channel

其中每个通道都是一个独立的AXI握手协议。下面两个图分别显示了读和写的模型:

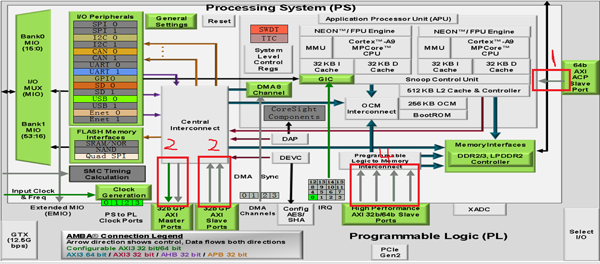

ZYNQ中的AXI接口共有9个,主要用于PS与PL的互联,包含以下三个类型:

. AXI_ACP接口,是ARM多核架构下定义的一种接口,中文翻译为加速器一致性端口,用来管理DMA之类的不带缓存的AXI外设,PS端是Slave接口。

. AXI_HP接口,是高性能/带宽的AXI3.0标准的接口,总共有四个,PL模块作为主设备连接。主要用于PL访问PS上的存储器(DDR和On-Chip RAM)

. AXI_GP接口,是通用的AXI接口,总共有四个,包括两个32位主设备接口和两个32位从设备接口。

其实,在具体设计中我们往往不需要在连接这个地方做太多工作,就像上一个例子中,我们加入IP核以后,系统会自动使用AXI接口将我们的IP核与处理器连接起来,我们只需要再做一点补充就可以了。不过,这部分概念还是了解比较好。

AXI总线简介的更多相关文章

- AXI总线简介、ID分析、DMA、Vivado烧录、系统集成

转载:https://blog.csdn.net/CrazyUncle/article/details/89918030?depth_1-utm_source=distribute.pc_releva ...

- AXI总线介绍

原帖地址:https://wenku.baidu.com/view/7c424c17e3bd960590c69ec3d5bbfd0a7956d5b9.html 1.AXI简介 AXI(Advanc ...

- zedboard如何从PL端控制DDR读写(二)——AXI总线

虽然Xilinx已经将和AXI时序有关的细节都封装起来,给出了官方IP和向导生成自定义IP,用户只需要关注自己的逻辑实现,但是还是有必要简单了解一下AXI的时序,毕竟咱是做硬件设计的. AXI(Ad ...

- AXI总线

AXI(Advanced eXtensible Interface)是一种总协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture) ...

- CAN总线简介

CAN总线简介 个节点,通信波特率为5Kbps~1Mbps,在通信的过程中要求每个节点的波特率保持一致(误差不能超过5%),否则会引起总线错误,从而导致节点的关闭,出现通信异常.

- FPGA中的除法运算及初识AXI总线

FPGA中的硬件逻辑与软件程序的区别,相信大家在做除法运算时会有深入体会.硬件逻辑实现的除法运算会占用较多的资源,电路结构复杂,且通常无法在一个时钟周期内完成.因此FPGA实现除法运算并不是一个&qu ...

- 自定义AXI总线形式SPI接口IP核,点亮OLED

一.前言 最近花费很多精力在算法仿真和实现上,外设接口的调试略有生疏.本文以FPGA控制OLED中的SPI接口为例,重新夯实下基础.重点内容为SPI时序的RTL设计以及AXI-Lite总线分析.当然做 ...

- 利用ZYNQ SOC快速打开算法验证通路(6)——利用AXI总线实时配置sysGen子系统

利用ZYNQ验证算法的一大优势在于,可以在上位机发送指令借助CPU的控制能力和C语言易开发特点,实时配置算法模块的工作模式.参数等对来对其算法模块性能进行全面的评估.最重要的是无需重新综合硬件模块. ...

- 将自己写的HDL代码封装成带AXI总线的IP

将自己写的HDL代码封装成带AXI总线的IP 1.Tools->create and package IP 2.create AXI4总线的IP 3.新建block design 4.点击右键, ...

随机推荐

- 【C++】bazel的使用

bazel的使用 bazel是google开源的构建工具,可以支持多种语言的构建.这里来尝试一下如何在C++项目中使用bazel构建. 安装就不介绍了,在官网很详细,输入bazel --help: U ...

- python3操作redis

redis也被称为缓存 1.redis是一个key-value存储系统,没有ForeignKey和ManyToMany的字段. 2.在redis中创建的数据彼此之间是没有关系的,所以也被称为是非关系型 ...

- NumPy快速入门笔记

我正以Python作为突破口,入门机器学习相关知识.出于机器学习实践过程中的需要,我快速了解了一下NumPy这个科学计算库的使用方法.下面记录相关学习笔记. 简介 NumPy是一个科学计算库.结合Py ...

- BZOJ 2707: [SDOI2012]走迷宫 [高斯消元 scc缩点]

2707: [SDOI2012]走迷宫 题意:求s走到t期望步数,\(n \le 10^4\),保证\(|SCC| \le 100\) 求scc缩点,每个scc高斯消元,scc之间直接DP 注意每次清 ...

- BZOJ 2055: 80人环游世界 [上下界费用流]

2055: 80人环游世界 题意:n个点带权图,选出m条路径,每个点经过val[i]次,求最小花费 建图比较简单 s拆点限制流量m 一个点拆成两个,限制流量val[i],需要用上下界 图中有边的连边, ...

- AJAX入门第一篇就够了

什么是Ajax Ajax(Asynchronous JavaScript and XML) 异步JavaScript和XML Ajax实际上是下面这几种技术的融合: (1)XHTML和CSS的基于标准 ...

- 安装RabbitMQ(一)

RabbitMQ简介 RabbitMQ 是由 LShift 提供的一个 Advanced Message Queuing Protocol (AMQP) 的开源实现,由以高性能.健壮以及可伸缩性出名的 ...

- Mac通过brew安装reds、memcached

redis brew install php70-redis 配置文件: /usr/local/etc/php/7.0/conf.d/ext-redis.ini memcached brew inst ...

- MySQL对sum()字段 进行条件筛选,使用having,不能用where

显示每个地区的总人口数和总面积.仅显示那些面积超过1000000的地区. SELECT region, SUM(population), SUM(area) FROM bbc GROUP BY reg ...

- iOS通知传值的使用

通知 是在跳转控制器之间常用的传值代理方式,除了代理模式,通知更方便.便捷,一个简单的Demo实现通知的跳转传值. 输入所要发送的信息 ,同时将label的值通过button方法调用传递, - (IB ...