FPGA噪声干扰

在FPGA高速AD采集设计中,PCB布线差会产生干扰。今天小编为大家介绍一些布线解决方案。

1、信号线的等长

以SDRAM或者DDRII为例,数据线,命令线,地址线以及时钟线最好等长,误差不要超过500mil。

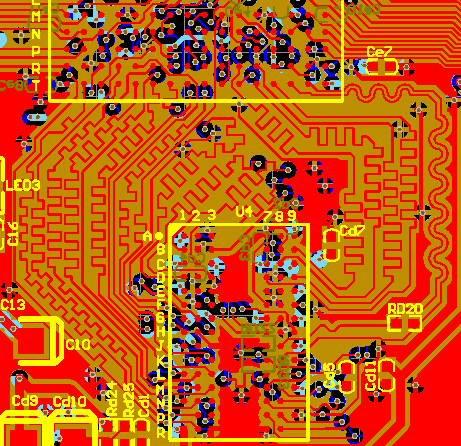

上图是FPGA与SDRAM布线,时钟频率设定为125M,为了等长可以走蛇形线。

蛇形走线虽然可以做到走线等长,但同时也占用更多的PCB面积。蛇形线没有所谓滤波或抗干扰的能力,只可能降低信号质量,所以只作时序匹配之用而无其它目的。

DDRII线路等长设计,最右边的弧度较大的走线为差分的时钟线,时钟线质量要求是比较高的。

布线是痛苦的,也是繁琐的,布不通时需要重新布线,不厌其烦的尝试,才能做出更好的效果。

2、电源芯片的选择

很多高速AD场合,开关电源并不合适,因为开关电源带来很多毛刺。大多数选择线性稳压电源。小编以ASM1117为例为大家介绍电源芯片中电容的使用。

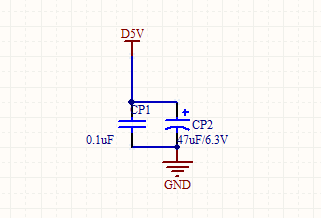

5V电源输入端,应加容值较大的钽电容或者电解电容滤除电源的低频噪声,加104(0.1uF)瓷片电容滤除高频噪声。电源走线应适当加宽。

在PCB布线时,也应该在5V走线的末端加容值较大的电容。

以ASM1117-3.3降压为例,如下图:

如上图,1117的3.3输出走线往下走,那么电容CP5放在旁边是没有任何效果的,通常这种电容是104瓷片电容,这个电容的容值是一个非常好的容值,在电源滤波中效果非常好。

那么该如何布局?

如上图,此种布局,CP28以及 CP10放置,电容应当放在电源走线路径上。注意电容不能离芯片引脚太远,电容有滤波半径,超出某一范围,电容将起不到滤波效果。

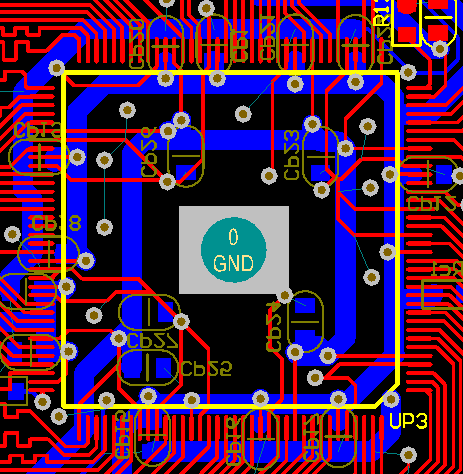

FPGA电源布线,根据多年布线经验以及产品稳定性,小编为大家推荐以下方案:

以QFP封装的FPGA为例,有三种电源,1.2V,2.5V,3.3V。布线时最好如上图效果,电源线之间最好隔开距离,FPGA电源引脚要加入104电容。

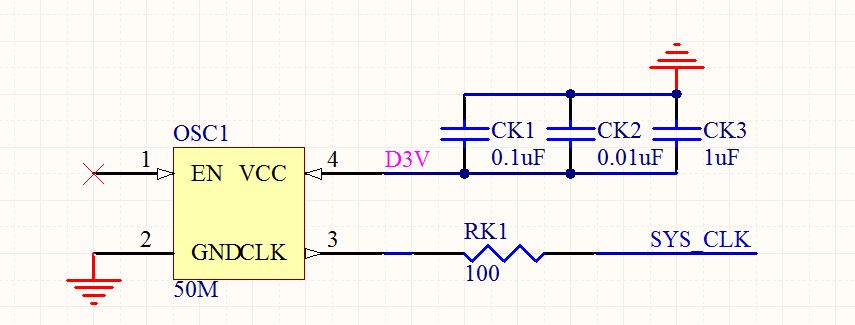

3、有源晶振布线

原理图设计如上,时钟输出端串入100~330欧姆的电阻,防止阻抗不匹配时时钟信号反射叠加。

有源晶振电源端加入103、104、105三种瓷片电容滤波,防止电源噪声和时钟之间的串扰。

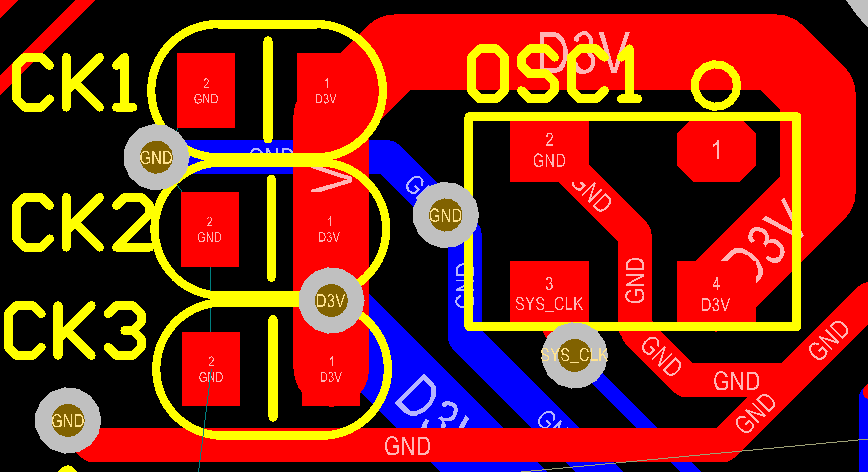

PCB布线时,上述效果时很糟糕的。晶振下面不应布线,电源走线应远离时钟线布线,并且中间加宽地线耦合,防止干扰。

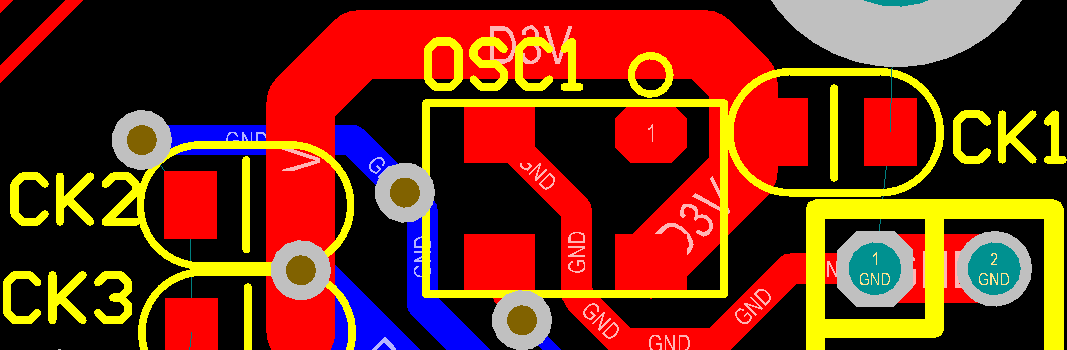

如上图布线,电源线避开时钟线,中间加入粗地线,注意有些地线不需要手动连接,放置地过孔,在铺铜(地网络)时,会自动加入。

此种方式放置电容亦可行。

FPGA噪声干扰的更多相关文章

- FPGA与simulink联合实时环路系列——实验三 按键key

实验三 按键key 实验内容 在FPGA的实验中,经常涉及到按键的使用,按键是必不可少的人机交互的器件之一,在这些实验中,有时将按键的键值读取显示到数码管.LCD或者是通过串口传送到PC的串口助手上进 ...

- FPGA与simulink联合实时环路系列——实验二LED

实验二LED 实验内容 在实验一的基础上,将simulink产生的测试信号输出到FPGA开发板上的LED灯进行显示,这里要在生成的硬件模型上进行修改,将传送到FPGA的信号输出到8个LED灯上,并且对 ...

- FPGA优化之高扇出

Fanout即扇出,模块直接调用的下级模块的个数,如果这个数值过大的话,在FPGA直接表现为net delay较大,不利于时序收敛.因此,在写代码时应尽量避免高扇出的情况.但是,在某些特殊情况下,受到 ...

- 关于 FPGA 内部信号扇入扇出

扇入.扇出系数 扇入系数是指门电路允许的输入端数目.一般门电路的扇入系数为1—5,最多不超过8.扇出系数是指一个门的输出端所驱动同类型门的个数,或称负载能力.一般门电路的扇出系数为8,驱动器的扇出系数 ...

- FPGA Timing笔记

很多FPGA工程师都会遇到timing的问题,如何让FPGA跑到更快的处理频率是永久话题.决定FPGA的timing关键是什么?如何才能跑到更快的频率呢? A. 第一步需要了解FPGA的timing路 ...

- FPGA的引脚VCCINT 、VCCIO VCCA

首先是看到FPGA在配置的时候有三种不同的电VCCINT .VCCIO VCCA,于是就查了下有什么不同: FPGA一般会有许多引脚,那它们都有什么用呢? VCCINT为施加于 FPGA 内核逻辑的电 ...

- FPGA与simulink联合实时环路系列——实验一 测试

实验一 测试 实验内容 在simulink创建测试模块,通过测试模块产生信号,再传送到FPGA,FPGA读出后再将信号无处理传送回simulink进行显示.由此来测试整个硬件在环的功能是否正常,并且熟 ...

- FPGA与simulink联合实时环路系列—开篇

FPGA与simulink联合实时环路系列—开篇 作为网络上第一个开源此技术,笔者迫不及待地想将此技术分享出来,希望大家多多支持.笔者从2011年接触FPGA以来,从各个方面使用FPGA,无论是控制. ...

- 基于FPGA的飞机的小游戏

基于FPGA的飞机的小游戏 实验原理 该实验主要分为4个模块,采用至上而下的设计方法进行设计.由50M的晶振电路提供时钟源,VGA显示控制模块.图形显示控制模块.移动模块的时钟为25M,由时钟分频电路 ...

随机推荐

- JNI_Z_03_类中的字段和方法的签名

1. Java类型 相应的签名 例子 boolean Z byte B char C short S int I long L float F double D void V Object L用&qu ...

- python学习笔记(arange函数与linspace函数)

上一篇提及到matplotlib模块.其中会涉及到numpy模块科学计数 这里总结两个数组生成函数 arange 与 linspace: #!/usr/bin/env python # -*- cod ...

- Linux命令详解-cd

Linux cd 命令可以说是Linux中最基本的命令语句,其他的命令语句要进行操作,都是建立在使用 cd 命令上的. 所以,学习Linux 常用命令,首先就要学好 cd 命令的使用方法技巧. ...

- ASP.NET Core 简单引入教程

0.简介 开源.跨平台 1.环境安装 参考官方教程 Core 官方文档 2.向世界问个好 sheel/cmd 下: dotnet --help // 查看帮助 dotnet new * / ...

- Node net模块与http模块一些研究

这周遇到一个有意思的需求,端上同学希望通过 socket 传送表单数据(包含文件内容)到 node 端,根据表单里的文件名.手机号等信息将文件数据保存下来.于是我这样写了一下--socket_serv ...

- NSURLConnection / NSURLSession/ SDWebImage

1. NSURLConnection (iOS9开始被弃用)=========================================== 此类的对象加载一个URL请求对象,通过异步/同步的方 ...

- L132

Major Opioid Maker to Pay for Overdose-Antidote Development A company whose prescription opioid mark ...

- cocos2dx lua 热加载实现

[Q]原创 2015-08-30 在公司使用cocos2dx+lua 开发游戏有一段时间了,刚好lua的热更新交给我负责.以前热更新的lua脚本大部分都是在下载之后加载.最近策划又有新需求,需要在游戏 ...

- Kotlin 第一弹:自定义 ViewGroup 实现流式标签控件

古人学问无遗力, 少壮工夫老始成.纸上得来终觉浅, 绝知此事要躬行. – 陆游 <冬夜读书示子聿> 上周 Google I/O 大会的召开,宣布了 Kotlin 语言正式成为了官方开发语言 ...

- Android数据库代码优化(2) - 从SQLite说起

从SQLite说起 如果没有SQLite的基础,我们只是从Android封装的SQLite API去学习的话,难免思路会受到限制.所以,我们还是需要老老实实从头开始学习SQLite. 当我们有一身的S ...