FPGA基础入门篇(四) 边沿检测电路

FPGA基础入门篇(四)——边沿检测电路

一、边沿检测

边沿检测,就是检测输入信号,或者FPGA内部逻辑信号的跳变,即上升沿或者下降沿的检测。在检测到所需要的边沿后产生一个高电平的脉冲。这在FPGA电路设计中相当的广泛。

没有复位的情况下,正常的工作流程如下:

(1)D触发器经过时钟clk的触发,输出trigger信号,保存了t0时刻的信号。

(2)同时由trigger通过非门输出信号,保留了当前时刻t1的触发信号

(3)经过与门输出信号pos_edge,neg_edge

a) 只有t0时刻为高,且t1时候为低的时候,与门输出高,此时为下降沿。

b) 只有to时候为低,且t1时候为高的时候,与门输出高,此时为上升沿。

当然,在复位的时刻,DFF被复位,无法检测触发信号。

二、采用一个触发器的边沿检测电路设计:

- verilog代码实现:

//one trigger

module edge_detect(

input clk_i, rst_n_i, data_i, //输入端口

output posedge_o,negedge_o //输出端口

);

//one regester

reg tri_1;

always@(posedge clk_i or negedge rst_n_i)

begin

if (! rst_n_i) //置位

begin

tri_1 <= 1'b0;

end

else

begin

tri_1 <= data_i; //触发器

end

end

assign negedge_o = tri_1 & (~data_i); //下降沿检测

assign posedge_o = (~tri_1) & data_i; //上升沿检测

endmodule

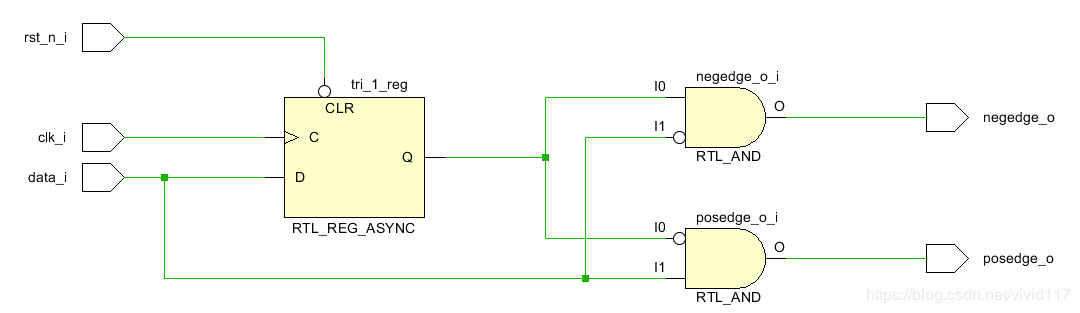

- RTL电路

用vivado RTL分析电路

- 仿真代码及结果

module tb_test(

);

reg clk_i,rst_n_i,data_i;

wire posedge_o, negedge_o;

//模块调用

edge_detect u1(

.clk_i(clk_i),

.rst_n_i(rst_n_i),

.data_i(data_i),

.posedge_o(posedge_o),

.negedge_o(negedge_o)

);

//initial

initial begin

clk_i = 0;

rst_n_i = 0;

#10

rst_n_i = 1;

data_i = 0;

#13

data_i = 1; //上升沿

#20

data_i = 0; //下降沿

#15

data_i = 1; //上升沿

#10

data_i = 0; //下降沿

end

//clk 信号

always #5 clk_i = ~clk_i;

endmodule

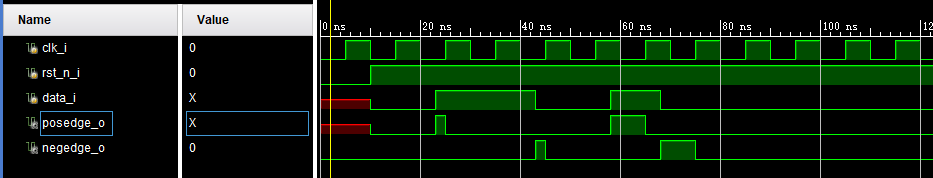

仿真结果:

分析:在第一次上升沿时,由于上升沿离下个时钟上升沿间隔短,结果会产生“毛刺”

下面利用多个触发器可以延迟n-1个触发器的周期时间保证至少有一个时钟周期。

三、采用多个触发器的边沿检测电路设计:

- verilog 语言实现(两个触发器及双边沿检测)

//two trigger

module edge_detect(

input clk_i, rst_n_i, data_i,

output posedge_o,negedge_o,double_edge_o

);

//two regester

reg tri_1;

reg tri_2;

always@(posedge clk_i or negedge rst_n_i)

begin

if (! rst_n_i) //置位

begin

tri_1 <= 1'b0;

tri_2 <= 1'b0;

end

else

begin

tri_1 <= data_i;

tri_2 <= tri_1; 二级触发器

end

end

assign negedge_o = tri_2 & (~tri_1); //下降沿检测

assign posedge_o = (~tri_2) & tri_1; //上升沿检测

assign double_edge_o = tri_1 ^ tri_2; //双边沿检测

endmodule

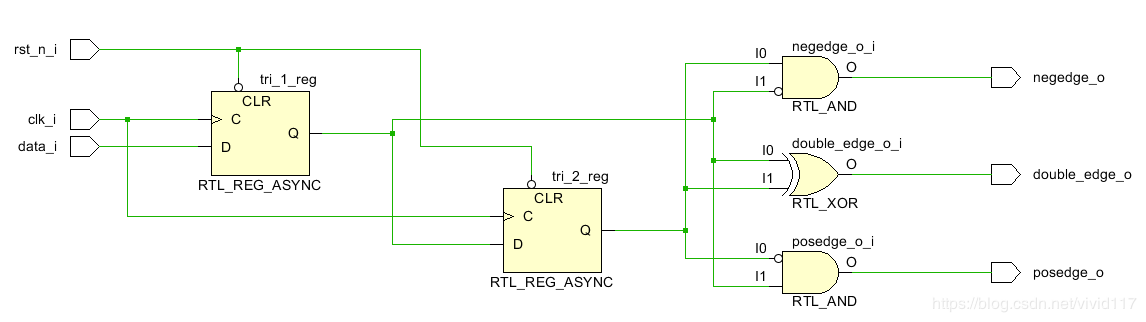

- RTL电路

用vivado RTL分析电路

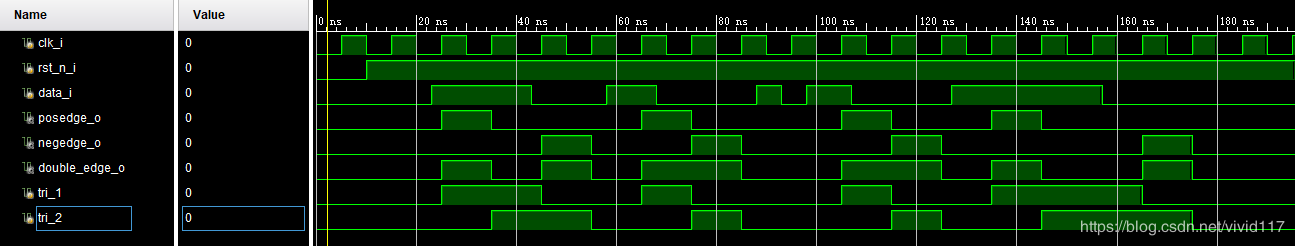

- 仿真结果:

tri_1将输入与时钟同步,tri_2延迟一个时钟周期。级数越多,延迟越高。

可以看到边沿检测结果都出现在下一个时钟周期

四、边沿检测应用

边沿检测技术在项目应用中,非常低广泛。如要有效捕获信号跳变沿,边沿检测技术的应用是必不可少的。

有如下几个方面

(1)将时钟边沿使能转换为边沿检测使能,使时钟同步化。

(2)捕获信号的突变(UART,SPI等信号使能突变)

(3)逻辑分析仪中信号的边沿检测。

五、实现指标及存在缺陷

没有十全十美的东西,也没有十全十美的电路、代码;边沿检测技术亦如此。有如下缺陷:

(1)增大CLK信号可以增强边沿检测的效率,但不能滤去跳变的杂波。

(2)减少CLK可以有效滤去跳变的杂波,但不能及时检测到边沿跳变。

(3)增加DFF能更好的滤除杂波,寄存信号,但同时检测延时大。

参考博文: https://blog.csdn.net/u011412586/article/details/9971455

https://www.cnblogs.com/crazybingo/archive/2011/07/26/2117149.html

FPGA基础入门篇(四) 边沿检测电路的更多相关文章

- SQLAlchemy 教程 —— 基础入门篇

SQLAlchemy 教程 -- 基础入门篇 一.课程简介 1.1 实验内容 本课程带领大家使用 SQLAlchemy 连接 MySQL 数据库,创建一个博客应用所需要的数据表,并介绍了使用 SQLA ...

- Linux及Arm-Linux程序开发笔记(零基础入门篇)

Linux及Arm-Linux程序开发笔记(零基础入门篇) 作者:一点一滴的Beer http://beer.cnblogs.com/ 本文地址:http://www.cnblogs.com/bee ...

- 【Linux开发】Linux及Arm-Linux程序开发笔记(零基础入门篇)

Linux及Arm-Linux程序开发笔记(零基础入门篇) 作者:一点一滴的Beer http://beer.cnblogs.com/ 本文地址:http://www.cnblogs.com/beer ...

- JS基础入门篇(三十五)—面向对象(二)

如果没有面向对象这种抽象概念的小伙伴,建议先看一下我写的JS基础入门篇(三十四)-面向对象(一)

- 【SSRS】入门篇(四) -- 向报表添加数据

原文:[SSRS]入门篇(四) -- 向报表添加数据 定义好数据集后 [SSRS]入门篇(三) -- 为报表定义数据集 ,就可以开始设计报表了,将要显示在报表的字段.文本框.图像和其他项从工具箱拖放到 ...

- MyBatis基础入门《四》接口方式.Select查询集合

MyBatis基础入门<四>接口方式.Select查询集合 描述: 在<MyBatis基础入门<二>Select查询>中有说过,SQLSession有两种用法,这里 ...

- verilog 之数字电路 边沿检测电路

由代码可知:此边沿检测电路是由两个触发器级联而成,sign_c_r 输出是sign_c_r2的输入.并且有异步复位端没有使能端.最后输出:由触发器的输出取反和直接输出相与.如下的RTL图.

- 云小课|DGC数据开发之基础入门篇

阅识风云是华为云信息大咖,擅长将复杂信息多元化呈现,其出品的一张图(云图说).深入浅出的博文(云小课)或短视频(云视厅)总有一款能让您快速上手华为云.更多精彩内容请单击此处. 摘要:欢迎来到DGC数据 ...

- .NET ORM 的 “SOD蜜”--零基础入门篇

PDF.NET SOD框架不仅仅是一个ORM,但是它的ORM功能是独具特色的,我在博客中已经多次介绍,但都是原理性的,可能不少初学的朋友还是觉得复杂,其实,SOD的ORM是很简单的.下面我们就采用流行 ...

随机推荐

- Leetcode 207.课程表

课程表 现在你总共有 n 门课需要选,记为 0 到 n-1. 在选修某些课程之前需要一些先修课程. 例如,想要学习课程 0 ,你需要先完成课程 1 ,我们用一个匹配来表示他们: [0,1] 给定课程总 ...

- Android ImageView加载圆形图片且同时绘制圆形图片的外部边缘边线及边框

Android ImageView加载圆形图片且同时绘制圆形图片的外部边缘边线及边框 在Android早期的开发中,如果涉及到圆形图片的处理,往往需要借助于第三方的实现,见附录文章1,2.And ...

- Python模块:configparser、hashlib、(subprocess)

configparser模块: 此模块用于生成和修改常见配置文档. 一个常见配置文件(.ini的后缀名)格式如下: [DEFAULT] # DEFAULT 是指后面的字典里都会默认有的内容 Serve ...

- 【NOIP2017练习】论战大原题(并查集)

题意:给定一个n个点m条边的无向图.定义一条路径的长度为路径上最小边的权值. 定义dist(i,j)为起点为i,终点为j的长度最长的路径的长度.求出第k大的dist(i,j)(i<j). 对于所 ...

- HDU - 2059 龟兔赛跑(多阶段决策dp)

http://acm.hdu.edu.cn/showproblem.php?pid=2059 初始把起点和终点也算做充电站,设dp[i]是到第i个充电站的最短时间,那么dp[n+1]即是乌龟到达终点的 ...

- Meeting 加虚拟边

Bessie and her friend Elsie decide to have a meeting. However, after Farmer John decorated his fence ...

- Bootstrap官网文档查询

Ctrl+F 在出现的小搜索框里面输入要查找的东西.回车即可!

- Ubuntu 16.04在搭建Redis Cluster搭建时,使用gem install redis时出现:ERROR: While executing gem ... (Gem::FilePermissionError) You don't have write permissions for the /var/lib/gems/2.3.0 directory.

注意:千万不要使用sudo来执行gem install redis. 解决方法: sudo apt-get update sudo apt-get install git-core curl zlib ...

- delphi调用oracle存储过程(ODAC)

CREATE OR REPLACE PACKAGE p_lee01ISTYPE cur_lee01 IS REF CURSOR;END; CREATE OR REPLACE PROCEDURE pro ...

- ASP.NET MVC不可或缺的部分——DI(IOC)容器及控制器重构的剖析

ASP.NET MVC不可或缺的部分——DI(IOC)容器及控制器重构的剖析 IoC框架最本质的东西:反射或者EMIT来实例化对象.然后我们可以加上缓存,或者一些策略来控制对象的生命周期,比如是否 ...