(数字IC)低功耗设计入门(二)——功耗的分析

前面学习了进行低功耗的目的个功耗的构成,今天就来分享一下功耗的分析。由于是面向数字IC前端设计的学习,所以这里的功耗分析是基于DC中的power compiler工具;更精确的功耗分析可以采用PT,关于PT的功耗分析可以查阅其他资料,这里不涉及使用PT的进行功耗分析。

(1)功耗分析与流程概述

上一个小节中讲解了功耗的构成,并且结合工艺库进行简要地介绍了功耗的计算。但是实际上,我们根本不可能人工地计算实际的大规模集成电路的功耗,我们往往借助EDA工具帮我们分析电路的功耗。这里我们就介绍一下EDA工具分析功耗的(普遍)流程,然后下一小节我们将介绍低功耗电路的设计和优化。

①功耗分析流程的输入输出

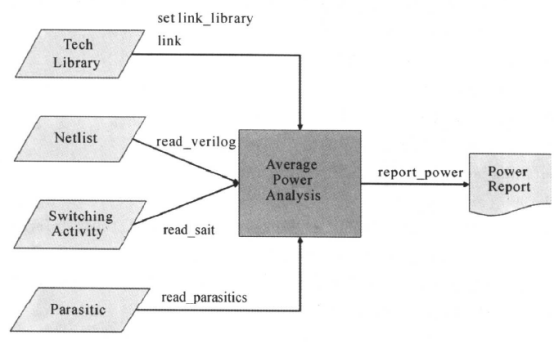

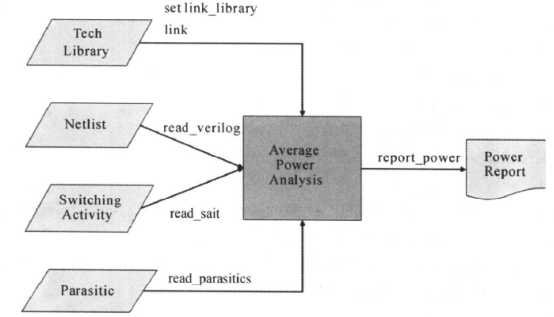

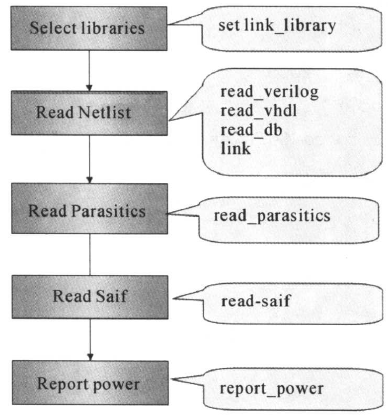

功耗分析的流程(从输入输出关系看)如下所示:

上面的图中,需要四种东西:

·tech library:这个就是包含功耗信息的工艺库了,比较精确的库里面还应该包含状态路径(SDPD)信息,代工厂提供。

·netlist:设计的门级网表电路,可以通过DC综合得到。

·parasitic:设计中连线等寄生参数,比如寄生电容、寄生电阻,这个一般是后端RC寄生参数工具提供,简单的功耗分析可以不需要这个文件。

·switch activity:包含设计中每个节点的开关行为情况,比如说节点的翻转率或者可以计算出节点翻转率的文件。这个开关行为输入文件是很重要的。这个开关行为可以有不同的形式提供,因此就有后面不同的分析功耗的方法。

(注意,不管使用什么方法进行功耗分析,功耗分析的时候,输入设计文件的都是门级网表文件)

②开关行为的一些概念

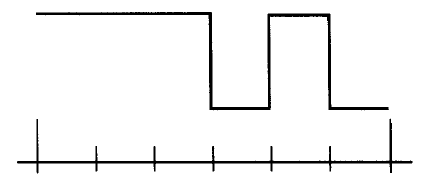

说到开关行为,我们前面的翻转率也是一种开关行为。此外我们还有其他关于开关行为描述的概念,这里我们通过举例说明,如下图所示:

·翻转(次)数:逻辑变化的次数,上图中信号的翻转数为3.

·翻转率:前面也有相关介绍,这里重提一下,翻转率是单位时间内信号(包括时钟、数据等等信号)的翻转次数。上图中翻转率为3/6 = 0.5(6个时间间隔内,翻转了3次)

·T1,T0:(节点)信号的逻辑值为1和0的持续时间,上图中T1为4,T0为2。

·静态概率(static probability ,SP):(节点)信号逻辑值为1的概率,上图中的SP为4/6=2/3。

③开关行为(文件)情况表示

前面我们说到了功耗的分析需要开关行为的情况,一般就是指每个节点的翻转率情况,我们有下面方式设置翻转率:

·直接命令进行:例如命令:

set_switching_activity -static 0.2 -toggle_rate 20 -period 1000 [all_inputs]

这时,翻转率设置的节点是输入,响应的翻转率为:Tr = 20/1000 = 0.02GHz

·SAIF文件:即switching activity interchange format,开关行为内部交换格式文件,用于仿真器和功耗分析之间交换信息的ASCII文件(美国标准信息交换码文件)。

·VCD文件,即value change dump 文件,它也是一个ASCII文件,文件中包括了一个设计中所选择变量值的变化信息,这些信息通过在仿真testbench中使用“VCD系统函数”得到。

在Synopsys的低功耗设计流程里面,可以使用power compiler(包含在design compiler中)进行功耗分析。我们可以通过命令来定义节点的翻转率的方法来分析功耗----称为无向量(vector-free)分析法;由于SAIF文件和VCD文件可以通过对电路仿真得到,它们是仿真接口格式文件,因此也可以通过VCS仿真器产生SAIF或者VCD文件的方法分析功耗。当要分析的结果比较精确时,一般使用SAIF文件或者VCD文件(VCD文件通过相关命令转换成SAIF文件,而后使用SAIF进行功耗分析)。

(2)无向量分析法

前面我们说到,无向量分析法就是通过命令来定义节点的翻转率的方法来分析功耗。我们先来逐条学习需要什么的命令,然后在后面进行举例说明无向量分析法的脚本。

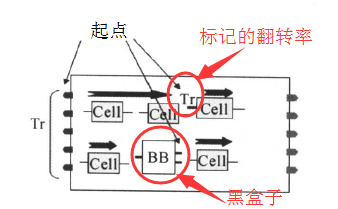

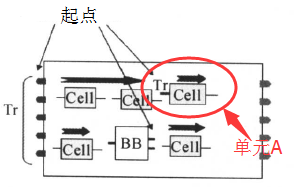

在学习设置翻转率的命令之前,我们先来了解一下什么是设计的传播起点和黑盒子。我们定义传播的起点为设计的输入端和黑盒子的输出端,黑盒子是指在工艺库里没有功能描述的单元(比如ROM 、RAM或者一些IP核)。例如对于下面的设计中:

上面的设计有三处起点,一处是整个设计的输入端,一处是黑盒子的输出端,还有一处是某个单元的输入端。最后一处的起点不包含在我们的定义中,但是我们也把它当做起点,因为这是被标记了翻转率,这个我们后面进行讲解。

利用无向量分析法分析功耗时,我们不必提供设计内部节点的翻转率,而是通过设置起点的翻转率就行了。我们有两种方法设置翻转率,一种是通过设置翻转变量,一种是通过标记的方法。下面我们就来介绍如何通过这两种方法进行设置翻转率。

①设置翻转变量

在power compiler中,可以设置下面的两个翻转变量进行设置翻转率:

power_default_toggle_rate

power_default_static_probability

下面就来介绍一下这两个变量(主要介绍power_default_toggle_rate)。

power_default_toggle_rate:其用法我们可以在DC中进行man一下,这个变量设置设计中默认使用的翻转率。定义方式是:

set power_default_toggle_rate 翻转值

翻转值默认是0.5。这个翻转值不是翻转率,这个变量定义的翻转率是个相对的值:

·如果设计定义了时钟,这个power_default_toggle_rate变量定义的翻转率就以最快的时钟为参考,比如翻转值为0.5时,设计中最快的时钟为10ns,那么翻转率Tr = 0.5/10ns = 0.05GHz,也就是整个设计中默认的翻转率是0.05GHz。

·如果设计中没有时钟,那么就会以工艺库中的时间单位作为参考,例如工艺库中的时间单位是ns,翻转值为0.5,那么翻转率Tr = 0.5/1ns = 0.5GHz。

power_default_static_probability:这个设置的是默认的静态概率,也就是起点的逻辑值是1的概率。至于静态概率,这里就不详细描述了。这两个变量的默认翻转值都是0.5,翻转率是很大的,一般情况下需要减小一点,比如设置为0.01和0.02这样的。

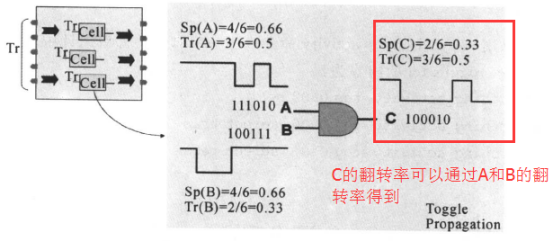

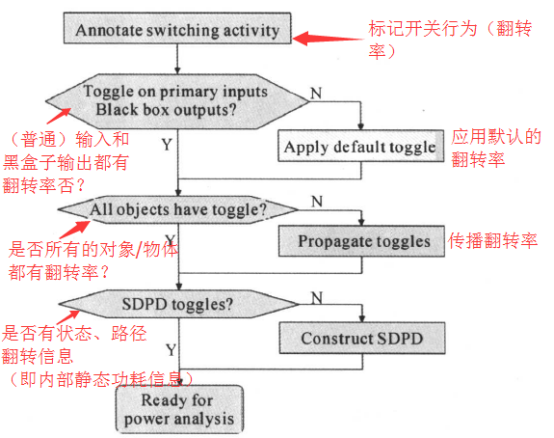

一般情况下,默认的翻转率是设置在起点上的,也就是说起点的翻转率用的是power_default_toggle_rate这个变量设置的翻转率,内部节点的翻转率可以通过传播得到,如下图所示:

需要说明的是,传播不可以穿过没有功能描述的黑盒子,也就是不能通过传播的方式得到黑盒子的输出翻转率,因此我们在最前面就定义了,将黑盒子的输出当做起点,这样其他节点的翻转率可以通过传播得到(包括黑盒子的输入),黑盒子输出的翻转率通过默认设置的翻转率得到,我们就得到了设计中所有节点的翻转率。

②标记翻转率

上面的方式设置的是默认的翻转率。当我们需要为某个节点标记某个指定的翻转率,而不是使用默认的翻转率时,我们就用到了标记频率,如下图所示:

单元A的输入端口标记了特定翻转率,比如说0.04GHz。标记的翻转率比传播的翻转率优先级更高,被标记翻转率的节点将作为一个新的起点,这就不属于起点的定义,但还是叫它为起点的原因。标记翻转率之后,这个单元后续的节点的翻转率将通过这个新标记的翻转率传播得到。

设置标记翻转率(简称设置翻转率)的命令主要有两条:

set_switching_activity 和 set_case_analysis,下面就来讲解一下这两条命令的意思。

set_switching_activity :设置某个节点的翻转率和静态概率,在使用无向量分析法估算功耗的时候,这个命令被广泛使用,越多的节点上被标记翻转率,估算功耗的精度就越高。命令和选项如下所示:

set_switching_activity

[-static_probability static_probability]

[-toggle_rate toggle_rate]

[-state_condition state_condition]

[-path_sources path_sources]

[-rise_ratio rise_ratio]

[-period period_value | -base_clock clock]

[-type object_type_list]

[-hierarchy]

[object_list]

[-verbose]

下面来简单介绍一下常用的几个选项,详细的介绍可以通过man set_switching_activity获取。

-static_probability :设置静态概率。

-period period_value | -base_clock clock:设置时钟(周期),-period和 -base_clock只能设置其中一个。

-toggle_rate:设置翻转值,与-period或者 -base_clock相关联。翻转率Tr等于:用-base_clock选项指定的时钟周期里面的翻转数目 或 用-period选项指定的时间段里的翻转数目;当没有这个设置两个选项时,将使用工艺库里面的时间单位,即翻转率等于在每个库单位时间内的翻转数目。

下面来举例说明这个命令的用法:

例一:

create_clock CLK -period 20

set_switching_activity -base_clock CLK -toggle 0.5 -static 0.015 [all_inputs]

上述命令设置了时钟周期为20ns,然后命令使用的是-base_clock的选项,所有输入端的翻转值为0.5,静态概率为0.015,于是得到翻转率Tr=0 .5/20=0.025 GHz

例二:

set_switching_activity -period 1000 -toggle 25 -static 0.015 [all_inputs]

上述没有创建时钟,但是使用了period选项,意思是1000个周期内翻转了25次,于是我们就可以得到所以输入的翻转率Tr=25/1000=0. 025 GHz

例三:

set_switching_activity -toggle 0.025 -static 0.015 [all_inputs]

上述命令中,-period和 -base_clock这两个选项都没有使用,这个时候就跟工艺库里面的时间单位有关了,若库中时间单位为ns,那么我们就得到翻转率Tr=0.025 /1 = 0.025 GHz

上面讲解了set_switching_activity ,下面我们就来讲解一下set_case_analysis。

set_case_analysis 用来指定一个静态逻辑值,也就是设置信号为常数,不进行翻转;设计里面的一些信号需要这样子设计,例如复位信号,设置如下所示:

set_case_analysis 1 [get_ports reset]

则设置了reset的值常为1.

=================================================================================================

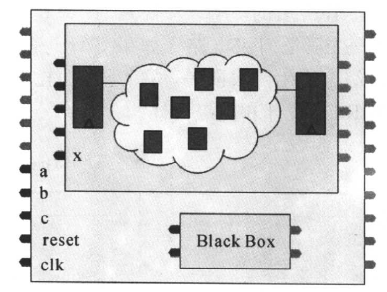

上面我们讲解了设置翻转率的方法,下面举例说明一下如何综合使用这两种翻转率。例如对于下面的设计:

翻转率的设置要求如下所示:

1.正确地定义时钟;

2.使用set_case_analysis命令设置常数控制信号reset;

3.在传输起点设置翻转率,在输入端和黑盒子输出端设置任何已知的翻转率,其他的起点将使用默认的翻转率。

4.让工具在设计中把翻转率传播下去

上面的没有要求具体的翻转率,因此我们可以设置我们想要的翻转率,根据上面的要求,我们编写相应的tcl脚本如下所示:

create_clock -p 4 [get_ports clk}

set_case_analysis 0 reset [get_ports reset]

set_power_default_toggle_rate 0.003

set_switching_activity -tog 0.02 a

set_switching_activity -tog 0.06 b

set_switching_activity -tog 0.11 x

上面的脚本中,设置了周期为4(ns)的时钟,然后利用set_case_analysis命令,设置reset端口为常数;翻转值为0.003,那么对应的翻转率为0.003/4ns,这个是默认的翻转率;然后利用set_switching_activity命令指定a、b、x的翻转值,其翻转率为 翻转值/4ns。

=============================================================================================

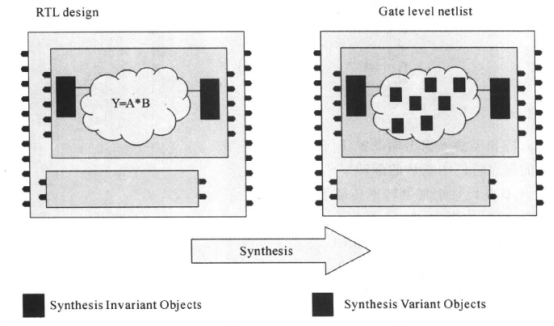

前面介绍了无向量分析法进行功耗分析,在介绍一下使用SAIF文件的方法进行功耗分析之前,我们先来介绍一下综合不变物体和综合变化物体的概念,下图为一个电路的RTL设计和门级设计:

根据定义,在综合前和综合后,设计中的寄存器数目和寄存器的结构是不变的,输入/输出端口和层次边界是不变的,设计中的黑盒子是不变的。这些不变的物体称为综合不变物体(Synthesis Invariant Objects,有时候也叫综合不变对象)。设计中大部分的组合电路生成与设计约束有很大的关系,不同的约束产生不同的组合电路。这些变化的物体称为综合变化的物体(Synthesis Variant Objects)。由于SAIF文件中涉及这两个概念,这里先进行介绍。

介绍完这两个概念之后,下面我们就来了解一下使用SAIF进行功耗分析。SAIF文件当做翻转率输入文件的方法有两种方式,也就是说利用SAIF进行功耗分析有两种方法——对RTL级的电路仿真后得到的SAIF文件(称为RTL backward SAIF) 以及 对门级网表的电路仿真后得到的文件(称为Gate backward SAIF)。下面逐个进行具体介绍。

(3)SAIF--RTL BACK分析法

RTL backward SAIF文件是通过对RTL代码进行仿真得到的,当设计很大的时候,门级仿真时间就会很长,这时候就可以使用这种方法进行分析。使用这种方法进行分析功耗的速度比较快,但是进度不够门级仿真SAIF文件的高。

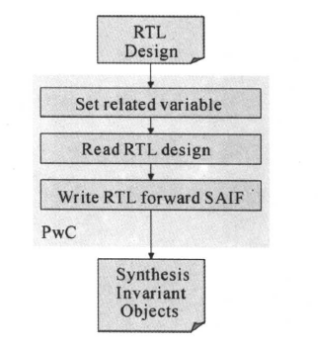

①RTL forward SAIF文件

RTL forward SAIF文件是记录RTL设计中综合不变物体的开关行为文件,可以简单地理解:RTL forward SAIF文件简要地记录了综合不变物的翻转率。RTL backward SAIF文件的产生需要RTL forward SAIF文件,因此我们首先需要产生RTL forward SAIF文件。产生RTL forward SAIF文件的流程如下:

RTL forward SAIF文件是由power compiler (包含在design compiler中)产生的,根据流程,我们知道,主要设置一些变量,然后读入RTL设计(RTL.v设计),接着读出SAIF文件就可以了。相应的脚本如下所示:

set power_preserve_rtl-hier_names true

read_verilog "sub.v top. v"

rtl2saif -output fwd_ rtl.saif

一个示例RTL forward SAIF文件里面的部分内容如下所示:

(SAIFILE

(SAIFVERSION "2 .0")

(DIRECTION "forward")

(DESIGN)

(DATE "Wed May 12 18:31:19 2004

(VENDOR "Synopsys,Inc")

(PROGRAM NAME "rtl2saif")

(VERSION“1 .0")

(DIVIDER/)

(INSTANCE top

(PORT

(address\15\ address\15\)

(address\14\ address\14\)

(address\13\ address\13\)

(address\12\ address\12\)

(address\11\ address\11\)

(address\10\ address\10\)

······

我们可以看到,文件里面包含设计中一系列综合不变的物体。在后续仿真中,仿真器只监视这些物体的开关行为。

②RTL backward SAIF文件的产生

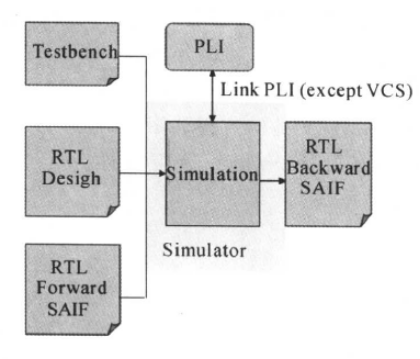

下面是产生RTL backward SAIF文件的流程:

从上图中,我们知道,产生RTL backward SAIF文件,需要在仿真器输入testbench测试平台文件、RTL.v设计、RTL forward SAIF文件,然后使用VCS产生RTL forward SAIF文件时,需要在testbench调用PLI监测节点的翻转率。下面我们就来介绍一下这几个部分。

·首先是PLI。使用VCS产生SAIF文件,需要用到程序设计语言接口(programming language interface,PLI)。通过PLI监测节点的翻转,得到节点的翻转率。主要需要下面的系统任务:

$set_gate_level_monitoring ( on|off|rtl_on);

$set_toggle_region (obj);

$read_ rtl_ saif(rtl_saif_file_name,tb_pathname);

$read_ lib_ saif(lib_saif_file_name);

$toggle_start;

$toggle_stop;

$toggle_reset();

$toggle_report(file_name,type,unit);

· RTL.v就是设计源文件了,然后RTL forward SAIF文件在前面也讲过了,这里就从略。

· 最后是testbench。testbench中调用RTL设计、调用一下上述的PLI系统函数、调用RTL forward SAIF文件等。一个简单的示例testbench文件如下所示:

module testbench;

top instl (a, b, c,s);//例化顶层设计

initial begin

$read_rtl_saif ("myrtl.saif")

$set_toggle_region (u1);

$toggle_start;

#120 a=0;

#STEP in_a=temp_in_a;

······

$toggle_stop;

$toggle_report("rtl.saif",1.0e-9,"top");

end

endmodule

上面的测试平台中,用了系统任务程序$read_rtl_saif ("myrtl. saif"),该命令读入综合不变物体文件——RTL forward SAIF。因此,仿真时,仿真器仅仅监视这些综合不变物体的开关行为。向量中$set_toggle_region (u1)命令选择要监视的模块。$toggle_start和$toggle_stop命令用于控制监视的起始和终止时间。$toggle_report("rtl. saif",1. 0e-9,"top")命令输出SAIF信息到指定的文件。

一起都准备就绪了,下面就可以使用VCS运行仿真:

vcs -R rtl. v testbench. v

注意,这里我们进行的是RTL设计文件的仿真,仿真完成后,就可以得到rtl.saif 文件,这个文件就是RTL backward SAIF文件。

③功耗的分析

对RTL代码仿真后,所得到的RTL Backward SAIF文件包含了设计中综合不变物体的开关行为信息。进行功耗分析时,分析工具通过其内部仿真器把综合不变物体的翻转率传播下去,从而得到其他所有节点的翻转率,进行门级电路的功耗分析。得到了RTL backward SAIF文件之后,我们根据前面的功耗分析的流程(从输入输出关系看),就可以分析功耗了:

这里的开关活动文件就是RTL backward SAIF文件了。然后在power compiler中利用RTL backward SAIF文件进行功耗分析的流程如下所示:

一个相应的示例脚本如下所示:

set target_library my. db

set link_library "* $target_library"

read_verilog mynetlist.v

current_design top

link

read_ saif -input rtl.saif -inst testbench/top

report_power

利用RTL backward SAIF文件分析功耗的过程就是上面这个样子了。上面的流程和脚本适用于前版图(pre-layout)的设计,没有用到寄生参数文件。连线的RC参数使用工艺库里的线负载模型。如果是后版图(post-layout)的设计,要尽量使用寄生参数文件,提高功耗分析的精确度。

从上面我们就知道,利用RTL backward SAIF文件分析功耗的流程就是:

power compiler 产生 RTL forward SAIF文件 ——》VCS仿真产生RTL backward SAIF文件 ——》power compiler 进行分析功耗。

(4)SAIF--GATE分析法

前面介绍了RTL backward SAIF文件分析功耗的方法和流程,下面介绍一下Gate backward SAIF文件分析功耗的方法和流程,这个与RTL backward SAIF文件的很类似。

①library forward SAIF 文件(简称为 库SAIF文件)

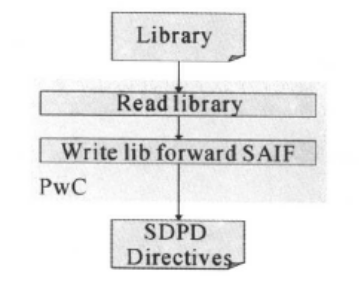

库SAIF文件是包含SDPD(电路状态路径)信息的SAIF文件。Gate backward SAIF文件的生成需要库SAIF文件,该文件可以通过power compiler生成,流程如下所示:

对应该流程的一个示例脚本如下所示:

read_db mylib.db

lib2saif -output mylib. saif -lib_pathname mylib.db

示例库SAIF文件的部分内容如下所示:

(SAIFILE

(SAIFVERSION "2.0" "lib")

(DIRECTION "forward")

(DESIGN)

(DATE "Mon May 10 15:40:19 2004"

(VENDOR "Synopsys,Inc")

(PROGRAM NAME "lib2saif")

(DIVIDER / )

(LIBRARY "ssc_core_typ"

(MODULE "and2al"

(PORT

(Y

(COND A RISE FALL (IOPATH B)

COND B RISE FALL(IOPATH A)

COND DEFAULT)

)

······

库SAIF文件中包含了SDPD信息。有了库SAIF文件,仿真时,仿真器会根据库中的SDPD信息,监视节点的开关行为。

②Gate Backward SAIF文件的生成

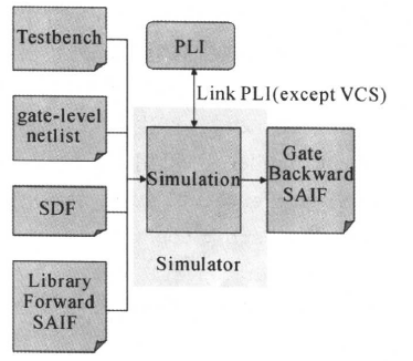

下面是产生gate backward SAIF文件的流程:

从上图中我们可以看到,产生gate backward SAIF需要testbench测试平台、门级网表、标准延时格式(standard delay format)文件SDF、库SAIF文件。其中SDF文件反标了门级网表中的RC延时参数等,可以更为准确地得到线网的延时。

testbench的示例内容如下所示:

module testbench;

top instl (a, b, c,s);

initial

$sdf_annotate("my.sdf",dut)

initial begin

$read_lib_saif ("mylib.saif");

$set_toggle_region (u1);

$toggle_start;

#120 a=0;

#STEP in_ a=temp_in_a;

······

$toggle_stop;

$toggle-report("gate.saif",1.0e-9,"top")

end

endmodule//testbench

testbench测试平台主要是调用门级网表、SDF文件、库SAIF文件。testbench中,用$sdf_annotate("my. sdf", dut)命令作SDF标记,以保证时序的正确性,从而得到正确的翻转数目。$ read_lib_saif ("mylib. saif")命令读取库SAIF文件中的SDPD信息。仿真器只监视在SAIF文件里列出的SDPD开关行为。$ set_toggle_region (u1)命令选择要监视的模块。$ toggle_start和$toggle_stop命令控制开始和结束时间。$ toggle_report("gate. saif",1. 0e-9, "top")命令把SAIF输出到指定的文件。

万事俱备,只欠仿真,接下来就是使用VCS进行仿真了:

vcs -R top.v testbench. v

注意,这里的仿真是对门级网表的仿真,也就是说这里的top.v是门级网表。产生的示例gate forward SAIF文件的部分内容如下所示:

(SAIFILE

(SAIFVERSION "2 .0")

(DIRECTION "backward")

(DESIGN)

(DATE "Mon May 17 02:33:48 2006")

(VENDOR "Synopsys,Inc")

(PROGRAM_NAME "VCS-Scirocco-MX Power Compiler")

(VERSION "1 .0")

(DIVIDER / )

(TIMESCALE 1 ns)

(DURATION 10000.00)

(INSTANCE tb

(INSTANCE top

(NET

(z\3\

(T0 6488) (T1 3493) (TX 18)

(TC 26) (IG 0)

)

······

(z\32\

(T0 6488) (T1 3493) (TX 18)

(TC 26)(IG 0)

)

······

)

(INSTANCE U3

(PORT

(Y

(TO 4989) (T1 5005) (TX 6)

(COND((D1 * !DO)|(! D1*D0)) (RISE)

(IOPATH S (TC 22 )(IG 0)

)

COND((D1*!DO)}(!D1,DO))

( IOPATH S (TC 21)(IG 0) (FALL)

)

COND DEFAULT (TC 0)(IG 0)

)

······

Gate Backward SAIF文件是通过对门级网表进行仿真所得到的。如果设计很大,仿真需要的时间很长。好处是精确度很高。VCS所产生的Gate Backward SAIF文件中包含了一些或所有连线的开关行为和单元的开关行为。这些开关行为分别以上升和下降表示,与状态和路径有关。用这个信息可以进行精确的功耗分析。

③功耗分析

有了门级网表、gate backward SAIF文件和SDF文件,就可以在power compiler中进行功耗分析了,分析功耗的流程图如下所示:

对应的一个示例脚本文件如下所示:

set target_library mylib.db

set link_library " * $target_library"

read_verilog mynetlist.v

current_design top

link

read_read_parasitics top.spef

read_ saif -input mygate. saif -inst tb/top

report_power

上面的流程和脚本适用于后版图(post-layout)的设计,spef文件在做完版图后产生。使用寄生参数文件,提高了功耗分析的精确度。如果是前版图( pre-layout)的设计,没有寄生参数文件,连线的RC参数使用工艺库里的线负载模型。

最后总结一下,这里分析功耗流程为:

power compiler 产生库SAIF文件——》VCS产生gate backward SAIF文件——》power compiler进行功耗分析。

(5)VCD转SAIF分析法

前介绍了使用SAIF文件分析功耗的方法,这个方法都是通过VCS仿真得到相应的SAIF文件,然后进行功耗分析。下面我们介绍使用VCD文件转换成SAIF文件的方法,然后进行功耗分析。

①VCD文件的产生

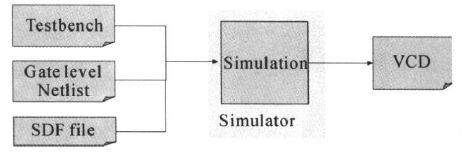

首先,我们在进行仿真的时候,需要通过在testbench中加入相关的系统函数,产生相应的VCD文件(和SDF文件),流程示意图如下所示:

相应的一个示例testbench如下所示:

module testbench;

······

initial

$sdf_annotate("my.sdf",dut)

initial begin

$dumpfile("vcd.dump");

$dumpvars;

······

endmodule

然后使用下面命令进行仿真:

vcs -R dut.v testbench.v +delay_mode_path

完成仿真之后,就可以得到VCD文件了。

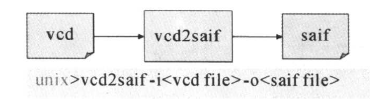

②VCD文件转换成SAIF文件

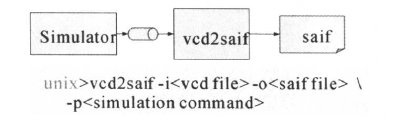

仿真时产生的VCD文件也包含了设计中节点和连线的开关行为。在Power Compiler中,可以使用程序vcd2saif可以把VCD文件转化为SAIF文件,如下图所示:

vcd2saif是在UNIX命令行使用的一个程序。vcd2saif程序也可以把VPD文件(二进制格式的VCD文件)转化为SAIF格式的文件。如果设计很大,仿真的时间长,vcd2saif程序可以用管道传递的方式把VCD转化为SAIF文件。这时vcd文件不存放在文件里,vcd通过先入先出(First-In First-()nt,简称FIFO把数据传给vcd2saif程序,然后产生SAIF文件。转换的SAIF文件里没有SDPD的信息。如下图所示:

有了SAIF文件之后,我们就可以像前面那样使用SAIF文件进行功耗分析了,至于是版图前的功耗分析还是版图后的功耗分析,取决于功耗分析时有没有与版图中有关的信息,比如是SPEF文件。因此流程为:

VCS产生VCD文件——》power compiler 将VCD文件转换为SAIF文件——》power compiler 进行分析功耗

最后,我们来说一下这里使用vcd2saif程序的好处,主要有下面三点:

1. VCD产生的速度快;

2. VCD是IEEE的标准并且适用于进行后仿真;

3. 转换的过程快。

=============================================================================================

我们已经介绍四种为设计产生开关行为的方法,分别是直接设置翻转率、RTL backward SAIF文件、gate back SAIF文件和VCD转SAIF文件;这些方法可以混合使用,其优先次序如下所示:

用read_ saif命令标记的开关行为优先级最高;用set_switching_activity命令设置的开关行为优先级次之;优先级最低的是用默认的变量power_default_toggle_rate指定的翻转率。

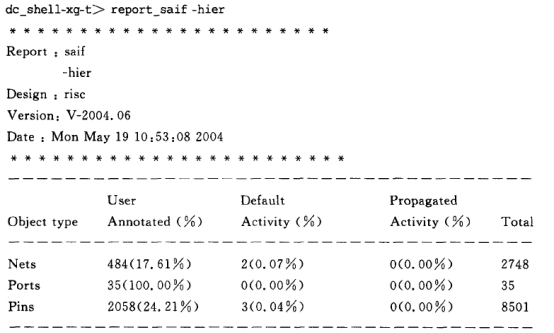

开关行为可以被清除,使用“reset_switching_activity”命令可以清除所有被标记的翻转率和通过传输得到的翻转率。用report_saif可以显示读入saif文件后设计中的开关行为信息。一个完整的SAIF文件,"user annotated”应该是100%。如果SAIF不完整,那么默认的翻转率将附加到输入端和黑盒子的输出端。翻转率通过零延迟仿真传输下去,这样就可以计算出设计的功耗。

使用report_saif命令的一个例子如下:

与开关行为有关的命令有:

merge_saif #合并SAIF文件

read_sai f #读backward SAIF文件

report_saif #报告开关行为的信息

rtl2saif #产生RTL forward SAIF文件

write_ saif #写出一个backward SAIF文件

lib2saif #产生library forward SAIF文件

propagate_switching_activity #传输功耗清除

reset_switching_activity #清除开关行为和/或翻转率

set_switching_activity #在指定的物体上设置开关行为

(6)功耗分析报告

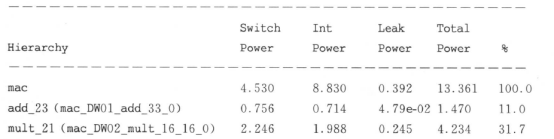

我们是通过分析功耗报告(report_power命令产生)来查看设计功耗的,一个功耗报告的示例部分内容如下所示:

Cell Internal Power=883.0439 mW(66%)

Net Switching Power=453.0173 mW(34%)

Total Dynamic Power=1 .3361 W(100%)

Cell Leakage Power = 391.5133 nW

其中第一项为内部短路功耗,第二项为开关功耗,合起来为动态功耗;最后一项为静态功耗,也就是泄漏功耗。如果要报告设计中每个模块和单元的功耗,在report_power命令后加选项 -hier,例如: report_power -hier,产生的报告如下所示:

基于EDA工具——power compiler 的功耗分析就记到这里。

(数字IC)低功耗设计入门(二)——功耗的分析的更多相关文章

- (数字IC)低功耗设计入门(一)——低功耗设计目的与功耗的类型

低功耗设计这个专题整理了好久,有一个月了,有图有证据: 然而最近一直有些烦心事.郁闷事,拖延了一下,虽然现在还是有点烦,但是还是先发表了吧.下面我们就来聊聊低功耗设计吧,由于文章比较长,因此我就不一次 ...

- (数字IC)低功耗设计入门(一)

低功耗设计这个专题整理了好久,有一个月了,有图有证据: 然而最近一直有些烦心事.郁闷事,拖延了一下,虽然现在还是有点烦,但是还是先发表了吧.下面我们就来聊聊低功耗设计吧,由于文章比较长,因此我就不一次 ...

- (数字IC)低功耗设计入门(七)——门级电路低功耗设计优化(续)

前面讲解了门级功耗的优化方法,包括静动态和总体的功耗.现在来记录一下门级层次(有点书也说是在系统级)常用的一种低功耗方法--电源门控. ①电源门控概述与原理 电源门控是指芯片中某个区域的供电电源被关掉 ...

- (数字IC)低功耗设计入门(八)——物理级低功耗设计&to be continued?

前面学习了从系统级到门级的低功耗设计,现在简单地了解了一下物理级设计.由于物理级的低功耗设计与后端有关了,这里就不详细学习了.这里主要是学习了一些基本原则,在物理级,进行低功耗设计的基本原则是: ...

- (数字IC)低功耗设计入门(三)——系统与架构级

前面讲解了使用EDA工具(主要是power compiler)进行功耗分析的流程,这里我们将介绍在数字IC中进行低功耗设计的方法,同时也结合EDA工具(主要是Design Compiler)如何实现. ...

- (数字IC)低功耗设计入门(四)——RTL级低功耗设计

二.RTL级低功耗设计 前面介绍了系统级的低功耗设计,换句话说就是在系统级降低功耗可以考虑的方面.系统级的低功耗设计,主要是由系统级设计.具有丰富经验的人员实现,虽然还轮不到我们设计,我们了解一下还是 ...

- (数字IC)低功耗设计入门(五)——RTL级低功耗设计(续)

二.RTL级低功耗设计(续) 前面一篇博文我记录了操作数隔离等低功耗设计,这里就主要介绍一下使用门控时钟进行低功耗设计. (4)门控时钟 门控时钟在我的第一篇博客中有简单的描述,这里就进行比较详细的描 ...

- (数字IC)低功耗设计入门(六)——门级电路低功耗设计优化

三.门级电路低功耗设计优化 (1)门级电路的功耗优化综述 门级电路的功耗优化(Gate Level Power Optimization,简称GLPO)是从已经映射的门级网表开始,对设计进行功耗的优化 ...

- VerilogHDL概述与数字IC设计流程学习笔记

一.HDL的概念和特征 HDL,Hard Discrimination Language的缩写,翻译过来就是硬件描述语言.那么什么是硬件描述语言呢?为什么不叫硬件设计语言呢?硬件描述语言,顾名思义就是 ...

随机推荐

- MySQL学习笔记(四)—存储过程

一.概述 存储过程是数据库定义的一些SQL语句的集合,然后直接调用这些存储过程和函数来执行已经定义好的SQL语句.存储过程可以避免开发人员重复的编写相同的SQL语句,而且存储过程是在MySq ...

- JavaWeb总结(八)—EL表达式

一.EL表达式简介 EL全名Expression Language.主要有以下作用. 1.获取数据 EL表达式主要用于替换JSP页面的脚本表达式,以及各种类型的Web域中检索Java对象.获取数据.( ...

- 通过Elasticsearch使用的你的数据

Elasticsearch 系列导航 elasticsearch 与 elasticsearch-head 的安装 ElasticSearch Index API && Mapping ...

- Java事物基础总结

1.什么是事物? 事物是逻辑上的的一种操作,这个操作过程中的每一个元素要么全部成功,要么全部失败.例如,银行转账过程视为一个事物,转出过程和转入过程要求全部成功或全部失败,通过提交事物或者回滚事物实现 ...

- 关于下拉框列表不可选择相同值的设置一:当前DOM不可选

<!DOCTYPE html><html><head lang="en"> <meta charset="UTF-8" ...

- ElasticSearch集群安装配置

1. 环境说明 Cent OS 7 jdk-8u121-linux-x64.tar.gz elasticsearch-5.2.1.zip 2. 系统环境配置 新建进程用户 修改File Descrip ...

- 4 安装MPush

cnblogs-DOC 1.服务器环境 2.安装Redis3.安装Zookeeper4.安装MPush5.安装Alloc服务6.完整测试7.常见问题 一.Linux安装Mpush [root@loca ...

- 深入理解MVC

首先我们来看看MVC架构的示意图: 和访问者交互的是控制层(Controller层),控制器(controller)是同类交互的集合,每一个交互的操作,都对应了一个动作(act ...

- 【转】JDBC学习笔记(4)——PreparedStatement的使用

转自:http://www.cnblogs.com/ysw-go/ PreparedStatement public interface PreparedStatement extends State ...

- 【转载】google搜索从入门到精通

原文地址:http://www.cnblogs.com/helloIT/articles/5095668.html /***************************************** ...