[原创][FPGA][IP-Core]altlvds_tx & altlvds_rx

1. 概述

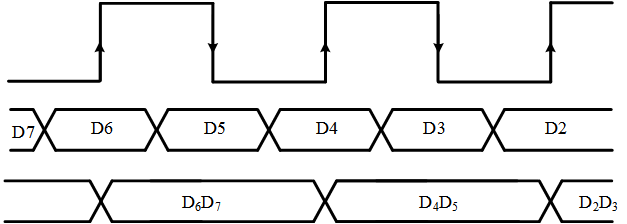

Alter公司的QuartusII软件提供了LVDS发送和接收的IP核供我们使用,其在本质上可以理解为并行-串行数据的转换器。其在官方文档(见附件)上也这样说过。其中的应用场景有告诉AD/DA的数据传输等。

那在此我们就针对这一IP核进行了解、熟悉和测试。首先我们来对差分发送端进行学习。

2. altlvds_tx

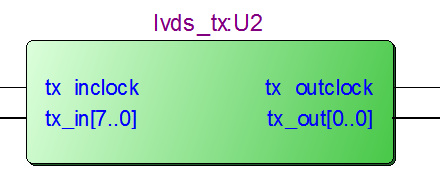

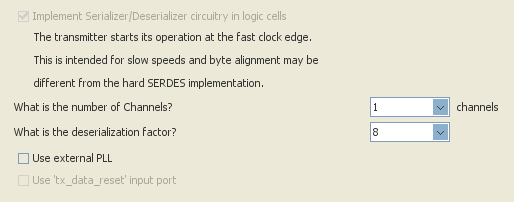

图2.1所示为一个简单的差分发送端,其有两个输入,一个为输入时钟,一个为输入数据。两个输出为穿行输出数据和输出时钟。

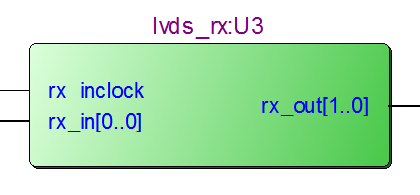

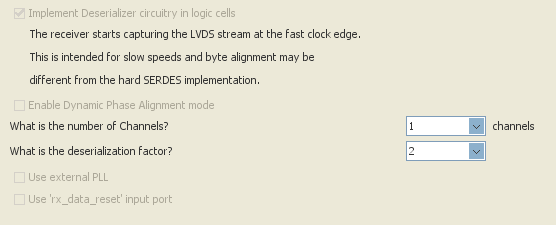

3. altlvds_rx

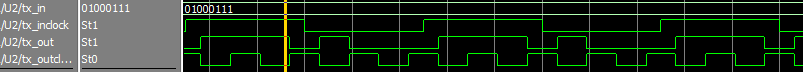

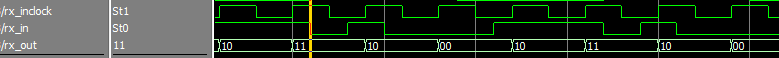

图3.3 仿真波形图结果

.png)

[原创][FPGA][IP-Core]altlvds_tx & altlvds_rx的更多相关文章

- Modelsim独立仿真Vivado Clocking Wizard IP Core

工欲善其事,必先利其器.在使用Vivado自带的仿真软件仿真的时候,相对于更优秀的仿真工具Modelsim,效率低了很多,为了更高效的开发,我尝试着用Vivado级联Modelsim仿真,但是级联后还 ...

- IP Core 分类

IP(Intelligent Property)核是具有知识产权核的集成电路芯核总称,是经过反复验证过的.具有特定功能的宏模块,与芯片制造工艺无关,可以移植到不同的半导体工艺中.到了SOC阶段,IP核 ...

- Vivado 2017封装自定义IP Core

使用Vivado2017.3自定义IP Core.通常情况下,我们做设计采用模块化设计,对于已经设计好的一部分模块功能,就可以直接拿来调用,IP Core就是这样来的,一般来说我们看不到IP Core ...

- 在EDK里面添加ISE IP core的方法

(1)在ISE下,使用core generator,可以得到xilinx的IP的*.v和*.ngc 文件,将这两个文件拷贝出来: (2)在EDK下使用“Create or Import Periphe ...

- 使用xilinx ip core FIFO First- World First-Through (FWFT)模式的注意事项

也许很多人知道xilinx ip core 中的fifo可以配成standard 模式和FWFT模式,并知道两者的区别是:standard模式下,当rd为高时,fifo会延时一个时钟输出数据(时序逻辑 ...

- 阅读 RAM-Based Shift Register(ALTSHIFT_TAPS) IP Core User Guide

阅读 RAM-Based Shift Register(ALTSHIFT_TAPS) IP Core User Guide 说明:本文档自带测试工程: DE_ALTSHIFT_TAPS.zip 1.支 ...

- Modelsim SE 仿真 ALTERA FPGA IP

Modelsim SE 仿真 ALTERA FPGA IP 最近,有几个朋友问过我是不是有新版本的Modelsim altera,其原因是 Qii 升级为新版本的,但是没配套的modelsim,没办法 ...

- H.265 Video Encoder IP Core

复制: 开源H.265硬件视频编码器H.265 Video Encoder IP Core是开源的H.265硬件视频编码器,实现了H.265(或叫HEVC)的大部分功能. 它由复旦大学专用集成电路与系 ...

- Xilinx 7系列例化MIG IP core DDR3读写

昨晚找了一下,发现DDR3读写在工程上多是通过例化MIG,调用生成IPcore的HDL Functional Model.我说嘛,自己哪能写出那么繁琐的,不过DDR读写数据可以用到状态机,后期再添砖加 ...

- ModelSim Simulation of RapidIO II IP Core Demonstration Testbench May Require ld_debug Command

Solution ID: fb83262Last Modified: May 17, 2013Product Category: Intellectual PropertyProduct Area: ...

随机推荐

- GoF23种设计模式之行为型模式之策略模式

传送门 ☞ 轮子的专栏 ☞ 转载请注明 ☞ http://blog.csdn.net/leverage_1229 1概述 定义一系列算法,把它们一个个都封装起来,并且让它们可以相互 ...

- Nordic Collegiate Programming Contest 2015 G. Goblin Garden Guards

In an unprecedented turn of events, goblins recently launched an invasion against the Nedewsian city ...

- Monkeyrunner脚本的录制与回放

继上一篇monkeyrunner环境搭建:http://www.cnblogs.com/zh-ya-jing/p/4351245.html 之后,我们可以进一步学习monkeyrunner了. 我也是 ...

- HBase0.94.2-cdh4.2.0需求评估测试报告1.0之四

第二组:文件存储读过程记录 第一组:一个列,四个分区,随机ID 测试列和分区 测试程序或命令 导入文件大小(Mb) 导入文件个数(个) 是否触发flush事件(布尔) 是否触发compact事件(布尔 ...

- Jmeter Cluster

Jmeter 是开源软件,100%纯java应用程序,专门为负载测试和性能测试. Jmeter的特性包括: 1.负载测试和性能测试许多不同的服务器/协议类型: Web - HTTP, HTTPS SO ...

- hibernate悲观锁,乐观锁

业务逻辑的实现过程中,往往需要保证数据访问的排他性.因此,我们就需要通过一些机制来保证这些数据在某个操作过程中不会被外界修改,这样的机制,在这里,也就是所谓的“锁”,即给我们选定的目标数据上锁,使其无 ...

- 第002弹:Java 中的值传递和引用传递

在 Java 的代码开发过程中,为了尽可能提高方法的复用性,明确方法的作用,同时防止一个方法内部过于臃肿的问题,往往会创建许多方法,那么不可避免地会涉及到参数传递的问题.通常来说,我们将 Java 中 ...

- iOS学习笔记36-Masonry自动布局

一.Masonry介绍 之前我们在屏幕适配的章节中学习过AutoLayout的使用,但那都是在可视化界面上进行添加约束完成的,我们很多时候都需要在代码中使用AutoLayout约束,苹果也为我们提供了 ...

- 【Luogu】P3356火星探险问题(费用流)

题目链接 网络流一条边都不能多连?没道理呀? 不过单看这题的确是个sb题…… #include<cstdio> #include<algorithm> #include< ...

- gcd-模板+最小公倍数

#include<iostream> #include<cstdio> #include<algorithm> using namespace std; int G ...