[原创][FPGA][IP-Core]altlvds_tx & altlvds_rx

1. 概述

Alter公司的QuartusII软件提供了LVDS发送和接收的IP核供我们使用,其在本质上可以理解为并行-串行数据的转换器。其在官方文档(见附件)上也这样说过。其中的应用场景有告诉AD/DA的数据传输等。

那在此我们就针对这一IP核进行了解、熟悉和测试。首先我们来对差分发送端进行学习。

2. altlvds_tx

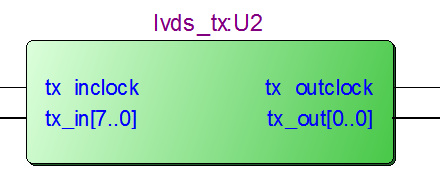

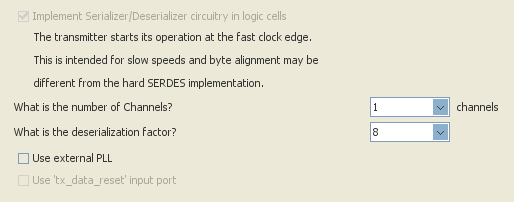

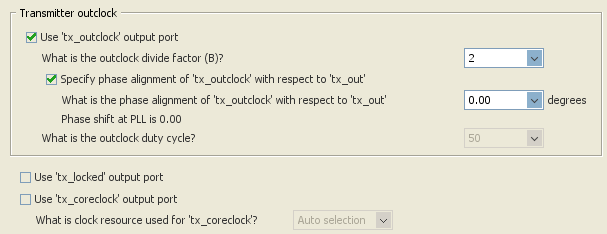

图2.1所示为一个简单的差分发送端,其有两个输入,一个为输入时钟,一个为输入数据。两个输出为穿行输出数据和输出时钟。

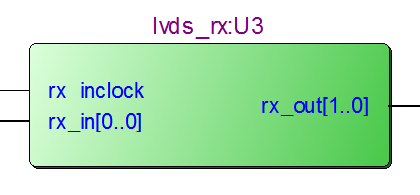

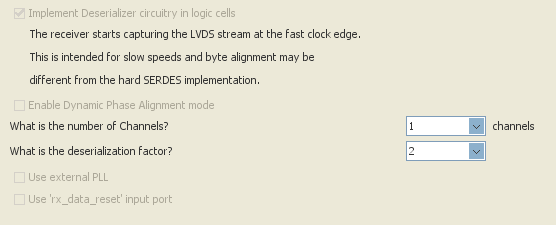

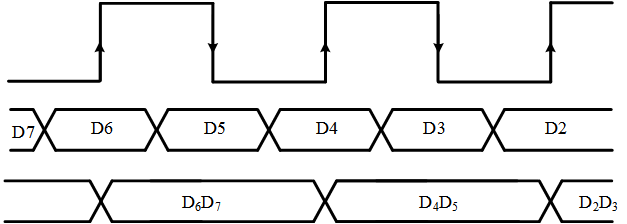

3. altlvds_rx

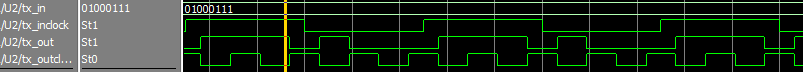

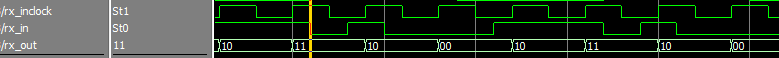

图3.3 仿真波形图结果

.png)

[原创][FPGA][IP-Core]altlvds_tx & altlvds_rx的更多相关文章

- Modelsim独立仿真Vivado Clocking Wizard IP Core

工欲善其事,必先利其器.在使用Vivado自带的仿真软件仿真的时候,相对于更优秀的仿真工具Modelsim,效率低了很多,为了更高效的开发,我尝试着用Vivado级联Modelsim仿真,但是级联后还 ...

- IP Core 分类

IP(Intelligent Property)核是具有知识产权核的集成电路芯核总称,是经过反复验证过的.具有特定功能的宏模块,与芯片制造工艺无关,可以移植到不同的半导体工艺中.到了SOC阶段,IP核 ...

- Vivado 2017封装自定义IP Core

使用Vivado2017.3自定义IP Core.通常情况下,我们做设计采用模块化设计,对于已经设计好的一部分模块功能,就可以直接拿来调用,IP Core就是这样来的,一般来说我们看不到IP Core ...

- 在EDK里面添加ISE IP core的方法

(1)在ISE下,使用core generator,可以得到xilinx的IP的*.v和*.ngc 文件,将这两个文件拷贝出来: (2)在EDK下使用“Create or Import Periphe ...

- 使用xilinx ip core FIFO First- World First-Through (FWFT)模式的注意事项

也许很多人知道xilinx ip core 中的fifo可以配成standard 模式和FWFT模式,并知道两者的区别是:standard模式下,当rd为高时,fifo会延时一个时钟输出数据(时序逻辑 ...

- 阅读 RAM-Based Shift Register(ALTSHIFT_TAPS) IP Core User Guide

阅读 RAM-Based Shift Register(ALTSHIFT_TAPS) IP Core User Guide 说明:本文档自带测试工程: DE_ALTSHIFT_TAPS.zip 1.支 ...

- Modelsim SE 仿真 ALTERA FPGA IP

Modelsim SE 仿真 ALTERA FPGA IP 最近,有几个朋友问过我是不是有新版本的Modelsim altera,其原因是 Qii 升级为新版本的,但是没配套的modelsim,没办法 ...

- H.265 Video Encoder IP Core

复制: 开源H.265硬件视频编码器H.265 Video Encoder IP Core是开源的H.265硬件视频编码器,实现了H.265(或叫HEVC)的大部分功能. 它由复旦大学专用集成电路与系 ...

- Xilinx 7系列例化MIG IP core DDR3读写

昨晚找了一下,发现DDR3读写在工程上多是通过例化MIG,调用生成IPcore的HDL Functional Model.我说嘛,自己哪能写出那么繁琐的,不过DDR读写数据可以用到状态机,后期再添砖加 ...

- ModelSim Simulation of RapidIO II IP Core Demonstration Testbench May Require ld_debug Command

Solution ID: fb83262Last Modified: May 17, 2013Product Category: Intellectual PropertyProduct Area: ...

随机推荐

- python导出开发环境

1.导出开发环境的依赖包 本地开发完后,再把代码给别人之前,需要 pip freeze > pip123.txt 2.其他环境安装依赖包 pip install -r pip123.txt 其他 ...

- 9-11.Yii2.0框架控制器分配视图并传参xss攻击脚本视图的过滤

目录 一维数组传参 新建控制器: 新建view模板 二维数组传参 新建控制器: 新建view模板 视图非法字符的过滤 新建控制器: 新建view模板 一维数组传参 新建控制器: D:\xampp\ht ...

- GoF23种设计模式之行为型模式之责任链模式

一.概述 使多个对象都有机会处理请求,从而避免请求的发送者和接收者之间的耦合关系.将这些对象连成一条链,并且沿着这条链传递请求,直到有一个对象处理它为止.其设计思想是:给对多个对象处理一个请求的机会, ...

- Tomcat Bug记录

1.问题:org.apache.tiles.request.render.CannotRenderException: ServletException including path '/WEB-IN ...

- hdu-2544 最短路(最短路)

Time limit1000 ms Memory limit32768 kB 在每年的校赛里,所有进入决赛的同学都会获得一件很漂亮的t-shirt.但是每当我们的工作人员把上百件的衣服从商店运回到 ...

- Mysql显示所有数据库

show databases; mysql> show databases; +--------------------+ | Database | +--------------------+ ...

- Java技术——多态的实现原理

.方法表与方法调用 如有类定义 Person, Girl, Boy class Person { public String toString(){ return "I'm a person ...

- windows基本DOS命令

基本命令 dir : 列出当前目录下的文件以及文件夹,后面可以接其他路径 md : 创建目录(mkdir),一次创建多级目录,mkdir a\b\c rd : 删除目录,删除非空目录rd /s(删除最 ...

- 深入了解ASO

ASO对于一些人来说可能很陌生,很多人都听说过SEO,没有听说过ASO(我也是最近才知道这个领域),因为这是一个数字营销的一个新领域.ASO(App Store Optimization)是为了让自己 ...

- 老男孩全栈python学习进程表

老男孩Python高级全栈开发工程师-1 0001.开学典礼_ALEX简介 00:55:53 ☆ 0002.职业生涯_来培训的目的 01:12:29 ☆ 0003.课程目标 00:29: ...