如何确定FPGA电路中DDR4的Speed bin 是否兼容?

原创 by DeeZeng

实际工作中,经常会碰到因为DDR3/4 或其他料件换料了,需要判断FPGA工程中IP设置需要重新改动,或是兼容直接换料就可行。

我个人倾向用 跑的速度的 speed bin 去设定,然后确认speed bin 是兼容的。

比如 DDR4 将换成2666 的chip, 但Arria 10 工程 只跑2133 或2400 的速度, 那我就按照2133 或 2400 的 speed bin 来设置。

但会需要确认 2133 、2400 speed bin 是被 2666 的chip 向下兼容的。

怎样查看Speed Bin 是否兼容呢?

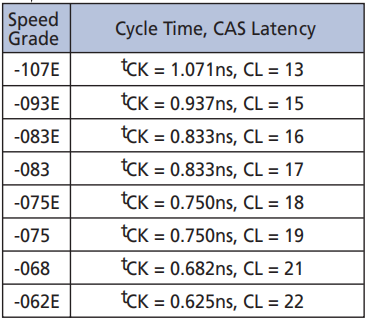

很简单, DDR4的datasheet中就有提,比如 Micron的这颗(随便找的一颗)

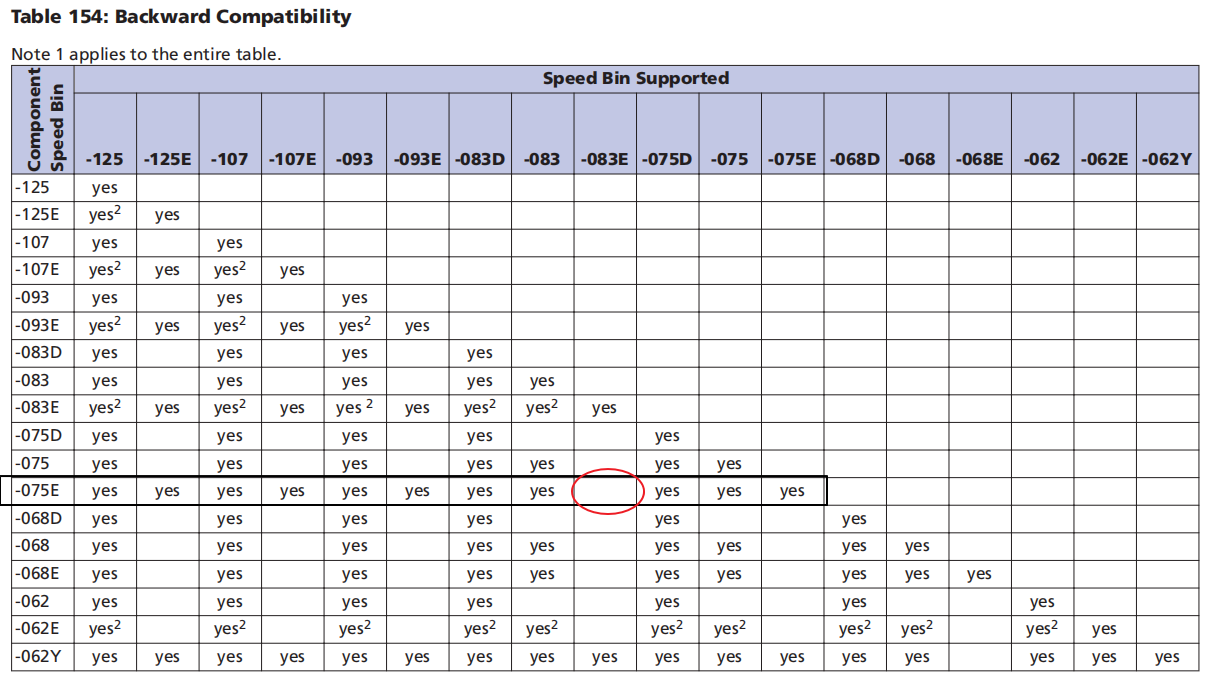

比如 我们选定 2666 的 component speed bin 是 075E。 那考虑兼容的时候 就会看到 不兼容 2400的 083E

这样设定IP的时候 我们就可以设定 2133 的093 或 093E speed bin 或 2400的 083 speed bin,而2400的083E speed bin 是不行的。

为什么会这样呢? 那有些参数是随 clock rate 变化的比如多少UI 是没影响。 但tRCD,tRP则是另外的情况,当然我们直接看兼容表就行了。

从兼容表也可以看出,并不是速度快就能直接替代速度慢的,有些参数还是不行的。 选替代料的时候需要注意一下。

是不是很简单,查看一下兼容表确认下就好!

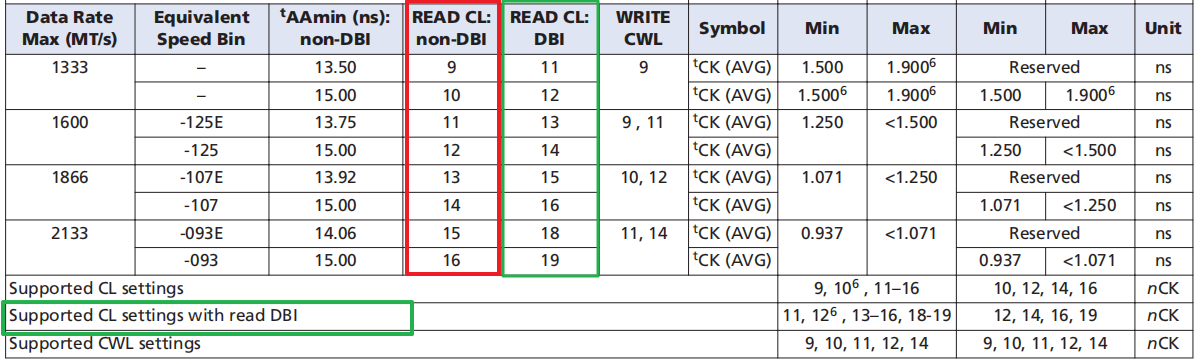

题外话:Data Bus Inversion(DBI) 这个功能可以在IP 中使能与否。

打开它可以让DQ IO 翻转更少,降低功耗。但它同时会增加latency(毕竟要多出一些判断来确定DQ 如何翻转)

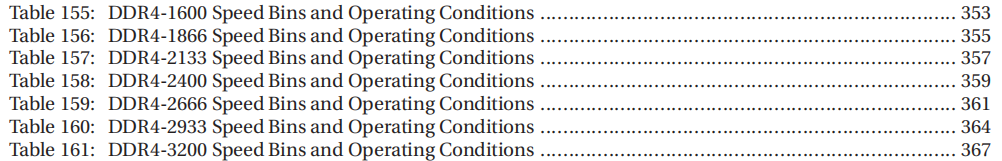

可以在 Speed Bin 中看到:

所以打开DBI 与否 对 CL 的设定是有影响的。

如何确定FPGA电路中DDR4的Speed bin 是否兼容?的更多相关文章

- 影响FPGA设计中时钟因素的探讨。。。转

http://www.fpga.com.cn/advance/skill/speed.htm http://www.fpga.com.cn/advance/skill/design_skill3.ht ...

- FPGA设计中的异步复位、同步释放思想

1.一个简单的异步复位例子: module test( input clk, input rst_n, input data_in, output reg out ); always@(posedge ...

- [专业名词·硬件] 1、等效串联电阻ESR概述及稳压电路中带有一定量ESR电容的好处

一.等效串联电阻ESR概述 ESR是Equivalent Series Resistance的缩写,即“等效串联电阻”.理想的电容自身不会有任何能量损失,但实际上,因为制造电容的材料有电阻,电 ...

- FPGA系统中DRAM,SRAM,SDRAM,FLASH 区别(转)

原文:http://hi.baidu.com/abners/item/a9042ef35d3f005bc8f337f5 一般来说这几种存储器是一个nios系统都具有的,sram的好处是接口简单,速度快 ...

- 基于FPGA的中值滤波算法实现

在这一篇开篇之前,我需要解决一个问题,上一篇我们实现了基于FPGA的均值滤波算法的实现,最后的显示效果图上发现有一些黑白色的斑点,我以为是椒盐噪声,然后在做基于FPGA的中值滤波算法的实验时,我发现黑 ...

- FPGA计算中定标与位扩展的实现

我不知道名字取对没有,在FPGA计算中有时往往需要在不溢出的情况下将数扩大,从而获得更好的计算精度. 比如.在一个8位宽的系统中,将x=0000_0010,算术左移m=5位之后得到xt=0100_00 ...

- 学习FPGA过程中的理论知识

学习FPGA,先要有数电知识,最好有点C语言,,学好硬件描述语言,verilog或者vhdl.在有这些基础上,做一些小的模块不断积累.这里不再赘述. 下面介绍一下关于FPGA学习过程中的一些理论知识. ...

- 硬件电路中VCC,VDD,VEE,VSS有什么区别

电路中GND和GROUND.VCC,VDD,VEE,VSS有什么区别 一.解释 DCpower一般是指带实际电压的源,其他的都是标号(在有些仿真软件中默认的把标号和源相连的)VDD:电源电压(单极器件 ...

- 电路中IC器件电压符号的解释

在电子芯片.运算处理器等集成电路行业中,存在多种电压.常用的的有:VDDQ->The supply voltage to output buffers of a memory chip 存储芯片 ...

随机推荐

- IDEA的参数配置

配置默认JDK 2.默认Project是没有JDK的,需要手动添加,然后才会有选项 关闭Intellij IDEA自动更新 文件编码设置 改快捷键,模板,注释,自动导包,创建web项目卡顿参数修改,代 ...

- 关于Jvm类加载机制,这一篇就够了

前言 一个月没更新了,这个月发生了太多的事情,导致更新的频率大大降低,不管怎样收拾心情,技术的研究不能落下! jvm作为每个java程序猿必须了解的知识,博主推荐一本书<深入理解Java虚拟机& ...

- 【Idea】JUnit单元测试%MODULE_WORKING_DIR%' does not exist

Idea执行单元测试时报错:上午9:35 Error running 'MobileMessageImplTest.java': Cannot start process, the working d ...

- 基于cxf开发的WebService

Node.jshttps://www.cnblogs.com/goldlong/p/8027997.htmlQQ音乐apihttps://juejin.im/post/5a35228e51882506 ...

- Programming In Lua 第十章

1,lua中的数据结构都是表来实现的.数组就是索引为数值的表. 2,矩阵就是二维数组,三角矩阵就是矩阵的一半. 3,稀疏矩阵问题: 4, 5, 6,

- HDU 6060:RXD and dividing(DFS)

题目链接 题意 给出n个点,要把除1以外的点分成k个集合,然后对于每个集合要和1这个点一起求一个最小生成树,然后问这k个最小生成树的最大总和是多少. 思路 因为每个集合都包含1这个点,因此对于每个点都 ...

- 研究Electron主进程、渲染进程、webview之间的通讯

背景 由于某个Electron应用,需要主进程.渲染进程.webview之间能够互相通讯. 不过因为Electron仅提供了主进程与渲染进程的通讯,没有渲染进程之间或渲染进程与webview之间通讯的 ...

- Spring Cloud Alibaba | 序言

目录 Spring Cloud Alibaba | 序言 1. Spring Cloud Alibaba是什么? 2. 主要功能 3. 组件 4. 版本说明 4.1 版本依赖关系 4.2 组件版本关系 ...

- C语言指针专题——序

看到好多的C语言初学者学到指针时,都觉得指针怎么那么难啊!我也想起了我当时学习指针时遇到的困难,确实很难!到底是教程写的不好呢,还是老师教的不好呢?我觉得都有. 网上搜索指针讲解的资料很多,我也看了不 ...

- P2822组合数问题

组合数问题(NOIP2016提高组Day2T1) Time Limit:1000MS Memory Limit:512000K [题目描述] 组合数表示的是从n个物品中选出m个物品的方案数.举个例子 ...